计算机硬件基础

CPU

时序电路(寄存器)+ 逻辑电路(CPU算数逻辑单元)构成CPU的电路系统。最终通过时钟系统来控制整个电路系统的运转。

:::info

CPU每秒处理20000亿个浮点数(双精度8Byte),但是内存每秒只能传输250亿个浮点数。因此要想CPU满负荷运行,内存每秒传输250亿个浮点数同时数据操作80次。现实情况是没有数据在每次加载时,需要操作80次。

CPU具有强大的数据处理能力,还需要内存宽度来平衡。

:::

GPU

GPU主要应用于图像渲染处理,有大量的核心支持数千个线程,用于大量的并行计算,将复杂的问题拆分,一次性解决。 :::info 对比CPU,CPU需要负责多个进程的上下文切换,开销很大,因此限制了支持的线程数量。而GPU可以说是简化版的CPU只负责相对简单的计算。 :::

I/O设备

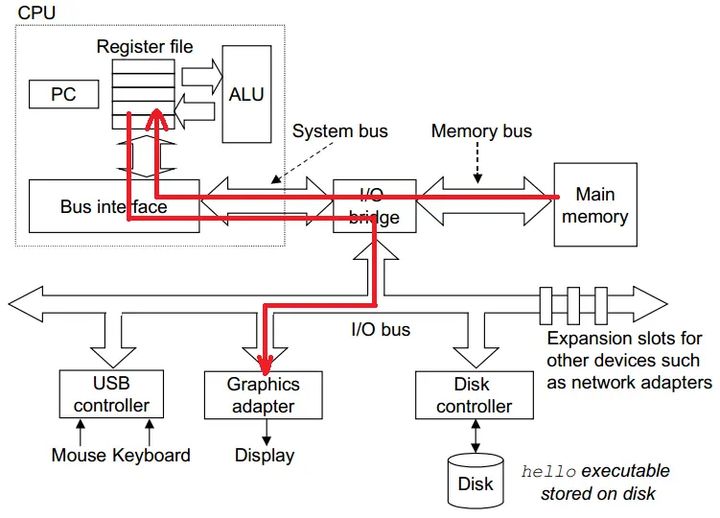

总线

信息传输的介质通道。

- 数据总线:数据传输的通道。决定数据交互一个数据传送量。

- 地址总线:地址总线的宽度决定CPU寻址能力。

控制总线:最简单的锁存器(门电路 )上有一根线,用来控制锁存器是输出数据还是写入数据。

I\O桥接控制芯片

总线数据传输的中间控制芯片,提供数据缓存、DMA功能。

主要是为了解决CPU读取不同存储器数据速度的差异。对慢速的设备,直接交给I\O桥接控制芯片去读取数据,使得CPU能够继续处理下一个指令,不必中断等待数据传回。

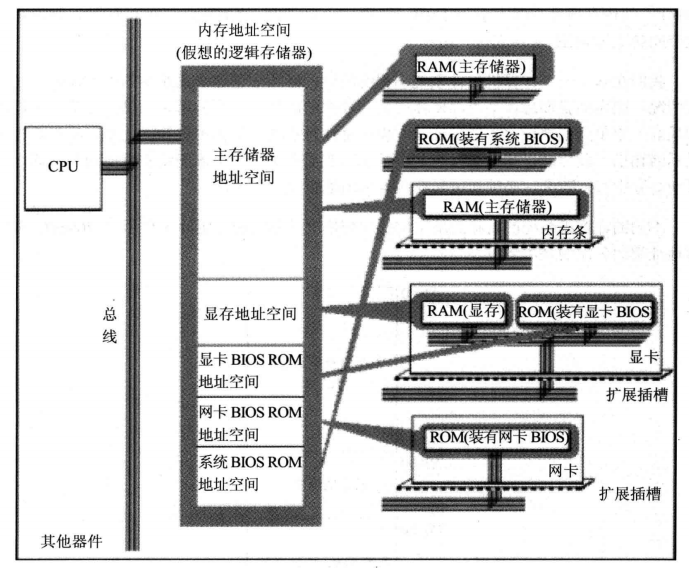

内存地址空间

- CPU会给计算机中所有存储设备,包括主存、显存、ROM,分配地址空间,以便CPU能够读写I\O设备中的数据。比如:CPU向内存中的8000H地址写入数据,会被写入到显存中显示。

- 如果地址总线的寻址空间有限,存储空间太大的主存其实也不是都可以物尽其用。

- 汇编语言是基于硬件系统编程,必须知道硬件系统的内存地址分配情况。

物理地址

- 8086CPU地址总线是20位,而寄存器是16位。

- 段地址 * 16 + 偏移地址 = 20位地址。通过地址加法器,传给20位地址总线。

地址计算分析段地址采用4位十六进制数表示,段地址 * 16相当于(二进制数表示的)段地址左移4位,换句话说20位地址中的前16位已经确定。如果偏移地址是0,则物理地址就是段地址的首地址。

偏移地址分析16位偏移地址决定段地址的寻址空间为64KB,所以一个段的最大长度为64KB。

段地址分析

- 段地址必须是16的倍数。

通过地址分段来寻址,对于数据、代码段读取来说,提供高效的数据检索和隔离。

寄存器

寄存器本质上就是触发器,既可以存储数据,也可以写数据。与主存最大的区别就是它与复杂的逻辑控制电路连接。

寄存器分类

因为不同寄存器与特定的逻辑电路相连接,可以实现特定的功能。

通用寄存器存放一些一般的数据,并可以拆分为两个独立的8位寄存器使用。

- AX(AH、AL)

- BX(BH、BL)

- CX(CH、CL)

- DX(DH、DL)

- 段寄存器存储内存各个不同分段的首地址。

- CS:代码段首地址。

- DS:数据段首地址。

- SS:栈段首地址。SS:SP始终指向栈顶。

- ES:扩展段寄存器。

- 指针寄存器

- IP:代码段偏移地址。IP寄存器会在CPU取到指令数据后,会根据数据大小自动增加。

- SP:栈段偏移地址。

问:地址总线宽度和寻址空间的关系?

- 假定地址总线位宽为10位,它可以控制2^10个锁存器(一个锁存器读写1bit),寻址空间就是2^10bit。一个地址,每次读写数据只需要1bit。

设定8个锁存器(1个内存单元)共享1个地址,那么寻址空间就是2^10Byte。一个地址,每次读写数据需要8bit,分别给8个锁存器。

问:存储单元为什么是8位?

英文文本信息(ASCII)的状态有100多,需要7位二进制表示100多个状态。换句话说存储单元位数至少要有7位。

- 7位作为存储单元,不方便表示、扩展。最终,可寻址存储单元就是8位。

问:计算机如何读取内存中数据和指令?

计算机通过地址总线、数据总线、控制总线的数据传输通道,发出一条指令给内存,这条指令就是三条总线上的电平表示。内存收到信号,通过地址总线上的信号找到内存单元。通过控制总线的信号知道是读还是写数据总线上的数据。问:计算机如何区分数据总线上的信息是表示数据还是指令?

- 内存中的代码和数据的存储没有任何区别,关键在于如何解释。

- 计算机通过存储16位地址的两个寄存器的类型,来区分数据和指令。CS:IP寄存器指向的内存空间就是指令。其他寄存器指向的内存空间就是数据。