存储技术

随机访问存储器

| SRAM | DRAM | |

|---|---|---|

| 构成 | 6晶体管/cell | 1电容+1晶体管/cell |

| tran/bit | 6 | 1 |

| 持久性 | 是,只要通电 | 否,需定期刷新 |

| 敏感度 | 否,抗干扰 | 是 |

| 速度 | 快 | 慢 |

| 成本 | 昂贵 | 较SRAM更便宜 |

| 应用 | cache | main memory |

非易失存储器

非易失存储器(Nonvolatile Memories),即read-only memory, ROM

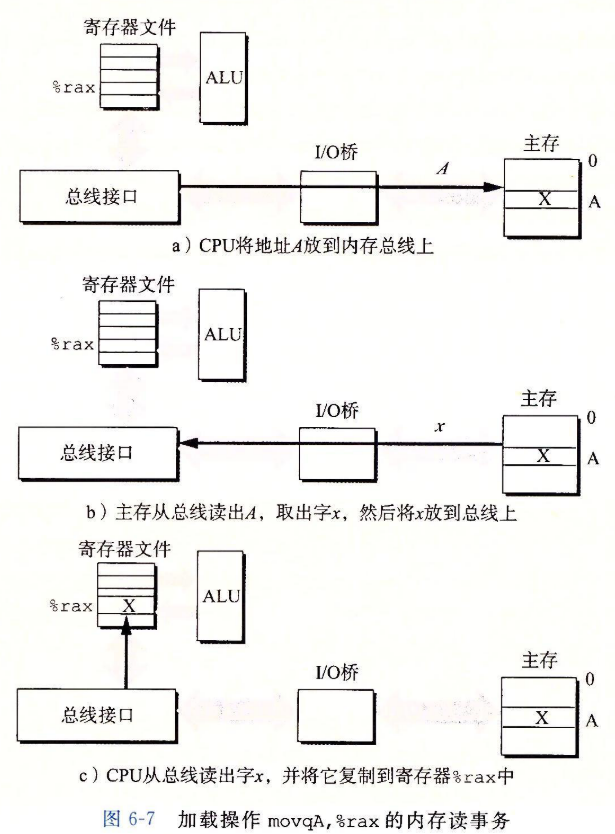

存储访问

数据流通过总线在CPU和DRAM主存之间来回

- 总线:一组并行导线,可携带地址,数据,控制信号,多个设备可共享总线

硬盘

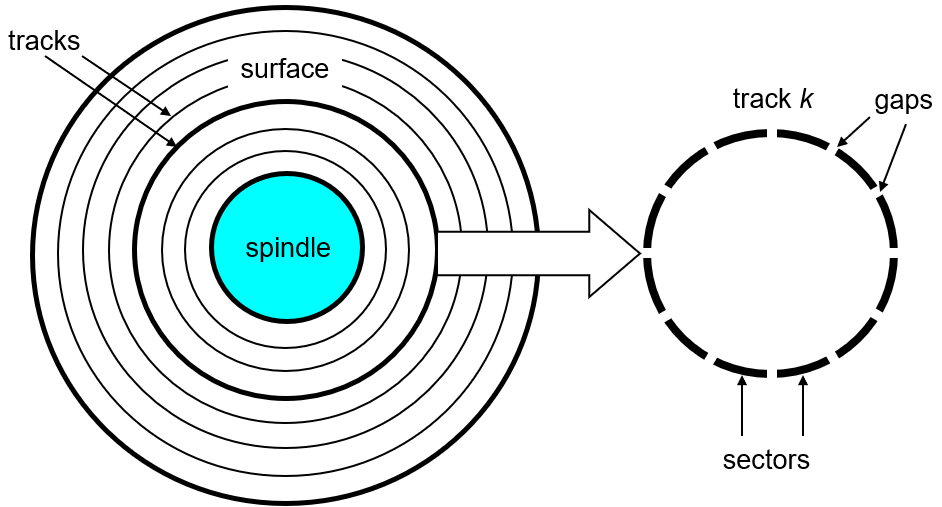

组成结构

|

- 由盘片(platters)组成,每个盘片由两面(surfaces)

- 每一个面上有数条磁道(trace)

- 每个磁道被间隙(gap)划分为扇区(sectors)

容量 = 磁盘数盘片数2磁道数扇区数 |  |

| —- | —- |

|

| —- | —- |

性能参数

| 寻道时间 | 磁头定位到某trace的用时 - 通常为9ms |

|---|---|

| 旋转延迟 |

抵达trace后,目标sector旋转到磁头下的时间 - |

| 传输时间 |

数据读写用时 - - 解释: - 1/RPM:每分钟转数的倒数,即1转/1磁道的用时 - 1/(sectors/track):即track/sectors,每个磁道平均扇区数 - 60secs/1min: 单位转换,化为每秒钟 |

| 总存取时间 |

Taccess = 寻道时间+旋转延迟+传输时间 |

| 举例 | 转速7,200 RPM,平均寻道时间9 ms,扇区/磁道 = 400,则 |

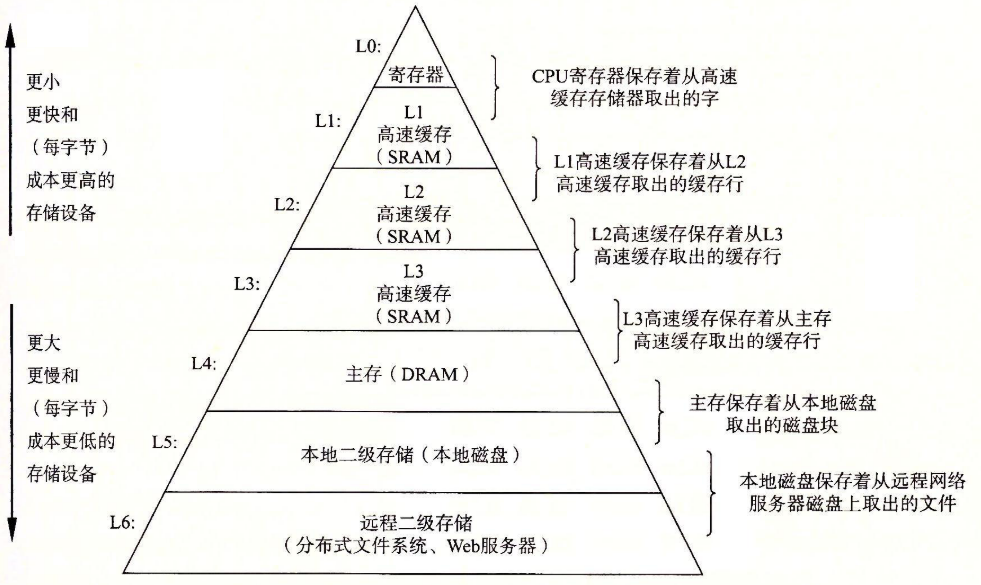

存储器层次结构

|

层次 | ⭐管理者 |

|---|---|---|

| register<->cache | compiler | |

| L1<->L2 | cache中的硬件 | |

| cache<->RAM | OS | |

| RAM<->disk | OS | |

| disk<->remote | 程序 |

cache

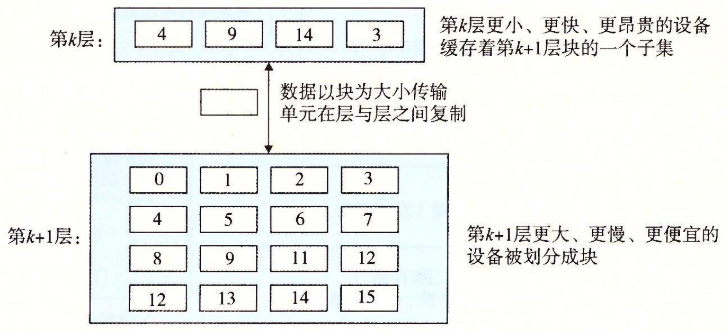

高速缓存原理:对于k,每个位于k层的存储设备(小,快)作为k+1层(大,慢)的cache

- 缓存命中(cache hit):当程序需要k+1层数据d时,它刚好被缓存在第k层中

- 缓存不命中(cache miss):

- 冷缓存/强制不命中/冷不命中(cold cache/compulsory miss/cold miss):第k层是空时导致

- 冲突不命中(conflict miss):由于算法/放置策略导致

- 容量不满足(capacity miss):当程序work set大于缓存大小

局部性原理

时间局部性

被引用过的存储器位置在未来可能会被多次引用(通常在循环中)

对于循环:更小的循环体和更多的循环迭代次数会产生更好的时间+空间局部性

分析以下伪代码的局部性

for (i = 0; i < M; i=i+1) {for (j = 0 ; j < N; j=j+1) {sum += data[i][j];}}

- sum具有时间局部性,每次循环都会被访问一次;作为标量没有空间局部性

- 对于循环,data[][]有较好的空间局部性,内层循环步长为1;但时间局部性较差,每个元素在函数中只会访问一次

存储器山

读吞吐量(read throughput):程序从存储系统中读数据的速率,当在s秒内读取n字节,则读吞吐量为n/s(B/s),单位通常为MB/s

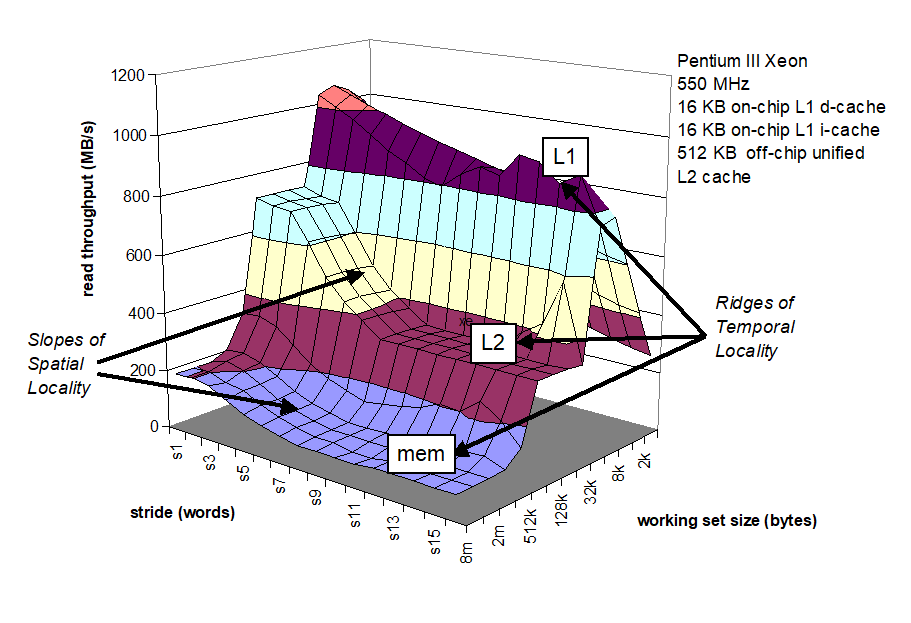

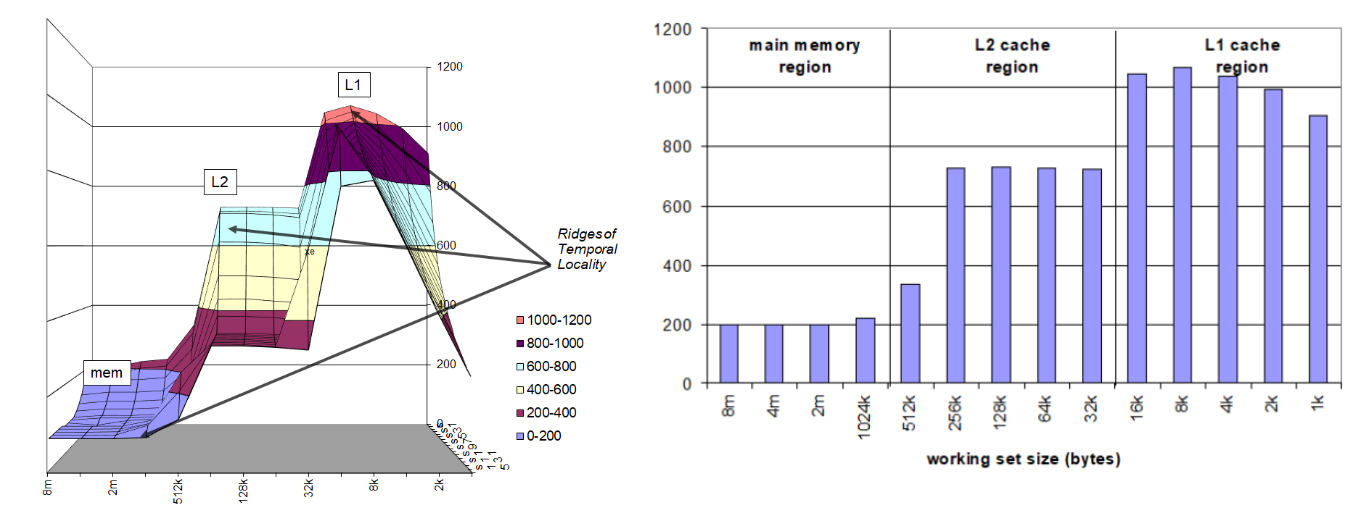

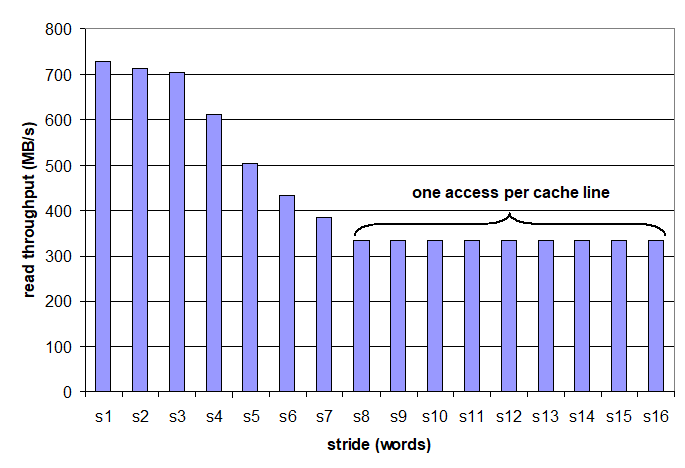

存储器山:编写程序,使用循环发出一系列读请求测试读吞吐量,程序中size表示工作集大小,stride为步长,以不同的size和stride测试读吞吐量,得到吞吐量与时间和空间局部性的二维函数—存储器山

- ⭐size越小,工作集越小,时间局部性越高

- ⭐**stride越小,跨度越小,空间局部性越高**

下图为奔腾处理器的存储器山

解读:

- 山脊(ridges):

- 图中三条山脊,实际上可见凸起为两条,对应size=16k和512k附近,表示工作集完全在L1和L2缓存中的吞吐量

- 当吞吐量恰好和L1或L2吻合,达到最大吞吐量

- 当>512k时,工作集开始存储在主存中,此时吞吐性能大幅下降

- 斜坡(slopes):

- 随着步长的增加,不同山脊的吞吐量下降,体现了空间局部性变差的影响

- 注意到即便在主存山脊中,吞吐量最高点也是最低点数倍,说明在时间局部性很差时,空间局部性也很重要

选择题知识点

- 关于引用局部性,下列正确的是②

①在compiler帮助下可精确预测未来的引用位置②是典型的程序特性③有数学证明

- 在存储器分层中,对应传输最大和最小数据块的层次为:

最大块:主存<->磁盘 最小块:CPU寄存器<->cache

- 未来的存储器分层发展趋势为:不会消失

给定代码

a = b;c = d;if (e == 1) return;

无论变量a,b,c,d,e的位置,都体现了引用(时间)局部性(重复引用)

⭐管理cache<->主存数据传输:OS

管理register<->cache:compiler

存储分级:利用了SRAM的快速和disk的大容量