1. 芯片

1.1 集成电路

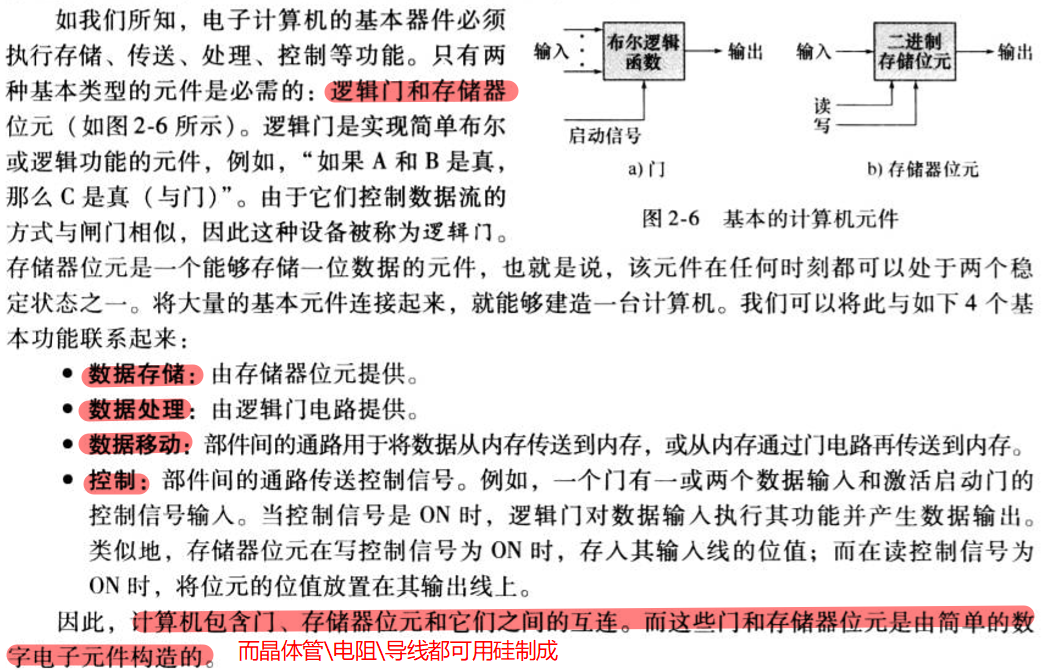

数字逻辑中的内容:利用输入电平的高低表示1与0,经过门电路的处理得到输出

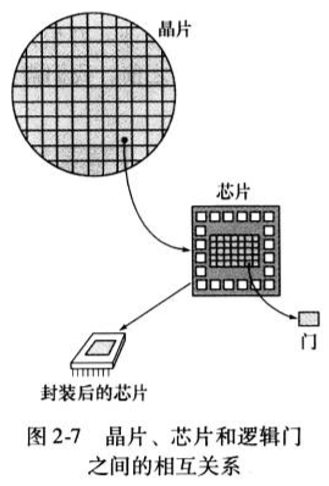

1.2 芯片

|

一块晶片上有大量芯片,每个芯片上有无数的门电路用于处理数据,位元用于存储数据 |

|---|---|

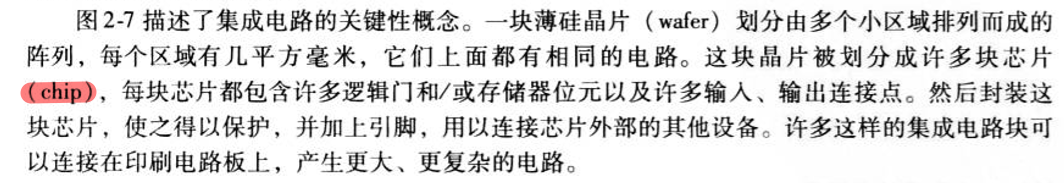

1.3 位元和DRAM

|  | 半导体存储器的基本结构是位元,可被多种技术实现,但都具有以下性质:

| 半导体存储器的基本结构是位元,可被多种技术实现,但都具有以下性质:

- 可稳定保持两种状态

- 可读/可写

位元普遍有三个功能端口:

- Select,用来选择位元

- Control,用来确定读写

- Data-In,接收1,0电信号

- Sense,输出当前状态

|

| :—-: | —- |

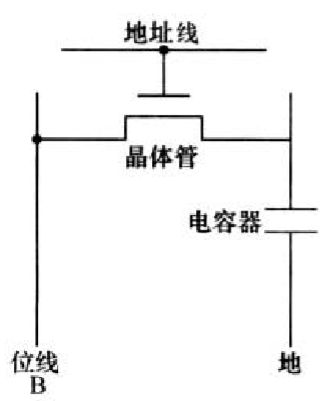

|  | 图示为一个储存1位信息的DRAM结构:

电容具有漏电的自然趋势,因此需要周期性充电保持存储状态—“动态”的来历

| 图示为一个储存1位信息的DRAM结构:

电容具有漏电的自然趋势,因此需要周期性充电保持存储状态—“动态”的来历

- 写操作:位线输入高低电压代表1和0,利用晶体管的特性,施加电压到地址线导通,电荷传输到电容器保存

- 读操作:施加电压到地址线,电容器放电,电荷被位线接收,经过放大器放大,对比参考值,确定位值是1还是0

|

1.4 芯片逻辑

一块RAM芯片内部位元的组织形式

参考链接: SDRAM基础知识

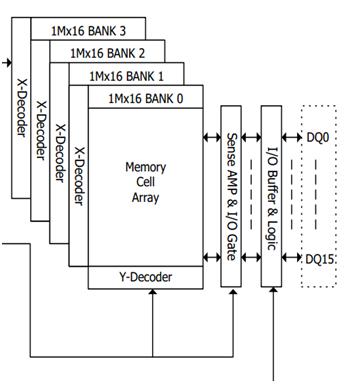

一般RAM芯片中阵列组织使用W×B表示:有W字长,每个字有B位宽,字的位宽决定半导体存储器一次读/写数据的位数

对于一个16Mb的DRAM,可以有多种内部阵列组织:

| 当阵列中位宽16bits(极端) | 1M×16b,1M个16位字 |

|---|---|

| 当阵列中位宽1bit(极端) | 16M×1b,16M个1位字 |

| 当采用4M×4(常见) | 4M×4b,4M个4位字 |

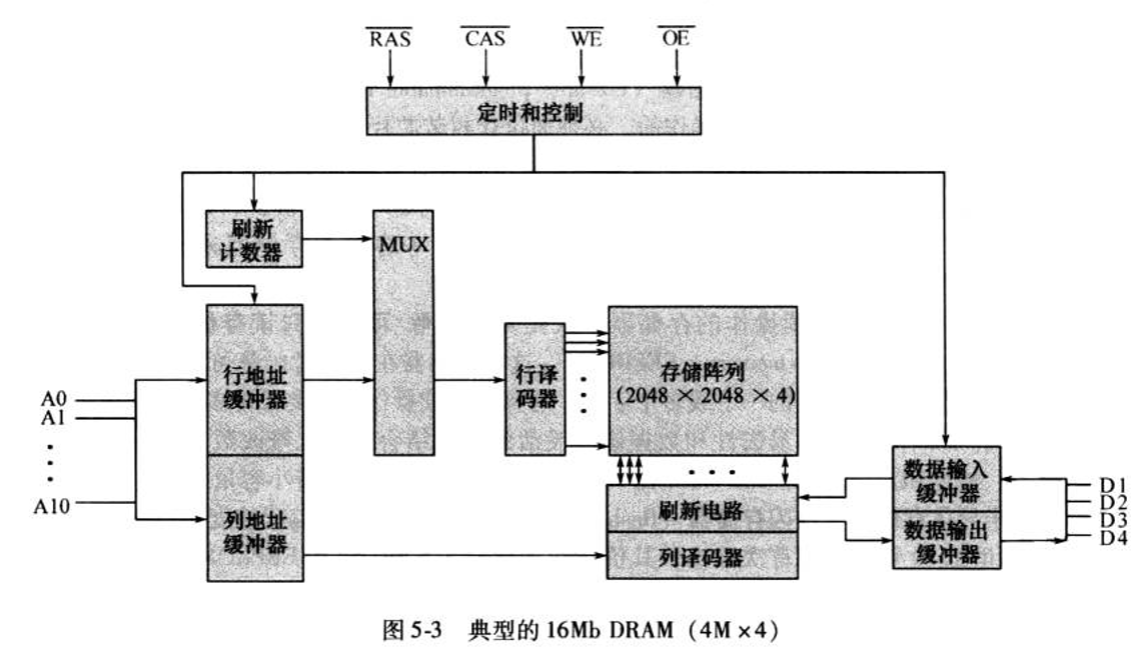

4M×4时DRAM内部结构如下:

放大存储阵列:

|  | 逻辑上:

| 逻辑上:

DRAM组织成4个2048×2048的方阵,阵列元素使用行和列控制线连接,行控制线连接行内每个位元的Select端口,列控制线连接Data-In/Sence端口

log2(4M)得到22,需要22根地址线,各取11位控制行与列,最终确定4位位元参与读/写:

- 写:每根位线的位驱动器根据对应数据线的值激活为1/0

- 读:每根位线的值经过放大器,传递到数据线

|

| :—-: | —- |

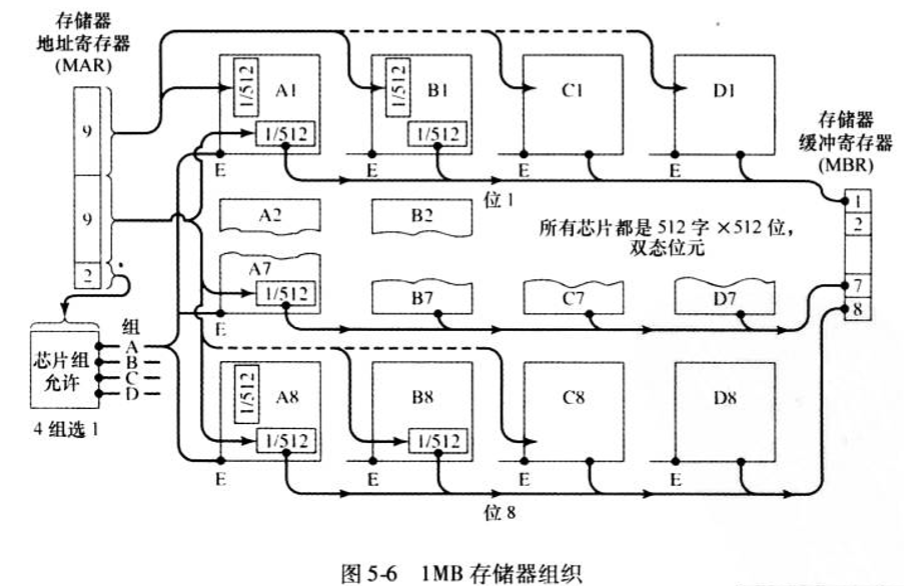

1.5 模块组织

多块RAM芯片组成一块存储器

对于更大容量的存储器,需要RAM芯片的阵列,此时需要保证位宽的一致,当RAM不满足存储器位宽要求,需要多个RAM组成一个模块达到位宽要求

当使用256K×2组成一个1M×8的存储器时,如图显示了如何使用4个芯片组成一个芯片模块

|

- 1M×8=4×(256K×2)×4 - 共需要16块RAM芯片组成存储器,其中4个芯片组成一个bank; - log2(256k)=18,行列控制位各9位 - 还需要2位进行组选择 |

|---|---|

2. 位宽与性能

| 总线宽度 | - 数据总线宽度对系统性能影响:数据总线越宽,一次传送的位数越多 - 地址总线宽度对系统容量影响:地址总线越宽,可访问单元越多 |

|---|---|

| CPU位宽 | 32位CPU和64位CPU的两大区别体现在此 - 数据总线:32位下,CPU在处理指令时只能处理最多32位,但64位下能够翻倍,大幅提升了对指令的执行能力,即前面得到字的位宽决定半导体存储器一次读/写数据的位数,在真实的计算机中,位宽由CPU决定 - 地址总线:32位下,最大寻址空间最大也只有2^32=4Gb,但64位下能有2^64b,更大的物理存储空间也提升了系统性能 |

3. 位宽与存储系统

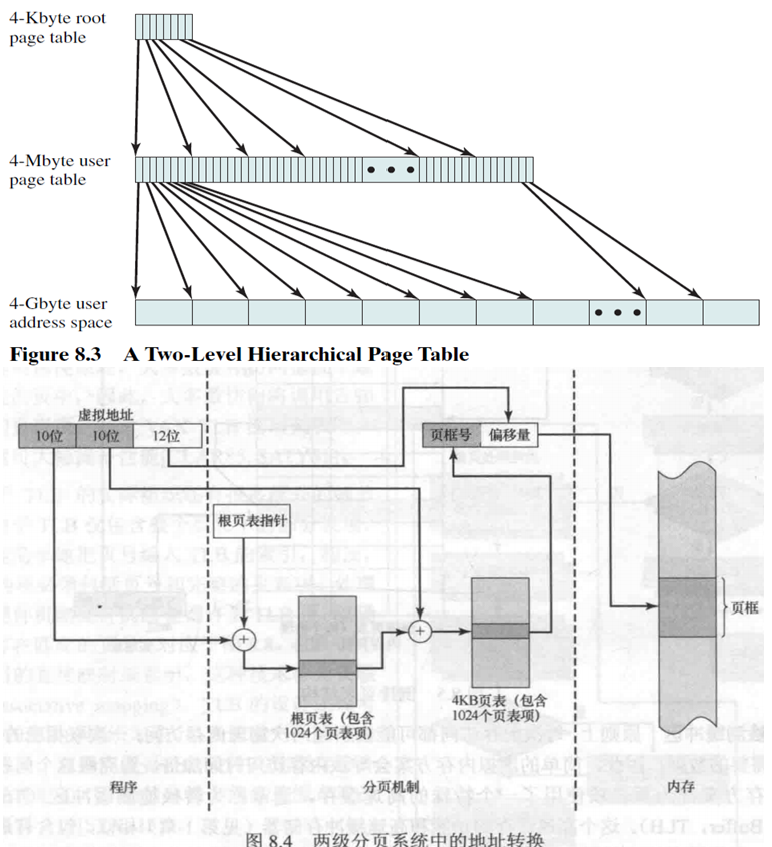

虚拟内存中的二级页表如下

|  |

|

- 32位二级页表结构(字节寻址):

假设页大小4k,虚存空间4G

则232/4k=220,页表个数为220,需要页表项也为220个

- 当每页都使用一个4bytes的页表项,则需要内存空间4*220=4M

- 对所有一级页表项占据的空间分页

- 222/4k=210,则需要210页,因为给定每页一个页表项

- 此时实存中保存了210个页表项,每个页表项4bytes,实际占用内存4k

|

| —- | —- |