1. ARM寄存器

1.1 综述

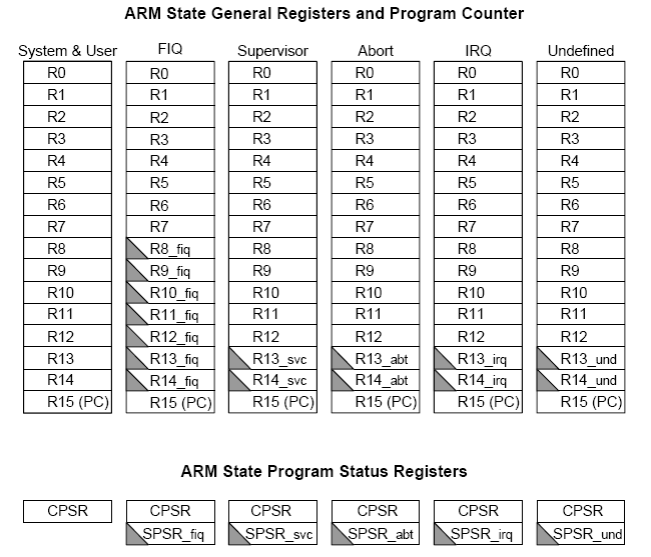

- ARM有37个寄存器(31个通用寄存器+6个状态寄存器)

寄存器不能全部同时看到,在不同的处理器状态和工作模式下,确定哪些寄存器对编程者可见

1.2 结构

1.2.1 寄存器个数

各模式公用:CPSR 1个

system/user:R0~R15 16个

FIQ影子寄存器:R8~R14 7个

SPSR_fiq 1个

Supervisor影子寄存器:R13~R14 2个

SPSR_svc 1个

Abort影子寄存器:R13~R14 2个

SPSR_abt 1个

IRQ影子寄存器:R13~R14 2个

SPSR_irq 1个

Udefine影子寄存器:R13~R14 2个

SPSR_und 1个

总计:1+16+3*5+5 = 371.3 通用寄存器

1.3.1 分类

没有对应影子寄存器:R0-R7

- 有对应影子寄存器:R8-R14

- 程序计数器:R15(PC)

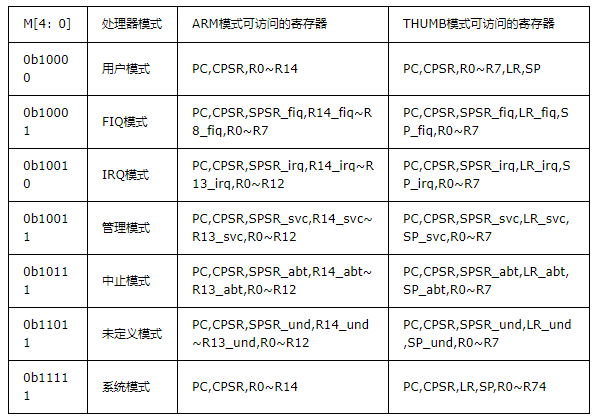

注 R0-R7为真正意义上的通用寄存器,没有任何特殊假设,功能等同,中断异常处理程序中需要对这几个寄存器保存 访问具体的物理处理器取决于当前的模式,依据规定的寄存器的名字进行操作 R8-R12有2组物理寄存器,一个是FIQ模式自己的,一个是其它模式的 R13-R14有6组物理寄存器,六个模式有各自的R13-R14(User和System共用一组) R13栈指针(SP指针)CPU在不同模式下会自动切换 R14链接寄存器(LR指针)有两个功能:保存调用子程序结束后需要返回的地址,发生异常时保存异常的返回地址 R15程序计数器(PC指针)指向正在取址的地址

使用寄存器最少的是用户模式

可使用的通用寄存器最少的模式是快速中断模式

1.3.2 特别注意

- R14(LR)在不同功能下的区别

调用子程序返回的地址为调用程序前的下一条指令地址,

而发生异常返回的地址会根据异常的类型,调用不同偏移的下一条指令地址 - R14(LR)在异常嵌套中存在风险

例如当连续发生两次IRQ中断时,会导致发生第二层中断时,R14_irq会保存第一层中断发生的下一条指令地址,而冲洗掉应该保存的用户模式下中断发生的下一条指令地址,导致程序跑飞回不到原来位置。

解决办法:(1)将用户模式下中断发生的下一条指令地址入栈,返回时从栈读地址返回

(2)使用不同的模式嵌套,如第一层中断用FIQ,第二层用IRQ,分别使用的是R14_fiq,

和R14_irq,不存在被冲洗的风险 R15(PC)的读取限制

从R15读取的值是处理器正在取址的地址,即当前正在执行指令地址加上8个字节(三级流水线)。而ARM状态下指令以字为单位(4字节),所以在ARM状态下R15的寄存器最低两位总是0。(Thumb状态最低总为0)1.4 对齐方式

ARM:字对齐

- Thumb:半字对齐

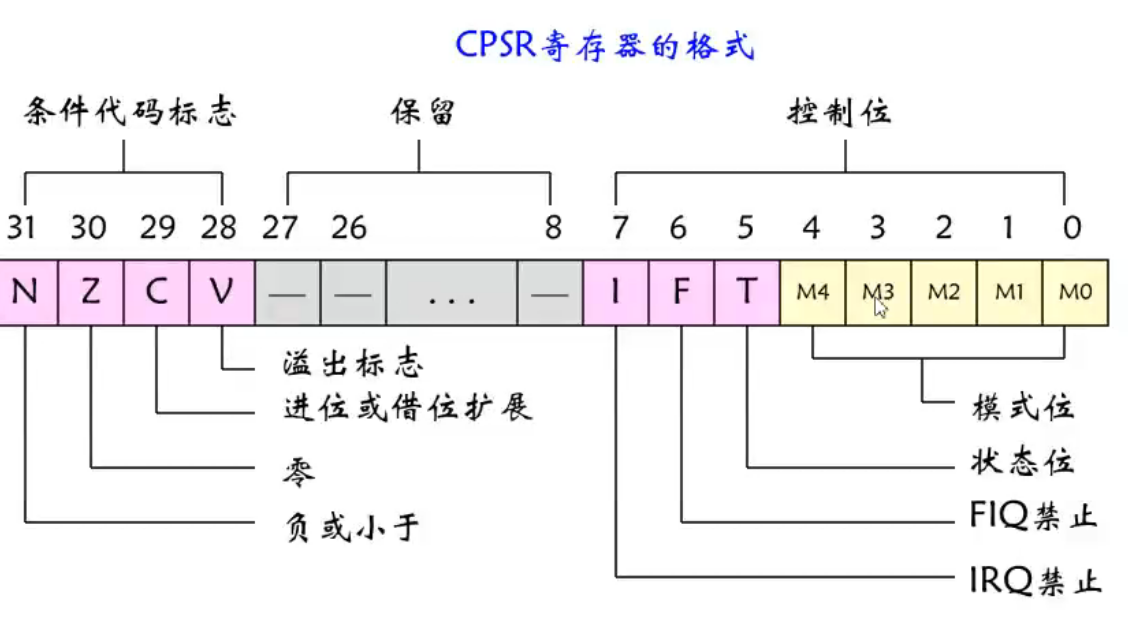

1.5 程序状态寄存器

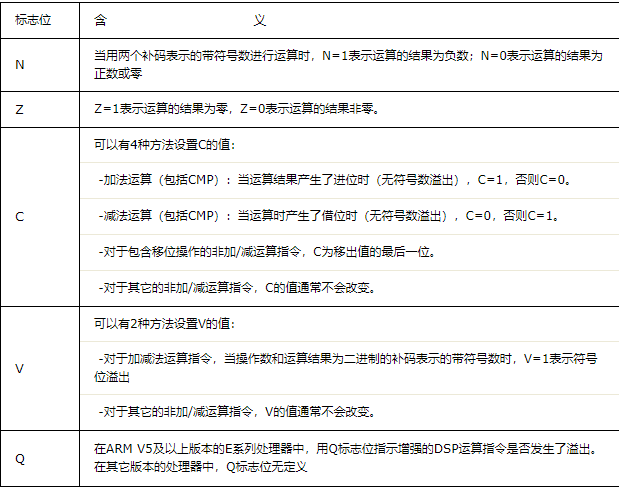

1.5.1 条件代码标志

大多数的数据处理指令可以选择是否影响条件代码标志位(指令带S标志),有的指令强制影响

所有的ARM指令都可以按条件执行,但Thumb指令中只有分支指令可按条件执行

1.5.2 控制位

- CPSR的低8位,发生异常时这些位会被改变,当处理器运行于特权模式时,这些位可通过程序修改

| I | IRQ中断禁止位 | 置1,禁止中断,置0,使能中断 |

|---|---|---|

| F | FIQ中断禁止位 | 置1,禁止中断,置0,使能中断 |

| T | 处理器状态位 | 置1,Thumb模式,置0,ARM模式 |

切换T时,ARM/Thumb状态时,ARM的工作模式和寄存器内容不变

- 模式位如下

2. ARM异常

2.1 异常来源

- 内部:软中断

- 外部:外设中断请求

需要用到IDT(异常向量表)

X86和ARM处理异常的区别:

X86发生异常时,根据中断号×4,在IDT中定位CPU到指定的向量地址,读取要执行的程序的地址

ARM发生异常时,根据发生中断的模式(IRQ,FIQ…),在IDT中定位到指定的向量地址,读取要执行的指令的地址,一般是一条跳转指令,而且,这时候只知道发生终端的总称,还需要具体判断发生中断的是哪个设备

一个是指令一个是程序,需要区分

2.2 进入异常

- PC+4/+8 —>LR (ARM状态),PC+2/+4 —>LR (Thumb状态)

- CPSR —> SPSR

- 根据异常模式更改CPSR(MOD:M4~0)

- I/F置1,禁止中断

- 根据IDT更改PC

异常总是在ARM状态下处理,会自动切换

2.3 退出异常

- LR-1/-2.. —> PC(根据异常类型返回)

- SPSR —> CPSR

- I/F置0,恢复中断(SPSR —> CPSR这个动作会自动恢复)

2.4 中止

发生在对存储器不能访问时

- 预取中止:发生在指令预取过程中

- 数据中止:发生在对数据的访问中

2.5 软件中断指令(SWI)

- 进入管理模式

2.6 未定义指令

- 陷阱程序

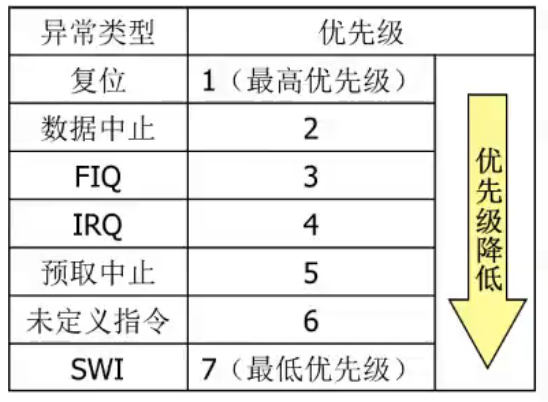

2.7 异常优先级

2.8 复位

nRESET信号被拉低,处理器放弃正在执行的指令

在复位后,除PC(0地址)和CPSR(管理模式)之外的所有寄存器的值都不确定

处理器操作:

- CPSR:M[4:0]管理模式

- I/F置位,(关中断)

- T清零,(进入ARM状态)

- PC从0X00取指

- 返回到ARM状态,恢复执行

3. Thumb指令集

3.1 指令特点

- 紧密度优化

- 提升窄内存性能

- 是ARM指令集子集

- 没有条件执行

- 只使用低端寄存器R0-R7

- 常量大小限制

- 不是常规指令集,编译器生成,而不是手动编写

- BX指令切换ARM/Thumb状态

切换T时,ARM/Thumb状态时,ARM的工作模式和寄存器内容不变

4. 内存和I/O

- ARM线性地址空间,

- 字宽寄存器,按字节顺序寻址

- 支持大端小端

访问对齐

如果存储器格式与芯片的存储器格式不符时,只有以字为单位的数据存取才正确

4.1 存放格式

- 大端模式:高数据位,低地址位

- 小端模式:低数据位,低地址位

半字占2个字节

字节占4个字节

4.2 I/O

4.2.1 接口信息

CPU与I/O设备之间的接口信息:数据、状态、控制信息

- 数据信息

- 数字量

- 模拟量

- 开关量

- 状态信息

- 反应外设当前工作状态

- READY/BUSY

- 控制信息

- 读写

- 时序

- 中断

- 片选

4.2.2 端口编址

- 存储器映射编址

- I/O与内存统一编址。I/O单元和内存单元同一地址空间

- 优点:可采用丰富的内存操作指令访问I/O单元,无需单独的I/O地址译码电路,无需专用I/O指令

- 缺点:外设占用内存空间,I/O程序不易读

- 举例:ARM

- I/O映射编址

- 分开编址

- 优点:I/O不占内存空间,I/O程序易读

- 缺点:I/O操作指令单一的传送指令,需要地址译码电路

- 举例:通用处理器

ARM的I/O端口内存映射

- 寄存器

- 不同于正常的存储器位置的操作,没有高速缓存和无缓冲区(避免对正常时序的影响)