内容概要:计算机发展历程、计算机硬件的基本组成、硬件的工作原理、计算机系统的层次结构、计算机性能指标、相关习题

计算机发展历程

什么是计算机系统

计算机系统 = 硬件 + 软件

计算机性能的好坏取决于软、硬件功能的总和

软件可细分为两类

- 系统软件:用来管理整个计算机系统

-

硬件的发展

逻辑元件:处理电信号的最小基本单元

电子管——晶体管——集成电路

摩尔定律:集成电路上可容纳的晶体管数目,约每隔 18 个月便会增加一倍,整体性能也将提升一倍软件的发展

机器语言——汇编语言——高级语言

DOS——WINDOWS——ANDROID/IOS目前的发展趋势

微型计算机向更微型化、多用途、网络化、高性能方向发展

- 巨型计算机向更巨型、超高速、并行处理、智能化方向发展

计算机硬件的基本组成

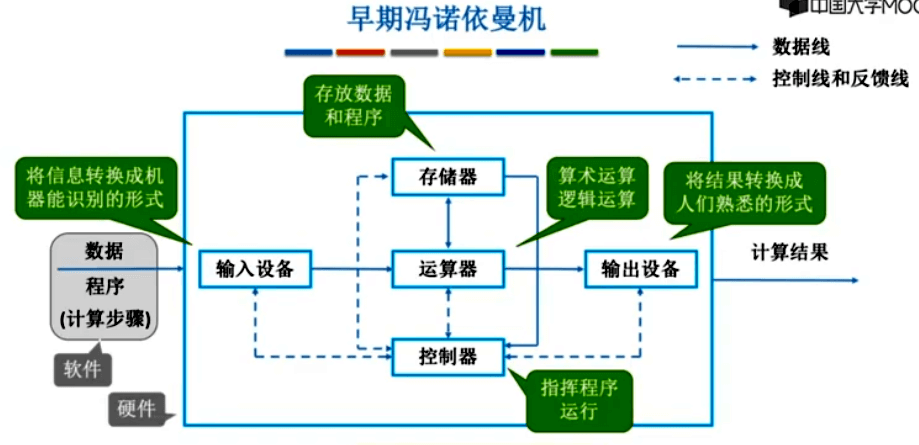

早期冯诺依曼机的结构

冯诺依曼首次提出了存储程序的概念,使计算机的执行不再依靠手动接线来控制。

存储程序的概念是指将指令以二进制代码的形式事先输入计算机的主存储器,然后按其在存储器中的首地址顺序执行程序指令,直至程序执行结束。

在计算机系统中,软件和硬件在逻辑上是等效的。即同一功能,既可以用软件实现,也可以用硬件实现。

用软件实现成本更低,效率更低,用软件实现成本更高,效率更高。

冯诺依曼机的特点

- 计算机由五大部件组成

- 指令和数据以同等地位存于存储器,可按地址寻访

- 指令和数据用二进制表示

- 指令由操作码和地址码组成

- 存储程序

- 以运算器为中心

五大部分

- 输入设备:将信息转换成机器能识别的形式

- 输出设备:将计算结果转换成人们熟悉的形式

- 主存储器:存放数据和程序

- 运算器:算术运算 、逻辑运算

- 控制器:指挥各部件,使程序运行

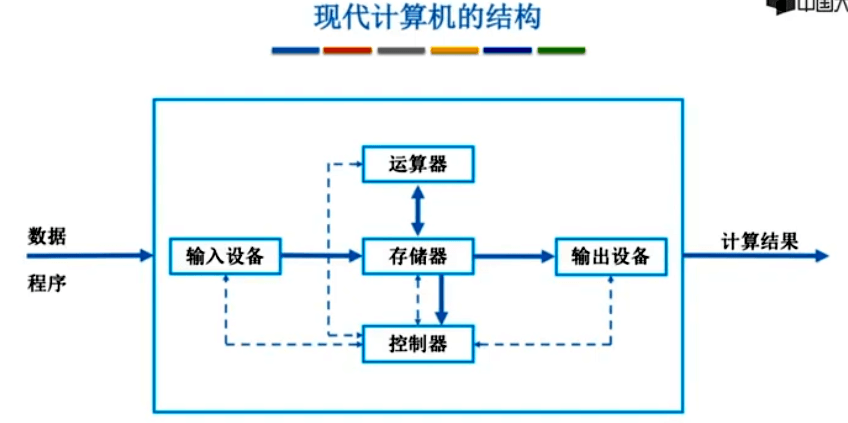

现代计算机的结构

现代计算机:以存储器为中心

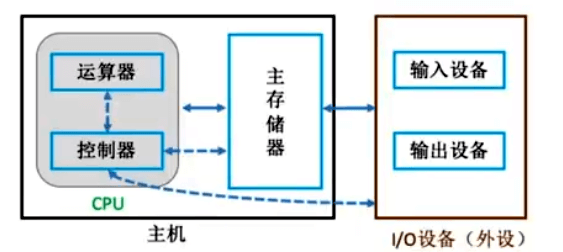

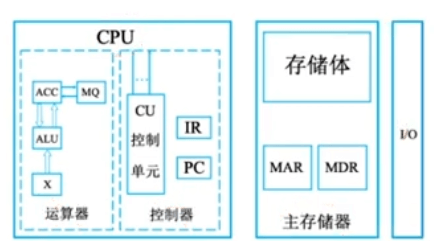

CPU = 运算器 + 控制器

将结构框图简化如下

存储器可分为主存和辅存

- 主存即内存,属于主机

辅存即机械 / 固态硬盘等,属于 I/0 设备,只在计算机需要的时候才将辅存中的数据读入内存中

硬件的工作原理

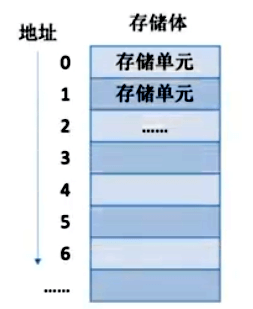

主存储器

读:CPU——MAR——存储体——MDR——CPU

写:CPU——MAR——MDR——存储体

数据在存储体中按地址存储

存储体被由一个个存储单元构成,存储单元内存储的一串二进制代码叫做存储字 (word),二进制代码的位数叫做存储字长。用于存储二进制数据的电子元件叫做存储元,每个存储元可存 1bit,存储元由电容的原理制作。

MAR 地址寄存器,用于指明要读 / 写哪个存储单元。其位数反映存储单元的数量。

MDR 数据寄存器,用于暂存要读 / 写的数据。其位数 = 存储字长。

MAR=4 位——总共有 24 个存储单元

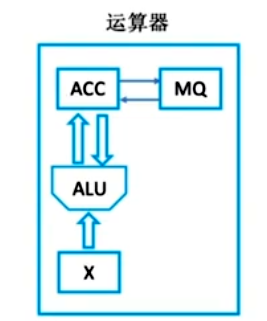

MDR=16 位——每个存储单元可存放 16bit,1 个字 = 16bit运算器

ACC:累加器,用于存放操作数、运算结果

MQ:乘商寄存器,在乘除运算时,用于存放操作数、运算结果

X:通用寄存器,用于存放操作数

ALU:算术逻辑单元,用电路实现各种算数运算、逻辑运算控制器

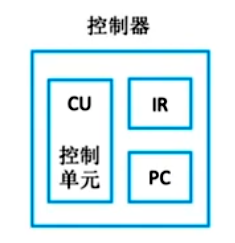

CU:控制单元,分析指令,给出控制信号

IR:指令寄存器,存放当前执行的指令

PC:程序计数器,存放下一条指令地址,有自动加 1 功能

PC——IR——CU

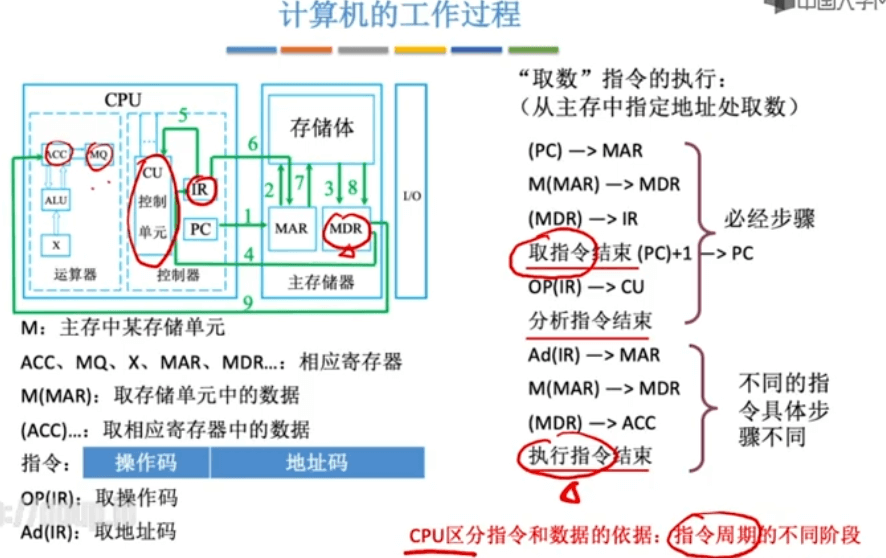

取指——执行计算机的工作过程

初始:事先将指令、数据存入主存,PC 指向第一条指令

从主存中取指令放入 IR,PC 自动加 1,CU 分析指令,CU 指挥其他部件执行指令

CPU 区分指令和数据的依据:指令周期的不同阶段

取指——执行

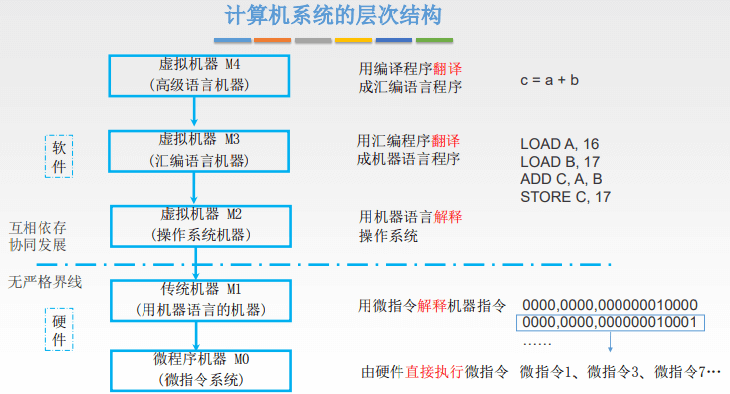

注:现在的计算机通常把 MAR、MDR 集成在 CPU 内计算机系统的层次结构

下层是上层的基础,上层是下层的扩展

五层结构M4:高级语言机器(执行高级语言)

- M3:汇编语言机器(执行汇编语言)

- M2:操作系统机器(向上提供广义指令)

- M1:传统机器(执行机器语言指令)

- M0:微程序机器(执行微指令 )

三个级别的语言

- 高级语言、汇编语言、机器语言

- 编译程序:将高级语言一次全部翻译成汇编语言,或直接翻译为机器语言

- 汇编程序:将汇编语言翻译成机器语言

- 解释程序:将高级语言翻译为机器语言(翻译一句执行一句)

计算机性能指标

存储器的性能指标

总容量 = 存储单元个数 × 存储字长(单位:bit)1Byte = 8 bit

CPU 的性能指标

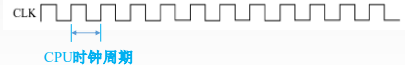

- CPU 主频:CPU 内数字脉冲信号振荡的频率10HZ 即 1 秒 10 个脉冲信号,时间上是 10 个时钟周期

- CPU 时钟周期:一个脉冲信号的时间(单位:微秒、纳秒)

- CPU 主频 (时钟频率)=

⭐

- CPI(Clock cycle Per Instruction):执行一条指令所需的时钟周期数不同的指令,CPI 不同。甚至相同的指令,CPI 也可能有变化。

- 执行一条指令的耗时 = CPI × CPU 时钟周期

- CPU 执行时间 (整个程序的耗时) =

⭐

- IPS(Instruction Per Second):每秒执行多少条指令MIPS:每秒执行多少百万条(10^6)指令

- CPI =

⭐

- FLOPS(Floating-point Operations Per Second):每秒执行多少次浮点运算

注:CPU 的性能指标中 K、M、G、T 位数量单位,描述频率速率

系统整体的性能指标

数据通路带宽:数据总线一次所能并行传送信息的位数(各硬件部件通过数据总线传输数据)

吞吐量:系统在单位时间内处理请求的数量

响应时间:指从用户向计算机发送一个请求,到系统对该请求做出响应并获得它所需要的结果的等待时间

用基准程序来动态评测计算机性能

习题

- 假定基准程序 A 在某计算机的运行时间为 100 秒,其中 90 秒为 CPU 时间,其余时间为 I/O 时间,若 CPU 速度提高 50%,I/O 速度不变,则运行基准程序 A 所消耗的时间为 ( )

A. 55 秒

B. 60 秒

C. 65 秒

D. 70 秒

解析:

令原始主频为 f,则原始时钟周期 T = 1 / f.

CPU 速度提高 50%,则 f2 = 1.5f, 故 T2 = 1 / (1.5f)= 2 / (3f)

由:CPU 执行时间 t = CPU 时钟周期数 C CPU 时钟周期 T

CPU 时钟周期数 C 不变,则 t 与 T 成正比。

故, t2 = (2/3)t = 90 2/3 = 60(s)

基准程序 A 所耗费的时间 = 60+10 = 70(s)

所以答案为 D.

解题技巧:

若 CPU 速度提高 n%,则 CPU 时间 t2 = t1 / (1+n%)

- 下列选项中,描述浮点数操作速度指标的是()

A. MIPS

B. CPI

C. IPS

D. MFLOPS

解析:

FLOPS(Floating-point Operations Per Second):每秒执行多少次浮点运算

所以答案为 D.

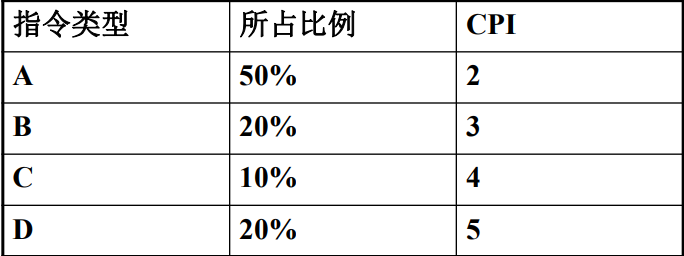

- 某计算机主频 1.2GHz,其指令分为 4 类,它们在基准程序中所占比例及 CPI 如下表所示

该机的 MIPS 数是()

A.100

B.200

C.400

D.600

解析: :::info MIPS = F/CPI

平均CPI = 0.52+0.23+0.14+0.25=3

所以MIPS=(1.2*10^9)/3=400MIPS ::: 所以答案为 C. :::info

- CPU 主频:CPU 内数字脉冲信号振荡的频率10HZ 即 1 秒 10 个脉冲信号,时间上是 10 个时钟周期

- CPU 时钟周期:一个脉冲信号的时间(单位:微秒、纳秒)

- CPU 主频 (时钟频率)=

⭐

- CPI(Clock cycle Per Instruction):执行一条指令所需的时钟周期数,不同的指令,CPI 不同。甚至相同的指令,CPI 也可能有变化。

- 执行一条指令的耗时 = CPI × CPU 时钟周期

- CPU 执行时间 (整个程序的耗时) =

⭐

- IPS(Instruction Per Second):每秒执行多少条指令MIPS:每秒执行多少百万条(10^6)指令

- CPI =

⭐

- FLOPS(Floating-point Operations Per Second):每秒执行多少次浮点运算 :::

- 程序 P 在机器 M 上执行时间是 20 秒,编译优化后,P 的指令数减少到原来的 70%,而 CPI 增加到原来的 1.2 倍,则 P 在 M 上的执行时间是()

A. 8.4 秒

B. 11.7 秒

C. 14.0 秒

D. 16.8 秒

解析:

tcpu = 时钟周期数 / f = (指令总数 × CPI) / f

f 不变, tcpu 与 (指令总数 × CPI) 成正比

故, t2cpu = (0.7 × 1.2) t1cpu = 0.84 × 20 = 16.8s

所以答案为 D. :::info

CPI(Clock cycle Per Instruction):执行一条指令所需的时钟周期数,不同的指令,CPI 不同。甚至相同的指令,CPI 也可能有变化。

:::info

CPI(Clock cycle Per Instruction):执行一条指令所需的时钟周期数,不同的指令,CPI 不同。甚至相同的指令,CPI 也可能有变化。

CPU 执行时间 (整个程序的耗时) =⭐ :::

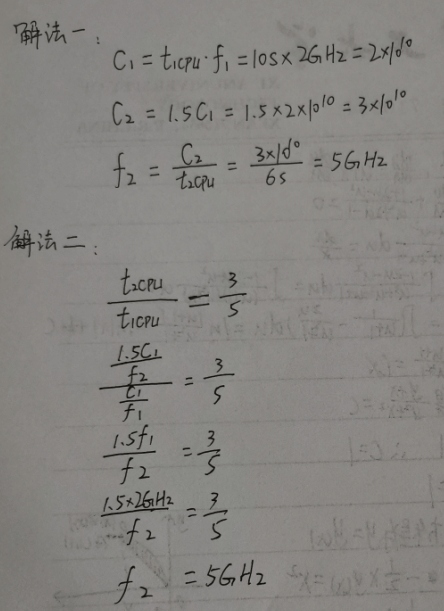

- 假设某程序 P 在机器 M1 上运行需要 10s,M1 的时钟频率 2GHz。设计人员想开发一种与 M1 具有相同 ISA 的新机器 M2。采用新的技术可以提高 M2 的时钟频率,但同时也会使 CPI 增加。假定 P 程序在 M2 上的时钟周期数是在 M1 上的 1.5 倍,则 M2 的时钟频率至少达到多少才能使 P 在 M2 上的运行时间缩短为 6s?

注: 软件和硬件的界面: ISA(Instruction Set Architecture )指令集体系结构

解析:

该例说明:由于时钟频率的提高可能会对 CPU 的结构带来影响,从而使其他性能标准降低。因此,时钟频率提升会加快 CPU 的运行速度,但不能保证执行速度有相同倍数的提高。

- 假定计算机 M1 和 M2 有相同的指令系统结构(ISA),主频分别为 1.5GHz 和 1.2GHz。在 M1 和 M2 上运行某基准程序 P,平均 CPI 分别为 2 和 1,则程序 P 在 M1 和 M2 上运行时间的比值是

A. 0.4

B. 0.625

C. 1.6

D. 2.5

解析:

tcpu = (指令总数 × CPI) / f

指令总数相同,tcpu 与 CPI 成正比,与 f 成反比

t1cpu / t2cpu = (CPI1 / CPI2) × (f2 / f1) = (2/1) × (1.2GHz / 1.5GHz) = 1.6

所以答案为 C.

- 通常称 “容量为 640KB 的存储器是指”

A. 640×10^3 字节存储器

B. 640×10^3 位存储器

C. 640×2^10 位存储器

D. 640×2^10 字节存储器

解析:

对于存储器

640KB = 640 × 2^10 Byte = 640 × 2^10 × 8 bit = 640 ×2^13bit

所以答案为 D.

- 冯诺依曼计算机的核心思想是()

A. 二进制运算

B. 有存储信息的功能

C. 运算速度快

D. 存储程序控制

解析:

冯诺依曼首次提出了存储程序的概念

所以答案为 D.

- 冯诺依曼机工作方式的基本特点是()

A. 多指令流单数据流

B. 按地址访问并顺序执行指令

C. 堆栈操作

D. 按内容选择地址

解析:

存储程序的概念是指将指令以二进制代码的形式事先输入计算机的主存储器,然后按其在存储器中的地址顺序执行程序指令,直至程序执行结束。

计算机的工作过程:

初始:事先将指令、数据存入主存,PC 指向第一条指令

从主存中取指令放入 IR,PC 自动加 1,CU 分析指令,CU 指挥其他部件执行指令

所以答案为 B.

(1) 计算机系统由硬件系统和软件系统构成。

(2) 存储程序,并按地址顺序执行,这是冯诺依曼型计算机的工作原理。

(2) 用机器语言编写的程序可以由计算机直接执行。

- 计算机硬件能够直接执行的是

Ⅰ. 机器语言程序

Ⅱ. 汇编语言程序

Ⅲ. 硬件描述语言程序

A. 仅 Ⅰ

B. 仅 Ⅰ、Ⅱ

C. 仅 Ⅰ、Ⅲ

D. Ⅰ、Ⅱ、Ⅲ

解析:

硬件能直接执行的只能是机器语言(二进制编码),汇编语言是为增强机器语言的可读性和记忆性的语言,经过汇编后才能被执行。硬件描述语言是电子系统硬件行为描述、结构描述、数据流描述的语言。