- 简答题(5个)份

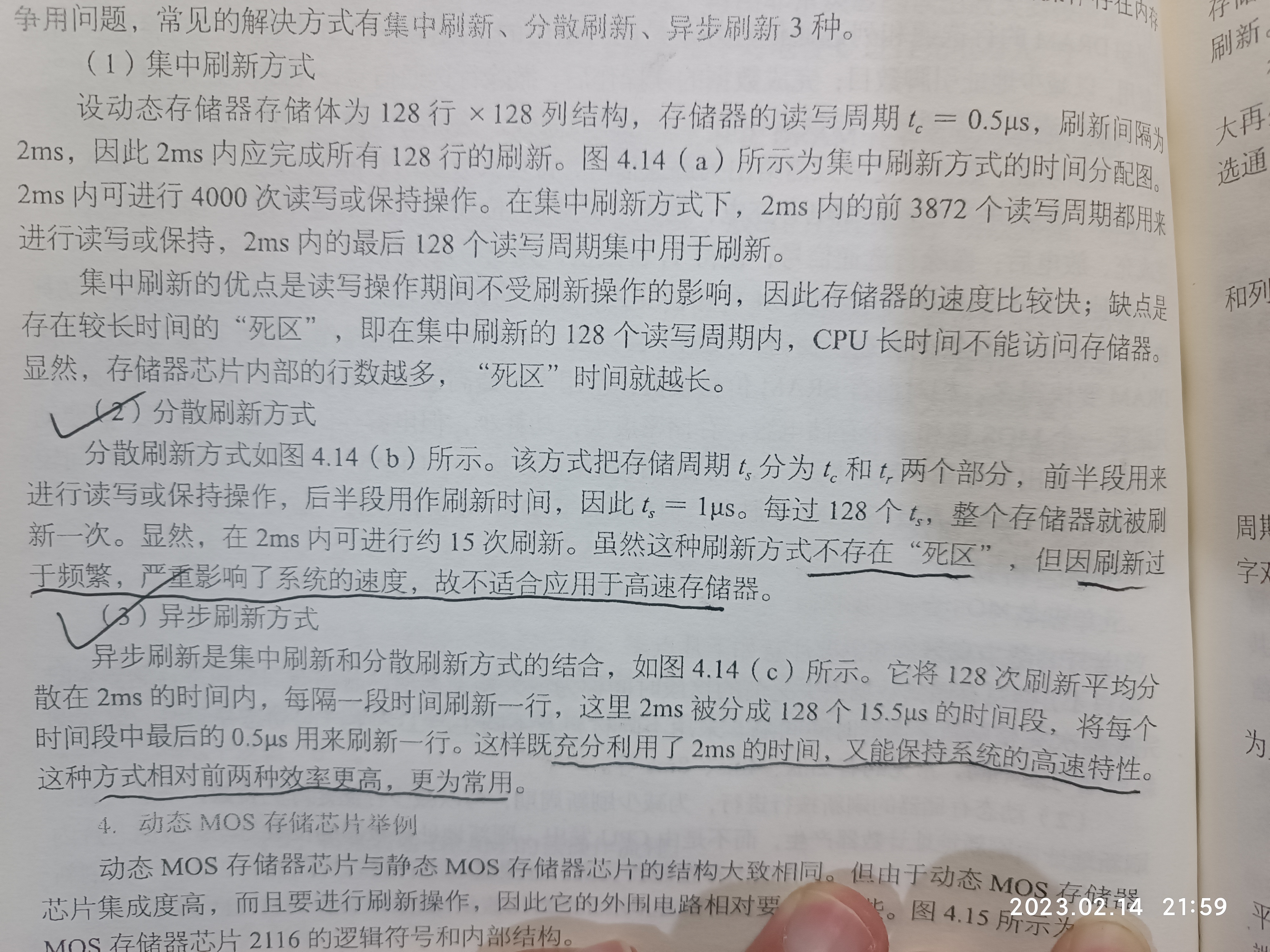

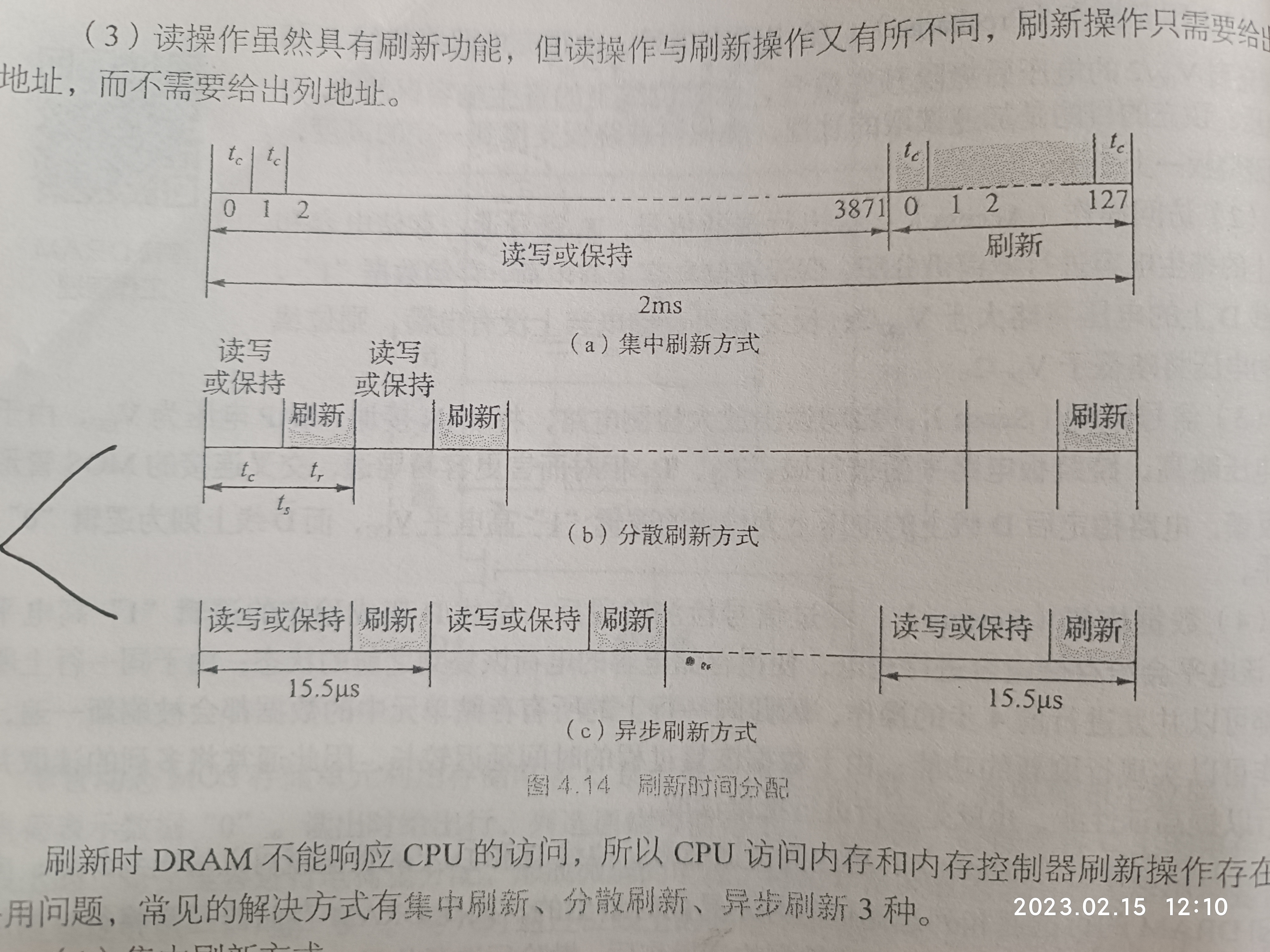

- 1.动态存储器芯片,简述分散式刷新与异步式刷新的基本原理以及优缺点

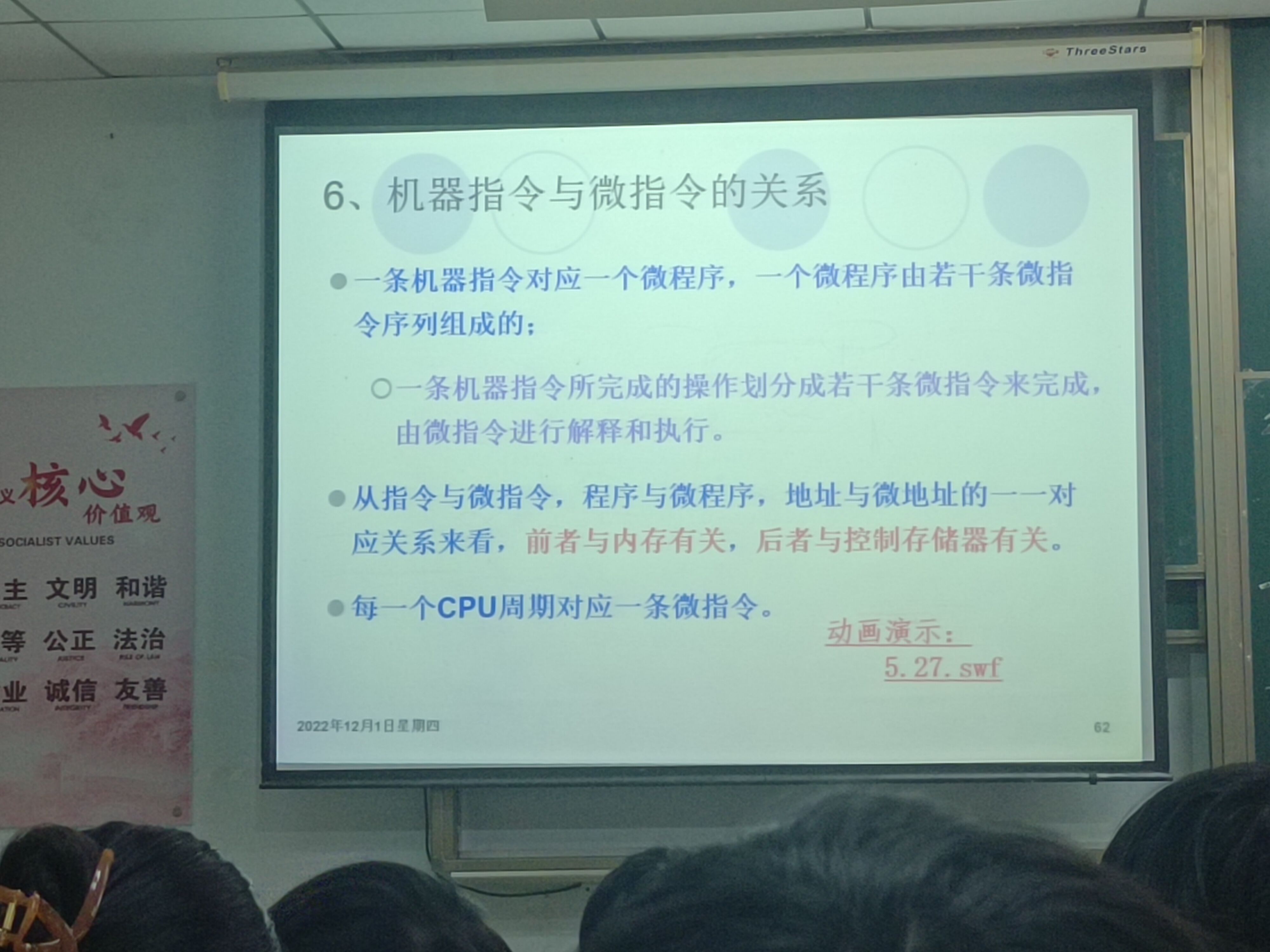

- 2.微程序控制器,微程序,微指令,微命令的关系是什么?

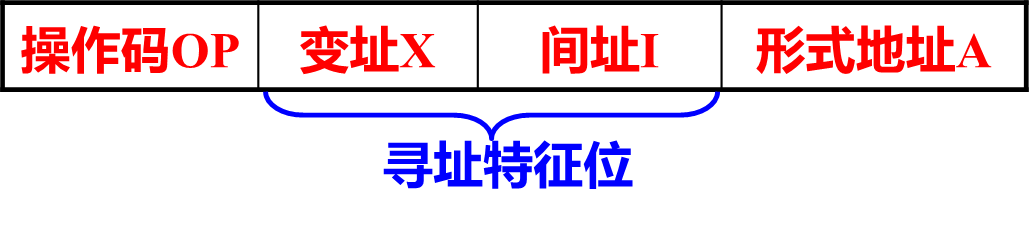

微命令构成一条条的微指令。一条条的微指分构成微程序,一条机器指令的执行需要段微程序去实现? - 3.指令系统,指分为操作码和地址码地址不码的寻址方式有直接寻址间接寻址,寄存器寻址,寄存器间接寻址,这些寻址式有什么不同?每一种寻址方式访问存储器的次数有多少次?

- 4.总线仲裁的作用义;集中式并行总线的仲裁方式基本原理是什么?集中式仲裁器的基本原理是什么?

- 5. 什么是中断?中断分为内中断和外中断,外中断主要是外部的设备要和主机进行数据交换,通讯。内中断王要是执行指令过程中产生的一些异常。

不管是什么中断都要解释猜楚什么是中断?还要描述中断的处理过程以及多中断的处理流程? - 指令周期、机器周期,时种周期这三个时间概念。

- 寻址方式:指令寻址方式,操作数寻址方式 什么是寻址方式)

- Cache:地址映射,替换算法,写算法

全相联射

直接映射

组相联映射

- 计算题

- 应用题

简答题(5个)份

1.动态存储器芯片,简述分散式刷新与异步式刷新的基本原理以及优缺点

2.微程序控制器,微程序,微指令,微命令的关系是什么?

微命令构成一条条的微指令。一条条的微指分构成微程序,一条机器指令的执行需要段微程序去实现?

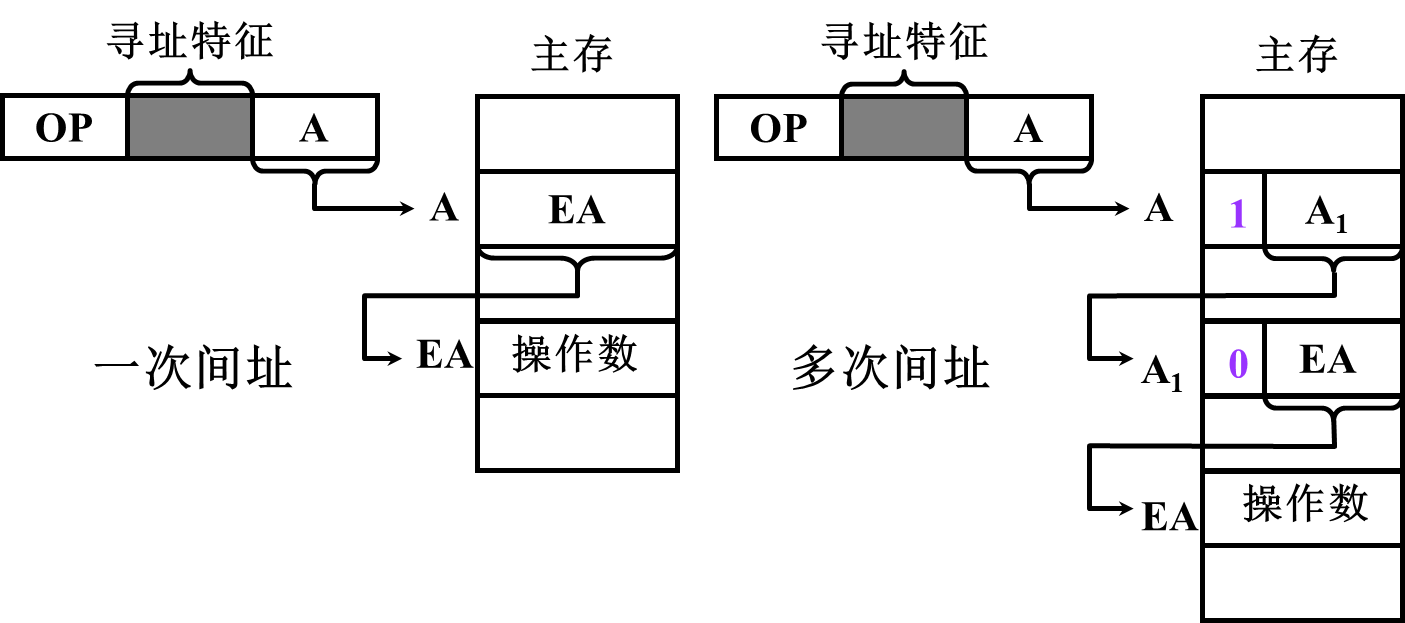

3.指令系统,指分为操作码和地址码地址不码的寻址方式有直接寻址间接寻址,寄存器寻址,寄存器间接寻址,这些寻址式有什么不同?每一种寻址方式访问存储器的次数有多少次?

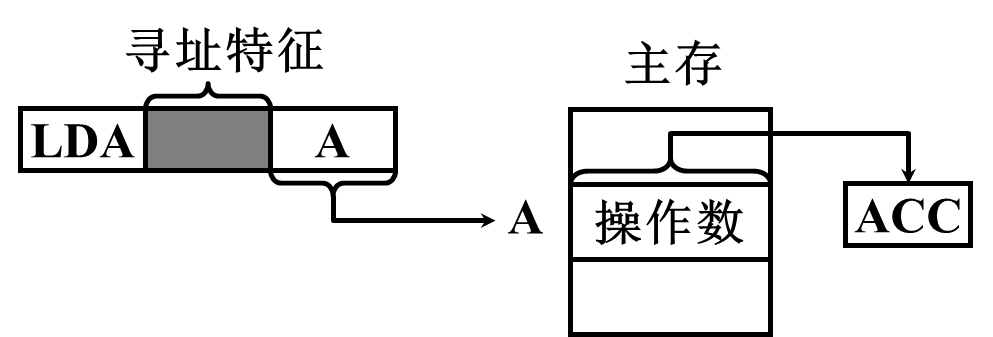

将指令中的形式地址A变换成操作数有效地址的过程,称为寻址过程。

:::success

隐含寻址:操作数地址隐含在操作码中;

立即寻址:形式地址A就是操作数;

直接寻址:有效地址由形式地址字段A直接给出;

间接寻址:有效地址由形式地址字段A间接提供,EA =(A)

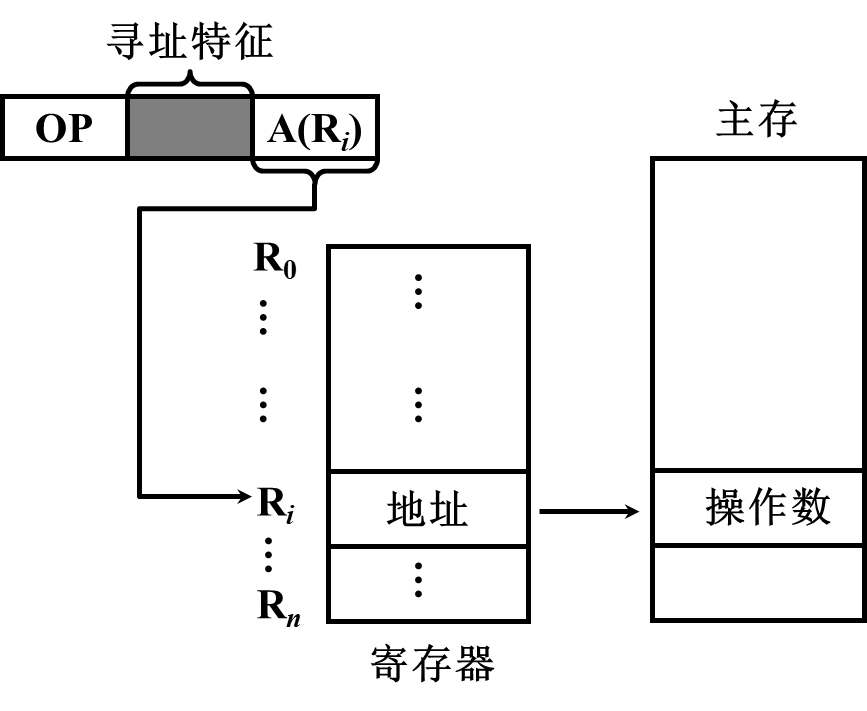

寄存器寻址:形式地址字段A为寄存器编号

寄存器间接寻址:形式地址字段A用于指出存放有效地址的寄存器编号;

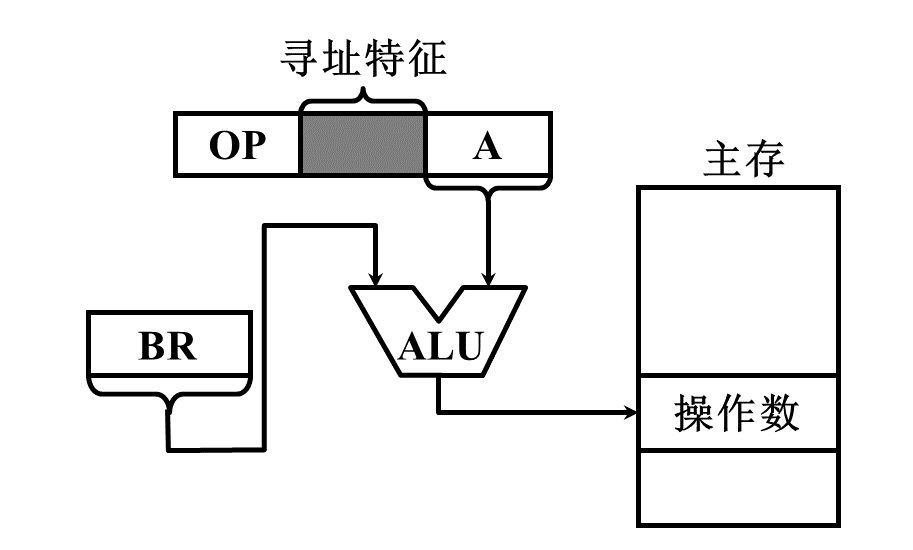

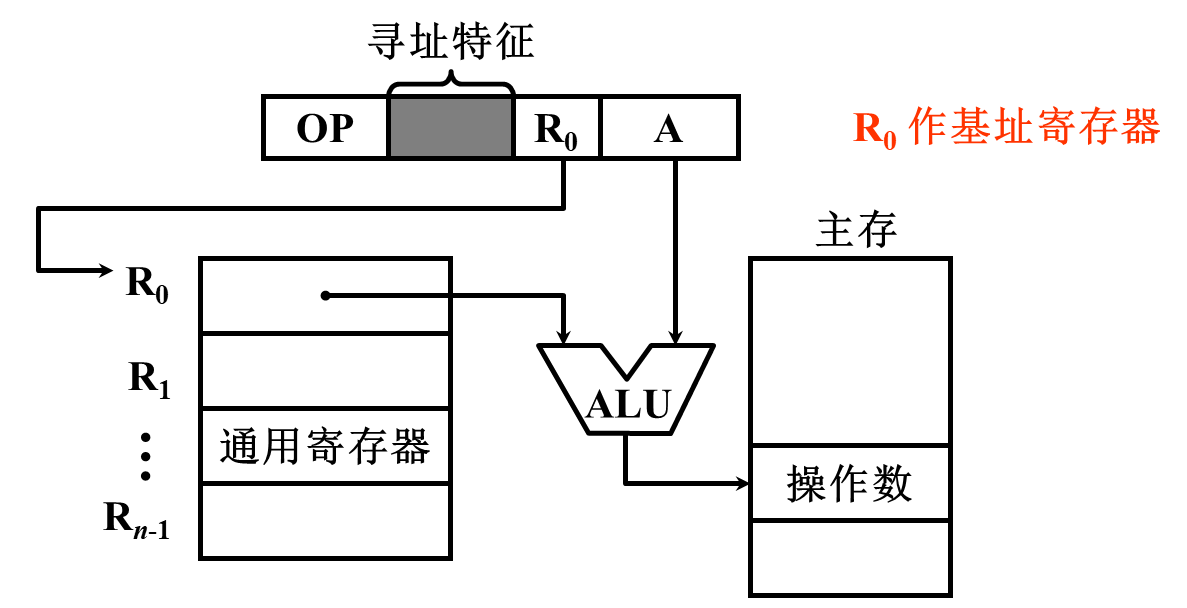

偏移寻址:直接寻址和寄存器间接寻址方式的结合

常用的偏移寻址

相对寻址:指令转移时,常用相对寻址方式;

EA=A+(PC)

基址寻址:EA=(基址R)+A ,A+1A

变址寻址:EA=A+(变址R) ,变址R+1变址R

有效地址EA=A+(R)

A是显式的形式地址字段;

R可以是显式的,也可以隐含的,某个专用的寄存器; :::

:::

4.总线仲裁的作用义;集中式并行总线的仲裁方式基本原理是什么?集中式仲裁器的基本原理是什么?

作用及意义:总线仲裁解决的是多个设备竞争使用总线的管理问题,由总线仲裁逻辑电路完成。

基本原理:集中式并行总线仲裁中,所有的设备都通过三条线连接到逻辑控制电路,再根据 相应的仲裁策略获得总线使用权。

5. 什么是中断?中断分为内中断和外中断,外中断主要是外部的设备要和主机进行数据交换,通讯。内中断王要是执行指令过程中产生的一些异常。

不管是什么中断都要解释猜楚什么是中断?还要描述中断的处理过程以及多中断的处理流程?

中断就是执行中断服务程序,这是中断系统的核心。处理过程:

准备部分,其基本功能是保护现场,对于非向量中断方式则需要确定中断源,最后开放中断,允许更高级的中断请求打断低级的中断服务程序;

处理部分,即真正执行具体的为某个中断源服务的中断服务程序;

结尾部分,首先要关中断,以防止在恢复现场过程中被新的中断请求打断, 接着恢复现场,然后开放中断,以便返回原来的程序后可响应其他的中断请求。

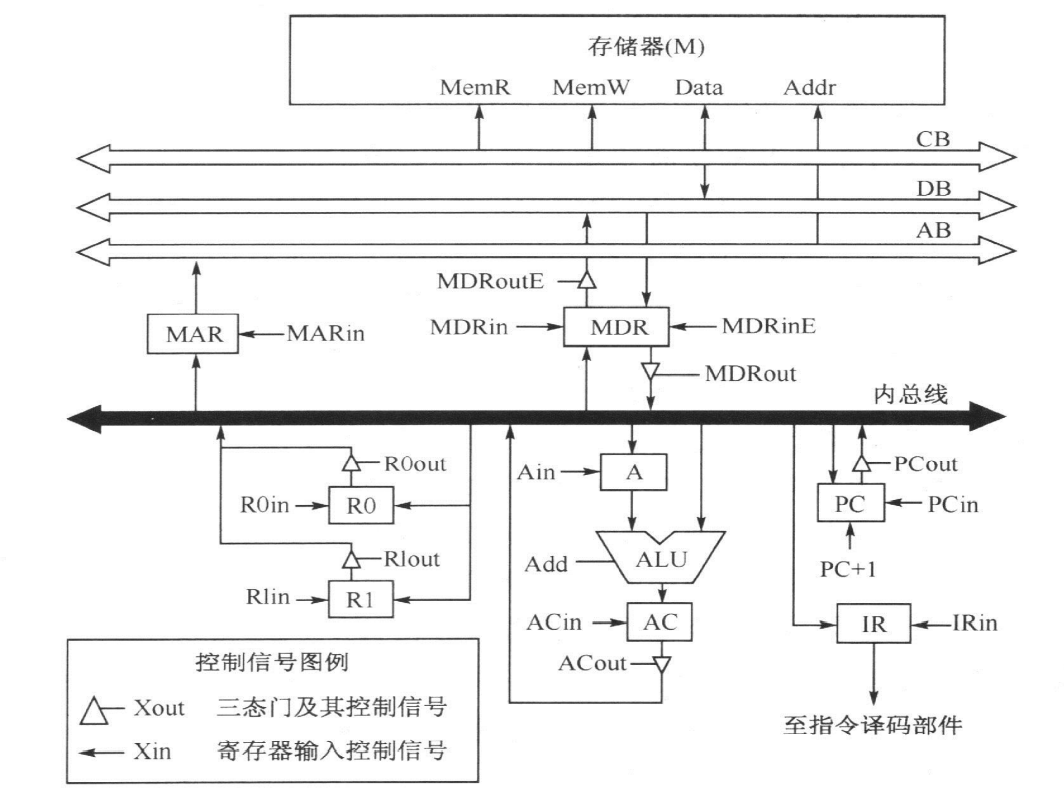

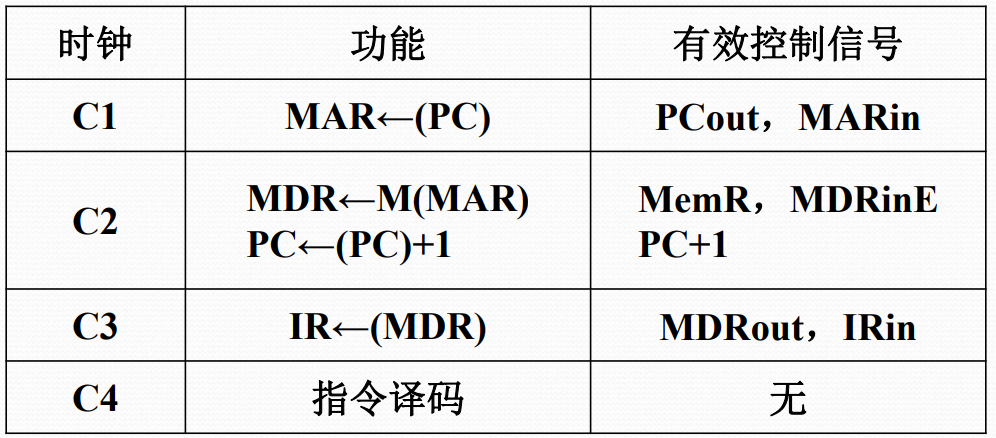

指令周期、机器周期,时种周期这三个时间概念。

CPU每取出并执行一条指令所需的全部时间称为指令周期;

机器周期是在同步控制的机器中,执行指令周期中一步相对完整的操作(指令步)所需的时间,通常安排机器周期长度=主存周期;

时钟周期是指计算机主时钟的周期时间,它是计算机运行时最基本的时序单位,对应完成一个微操作所需的时间,通常时钟周期=计算机主频的倒数

寻址方式:指令寻址方式,操作数寻址方式 什么是寻址方式)

Cache:地址映射,替换算法,写算法

全相联射

直接映射

组相联映射

计算题

有一个32位的非零规格化的浮点数,它是由三个部分构成的,比如说32位。符号,阶码,尾数 3个部分构成。其中尾数是23位,阶码是8位,符号位是1位,符号位位于最高位,紧跟着的8位是减码然后,剩下的23位是尾数,那么我们给定一个具体的数据,让你求32位的规格化的符点数的二进制的编码

让你我给定两个数据啊 一个正数一个负数 求所对应的32位的规格化的符点数的二进制编码

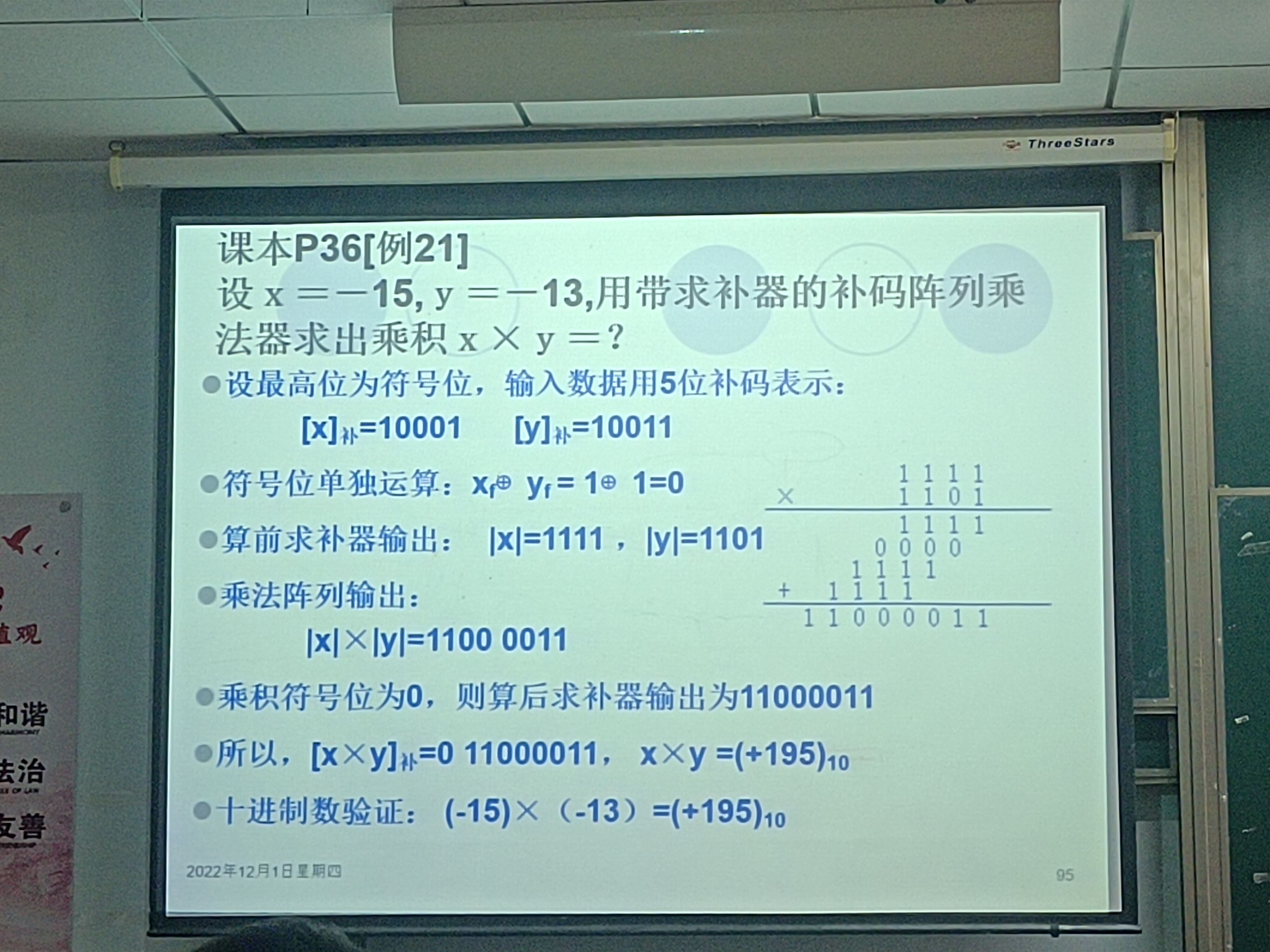

给定一个x和一个y,用补码表示这两个数据,并且用直接补码的阵列乘法器求出x乘y的积?(教材有例题)

![E6O]3D81~]L_`}BX(D4(TS.jpg![2EJGZA8RY{F]PDMOIQLOC62.jpg](/uploads/projects/u2304658432@professionalcourses/f8b277da09dee4d81b3a56ae3205556c.jpeg)

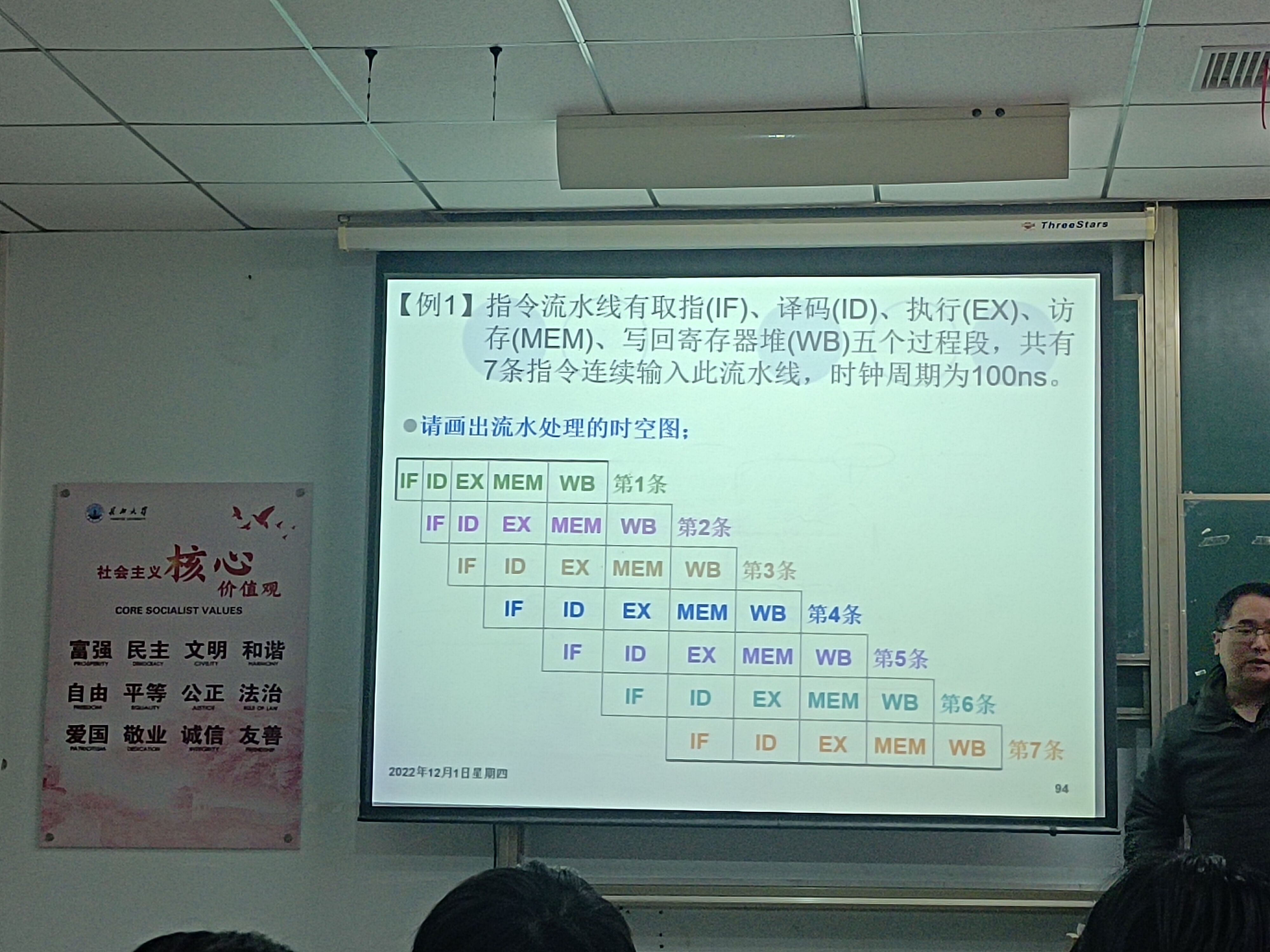

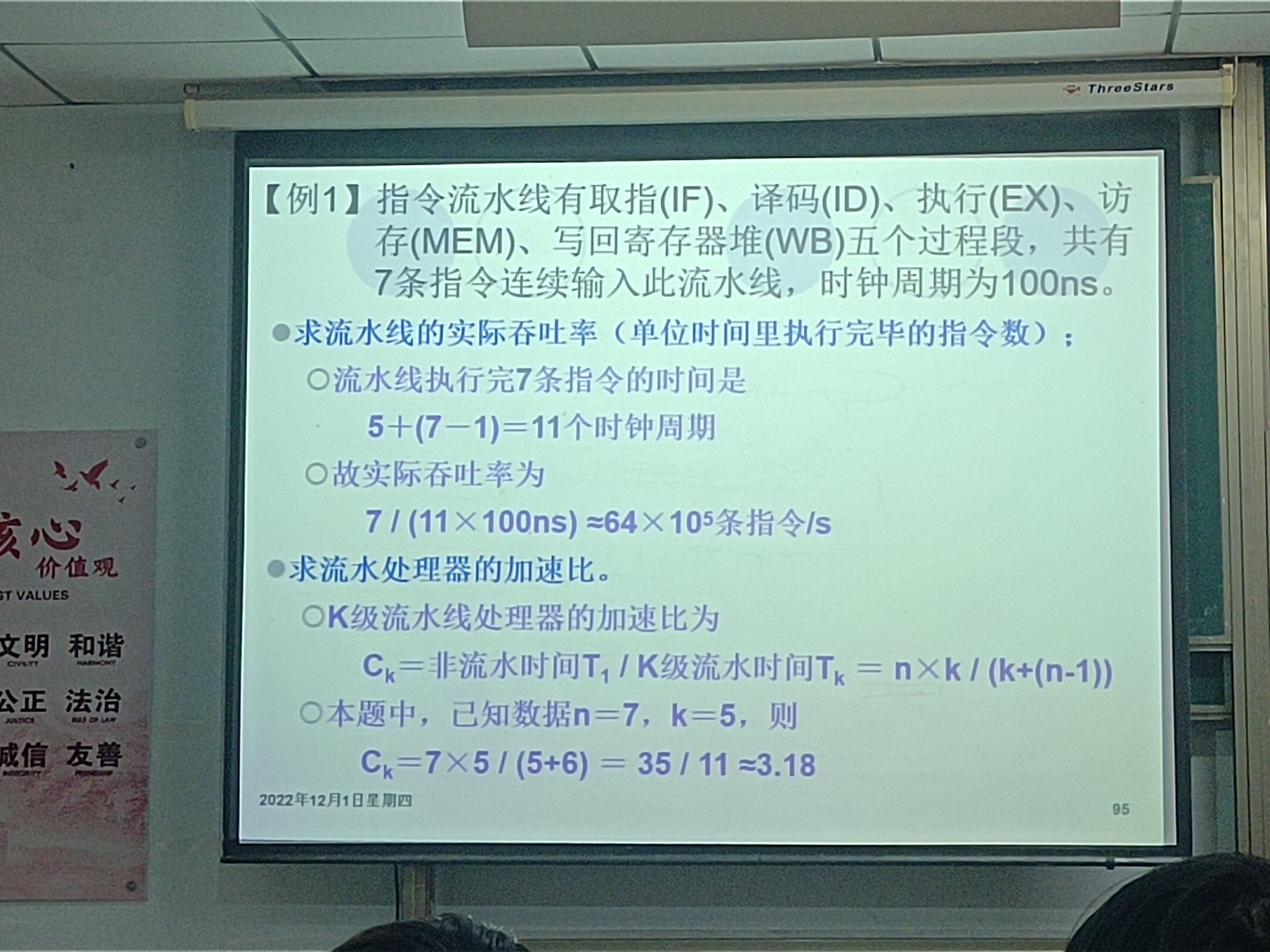

指令的执行过程:取址, 移码,执行,访问存储器,写回五个过程。如果一用户程序有7条指令,按照流水线送进去,时周期100ns、 画出流水处理的时空图,标量流水时空图。根据时空图,求出统水线吞吐量(单化时间内执行的指令数) ,求流水处理器的加速比(用处理器七条指令时间和非流水(冯诺依曼型)时间之比

应用题

(1).有一个8在机,采用半体物理若,地址码为18位, 如果果我们采用的静态存储片4kX4来组成最大存储空间,并采用存储条形式可来组织8位机存储器

问

- 有个模块条(如果是64kx8 ,其需要多少模安条、。(地址码为18位,那么最大存储容量2^18,256k, 利用4kX4来组织、

- 有个模块条包含多少芯片(4kx4多少才能构成64kx8),还有其包含多少芯片?CPU使用多少条地支线连接各个模块?使用什么样的译码器(38译码器,4-16译码器)

(2).控制器

给定一个数据通路(模型机),IR,PC,AR寄存器,DR,通用寄存器R1,R2,R3,暂存寄存器x,y,以及ACC用双总线将功能部件连接起来(IR为指令寄存器,PC为程序寄存器,模型机有M位,AR为地址寄存器,DR为数据寄存器,ACC为算术单元,每个部件都有一个控制信号机,I:输入,O:输出)

stop:R1,R2;将R1传送到R2中

根据指令功能画出指令周期流程图,在CPU里把动作描述出来(教材有例题)

:::success

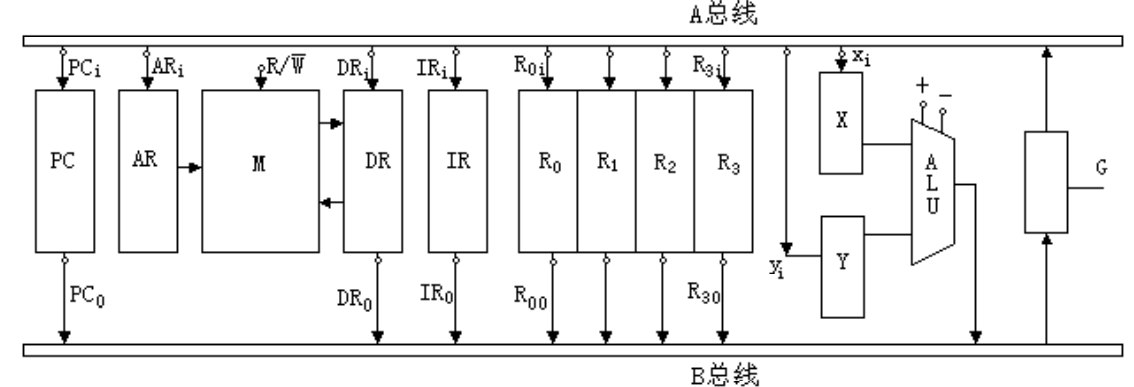

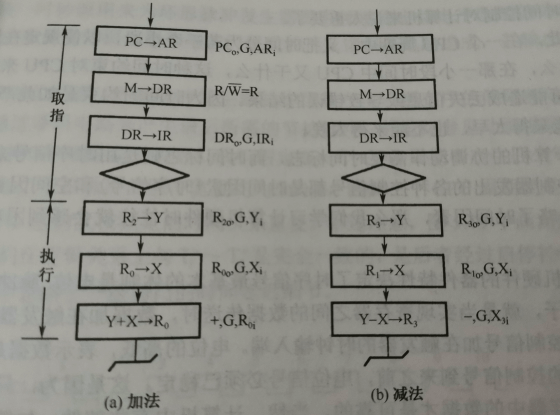

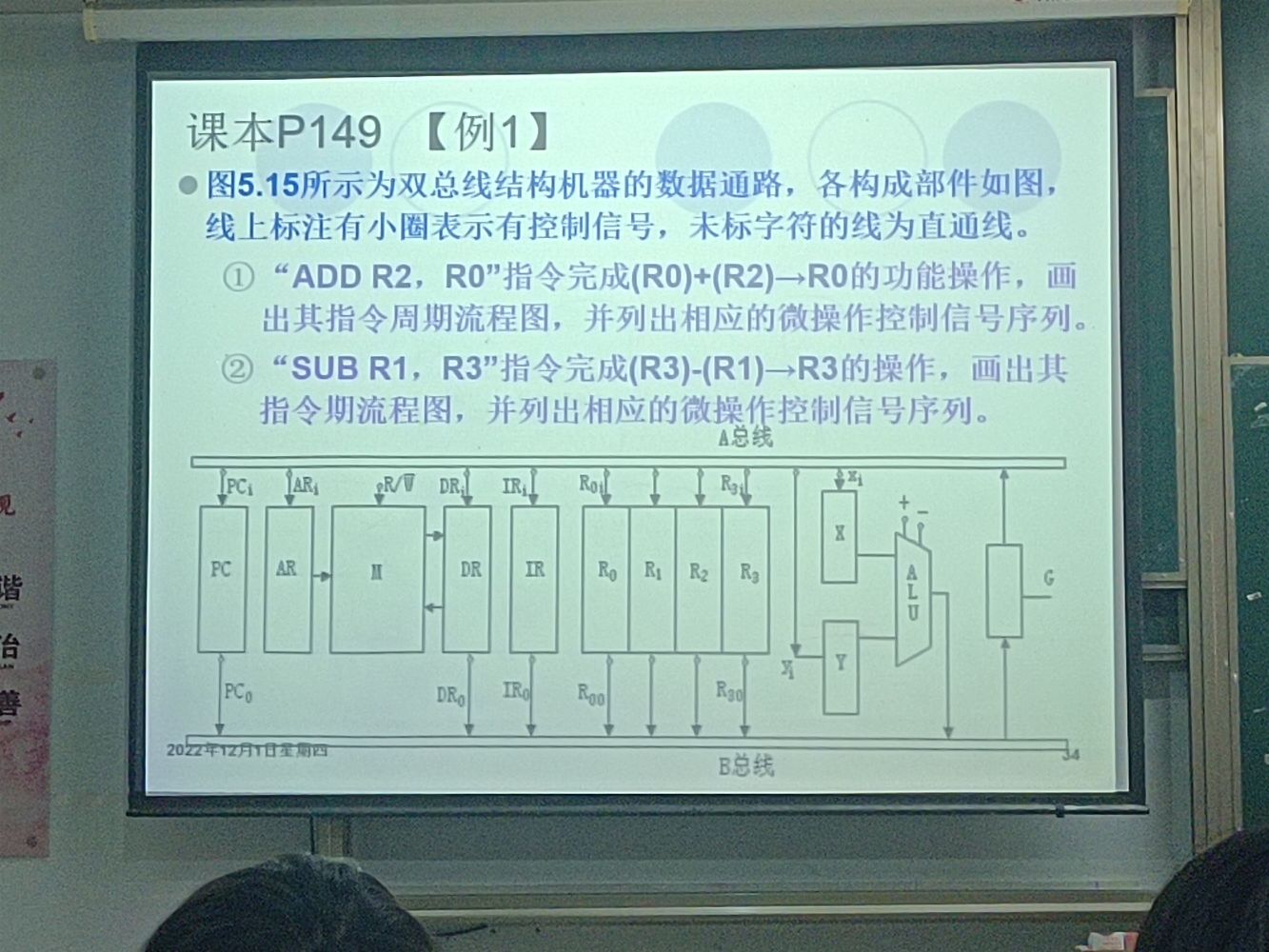

- 下图所示为双总线结构机器的数据通路,IR 为指令寄存器,PC 为程序计数器 (具有自增功能),M 为主存 (受 R/W 信号控制),AR 为地址寄存器,DR 为数据缓冲寄存器, ALU 由加、减控制信号决定完成何种操作,控制信号 G 控制的是一个门电路。另外,线上标注有小圈表示有控制信号,例中 yi 表示 y 寄存器的输入控制信号,R1o 为寄存器 R1 的输出控制信号,未标字符的线为直通线,不受控制。

(1) 指令 “ADD R2,R0”,完成 (R0)+(R2)→R0 的功能操作,画出其指令周 期流程图,假设该指令的地址已放入 PC 中。并列出相应的微操作控制信号序列

(2) 指令 “SUB R1,R3”,完成 (R3)-(R1)→R3 的操作,画出其指令期流程图 ,并列出相应的微操作控制信号序列

解析:

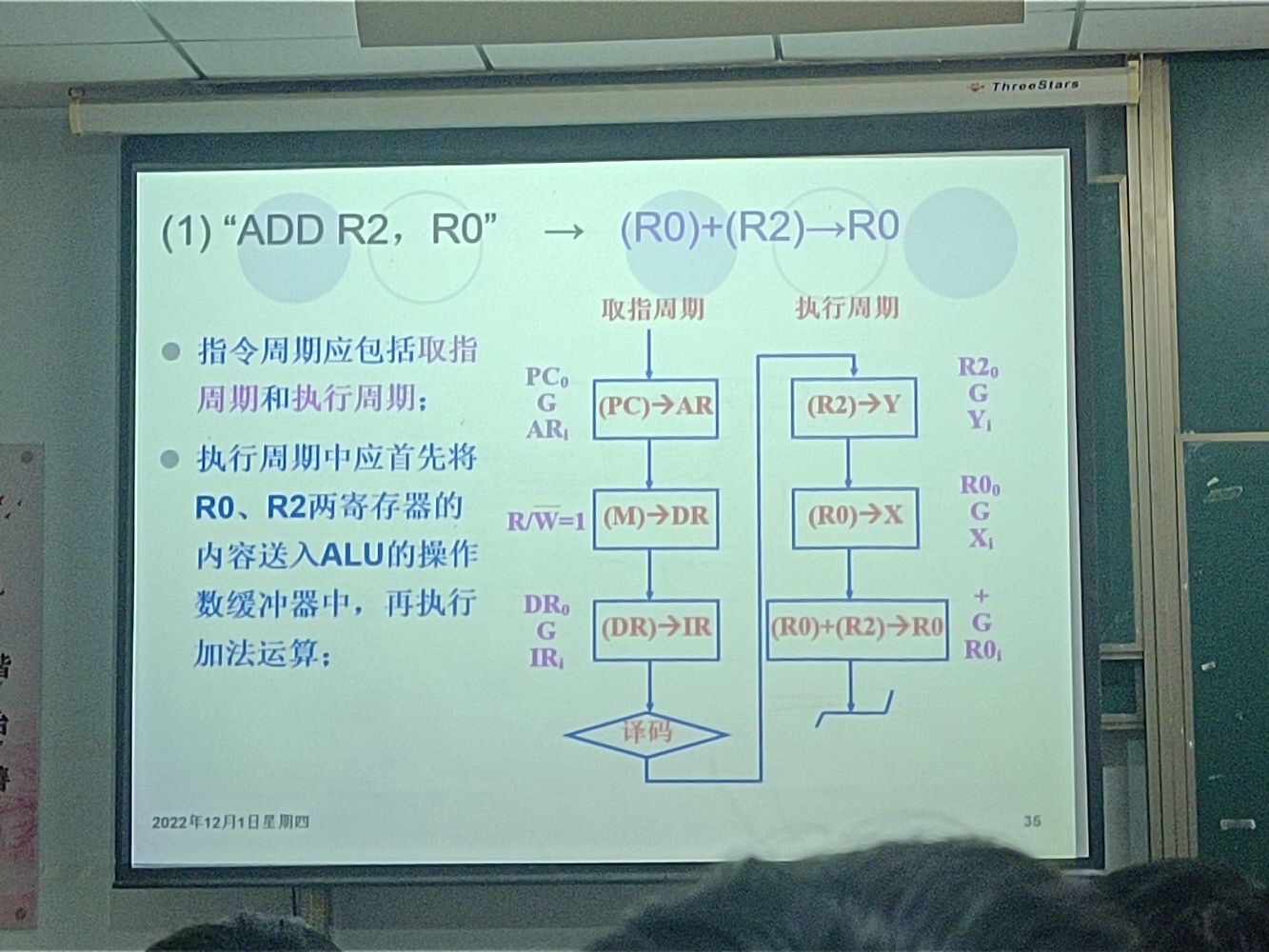

用方框图语言表示指令周期

- 方框:代表一个 CPU 周期,方框中的内容表示数据通路的操作或某种控制操作。

- 菱形:表示某种判别或测试,不过时间上它依附于紧接它的前面一个方框的 CPU 周期,而不单独占用一个 CPU 周期。

(1)“ADD R2,R0” 指令是一条加法指令,参与运算的两个数放在寄存器 R2 和 R0 中,指令周期流程图包括取指令阶段和执行指令阶段两部分 (为简单起见 ,省去了“→” 号左边各寄存器代码上应加的括号)。 根据给定的数据通路图,“ADD R2,R0” 指令的详细指令周期流程图如图 (a) 所示,图的右边部分标注了每一个机器周期中用到的微操作控制信号

(2)“SUB R2,R3”指令是一条减法指令,其指令周期流程图如图 (b) 所 示。与 ADD 指令不同的是:在执行指令阶段,微操作控制信号序列有所不同。

PC→AR:将指令地址从程序计数器中送入地址寄存器

M→DR:将指令从主存中读出读出到数据寄存器

DR→IR:将指令从数据寄存器送入指令寄存器

◇:分析指令

:::

:::

![@V4E$PC6{()C)KGRFILV.png

![NY2]{GX[6WB~ANEFTUZGK.png](https://cdn.nlark.com/yuque/0/2023/png/22782459/1676558829515-1be726ec-bfb7-4e5f-9dde-316ce0f2405f.png#averageHue=%23f6f7f4&clientId=u78ac5ed5-ef23-4&from=drop&id=uad061f2b&originHeight=483&originWidth=414&originalType=binary&ratio=1&rotation=0&showTitle=false&size=29572&status=done&style=shadow&taskId=u3505fd5e-1e00-442f-94a9-8b4d81c7d25&title=)

(3).假设有一个8位机,16位机,给一段C程序,有无符号数,符号数,定义一个变量,根据C程序进行加减乘除运算,运算结果放到CPU寄存器里面。那么寄存器里面存放的二进制编码是什么?(教材有,运算可能会给出,无符号,有符号怎么标识)