8088/8086 微处理器

简介

- 8088/8086 属于第三代微处理器的典型代表。

- 第三代微处理器和第二代微处理器的主要区别在于字长有了跨越式发展。

- 第二代微处理器主要是以 8 位微处理器为主要代表,第三代微处理器主要是以 16 位微处理器为主要代表

- 最初 Inter 公司的第三代微处理器主推 8086 芯片,它是一款 16 位微处理器,它在内部结构和对外通道上的处理能力都是 16 位,也就是说该芯片能够并行处理 16 位二进制码。但是为了与之前推出的主板和其他外部部件兼容,所以 Inter 公司又推出了 8088 微处理器。

- 8088 和 8086 的主要区别在外部通道上,8086 的对外通道是 16 位的,而 8088 的对外通道是 8 位的;两者内部结构都是 16 位。

说明:

面对科学研究,以学习前沿技术为主,面对教学研究,以学习基本原理和基础知识为主。因此不论是 8086、8088 还是如今的 64 位微处理器,它们最核心部分的基本原理都是类似的。为了后续学习方便,这里以学习 8088 芯片为主。

关注点:

- 8088/8086CPU 能够实现指令并行流水工作的原因;

- 实地址模式下的存储器地址变换原理

-

8088/8086CPU 的特点

此处的特点是与第二代及其之前的 CPU 相比

采用并行流水线工作方式

- 通过设置指令预取队列实现——CPU 内部结构

- 对内存空间实行分段管理

- 将内存分为 4 个段并设置地址段寄存器,以实现对 1MB 空间的寻址——实模式存储器寻址

支持协处理器

最小模式:是单处理器模式,所有控制信号由微处理器产生

- 最大模式:是多处理器模式,部分控制信号由外部总线控制器产生

- 用于包含协处理器的情况下

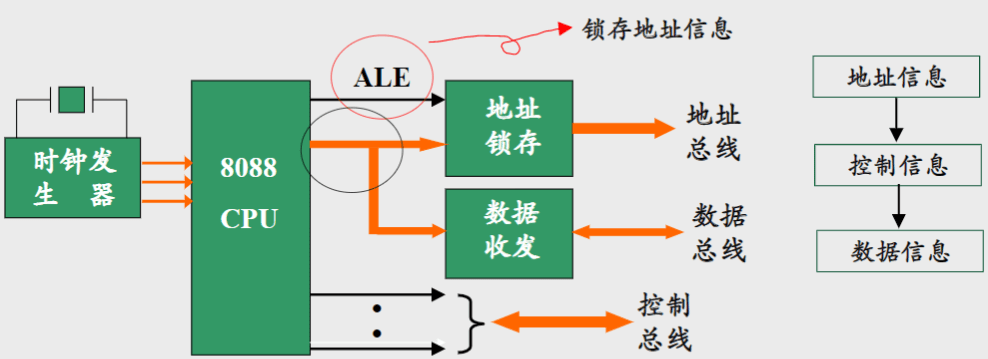

最小模式下的总线连接示意图:

- CPU 将地址信息通过控制总线发出后会将地址信息存入地址锁存器,防止该通道后续传输的数据信息冲掉该地址信息

- 数据收发模块是一个驱动器,连接 CPU 和数据总线,负责数据的收发

- 所有控制信号都由微处理器产生。所以 CPU 直接与地址总线相连

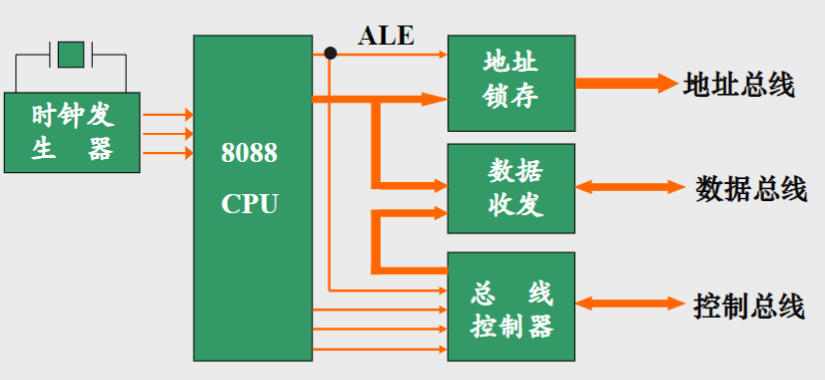

最大模式下的总线连接示意图:

由于需要与协处理器进行协调工作,所以控制信息通过总线控制器与控制总线连接,也就是说部分控制信号由外部总线控制器产生

两种工作模式的选择方式

8088 是工作在最小还是最大模式由 MN/\overline{MX}MN/MX 引线的状态决定

MN/\overline{MX}-0MN/MX−0 工作于最大模式

MN/\overline{MX}-1MN/MX−1 工作于最小模式

8088CPU 的主要引线及内部结构

8088CPU 最小模式下的主要引脚信号

完成一次访问内存或接口所需要的主要信号

- 与外部同步控制信号

- 中断请求和响应信号

-

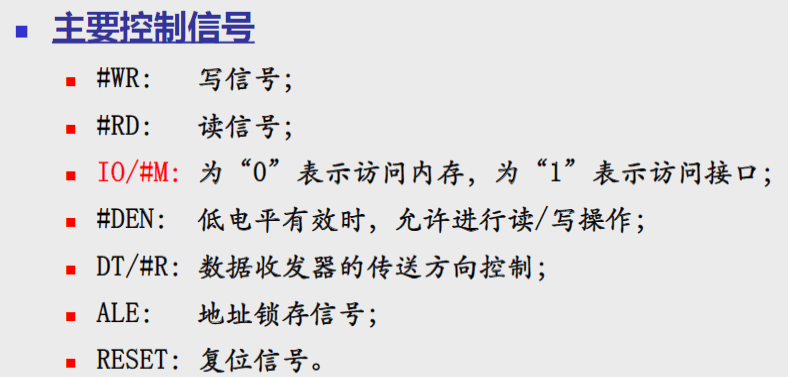

访存 / 接口信号

也就是上横线,表示低电平有效

DEN是数据收发器的选通信号

【例】当#WR=1,#RD=0,IO/#M=0时,表示 CPU 当前正在进行读存储器操作

外部同步控制信号

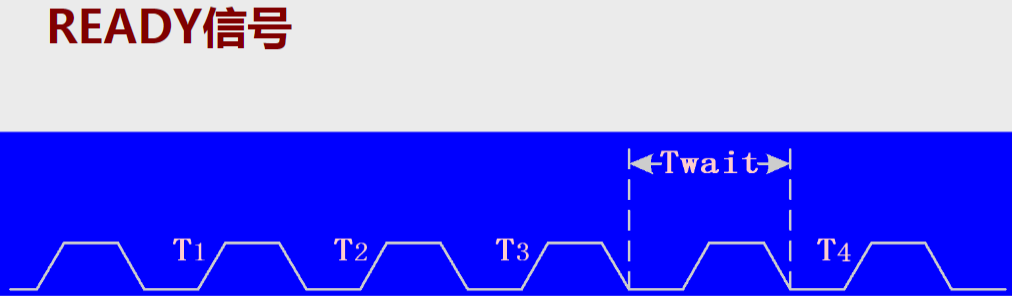

- READY 实现 CPU 与内存 / 接口之间同步控制的信号

在一个标准的总线周期中,正常情况下,可以完成一次访存或访接口的操作;但如果接口或内存还没准备就绪,可以在 T3 时钟周期之后,插入若干个 TWAIT 周期

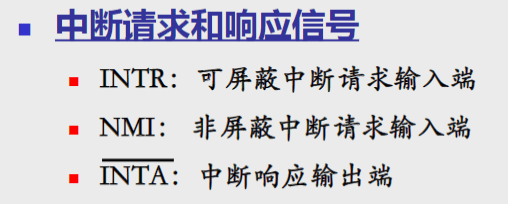

中断请求和响应信号

总线保持信号

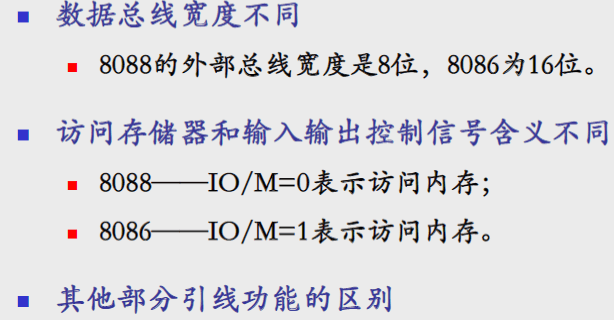

8088 和 8086CPU 引脚功能比较

8088 内部结构

无论是哪种型号的 CPU,在总的功能上都包括三个部分:控制器、运算器、寄存器组

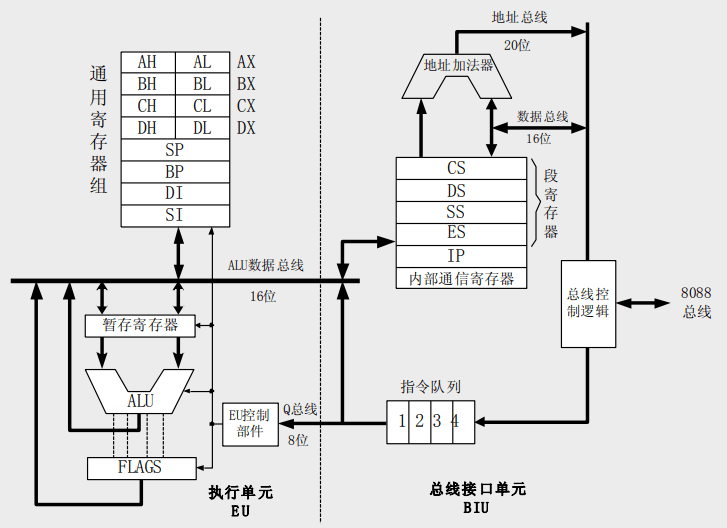

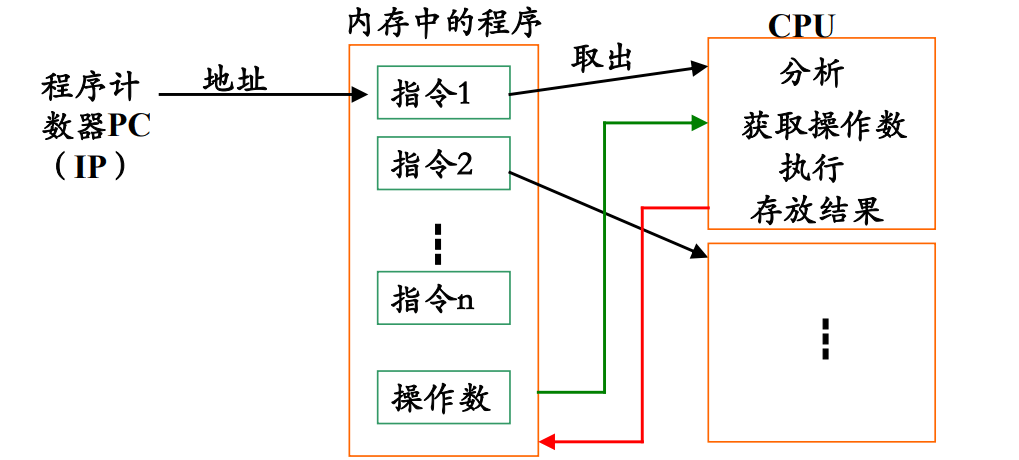

- Inter 公司在逻辑上把 CPU 分为执行单元和总线接口单元

- 执行单元:用来执行程序

- 总线接口单元:用来访问内存 / 接口

-

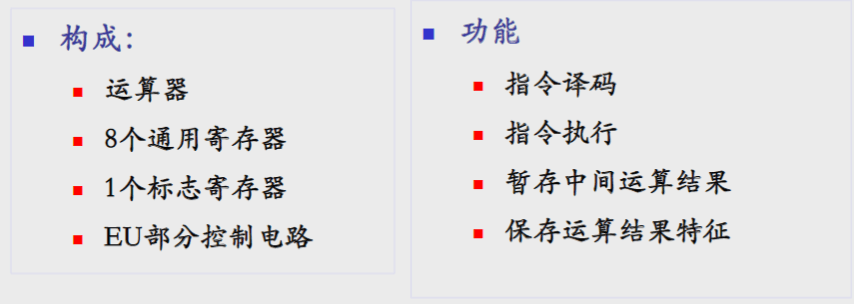

执行单元

FLGAS 标志寄存器:用来保留运算结果的特征。比如:两个数相加结果是否有进位、结果是否是零、结果是否有溢出等等

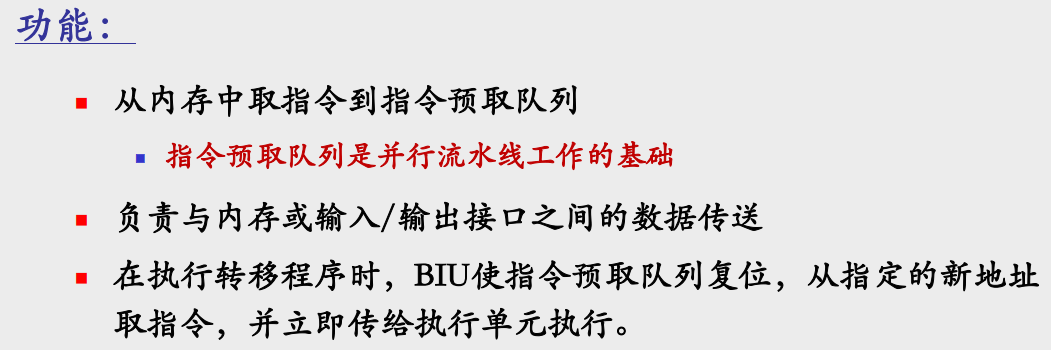

总线接口单元

CPU 从内存取到指令后不是直接经过译码交给运算器去执行,而是先放入指令预取队列中暂存

- 指令预取队列是并行流水线工作的基础

- 地址加法器可以将两个 16 位的地址相加得到一个 20 位的地址

指令预取队列的存在使 EU 和 BIU 两个部分可同时进行工作。EU 在分析和执行指令时,BIU 可以去取指令,实现了指令的并行执行。

8088CPU 内部寄存器

8088CPU 内部含 14 个 16 位寄存器,按功能可分为三类:

- 8 个通用寄存器

- 数据寄存器:AX、BX、CX、DX

- 地址指针寄存器:SP、BP

- 变址寄存器:SI、DI

- 4 个段寄存器

- CS、DS、ES、SS

2 个控制寄存器

AX:累加器

- 所有 I/O 指令都通过 AX 与接口传送信息,中间运算结果也多放于 AX 中;

- BX:基址寄存器

- 在间接寻址中用于存放基地址;

- CX:计数寄存器

- 用于在循环或串操作指令中存放计数值;

DX:数据寄存器。

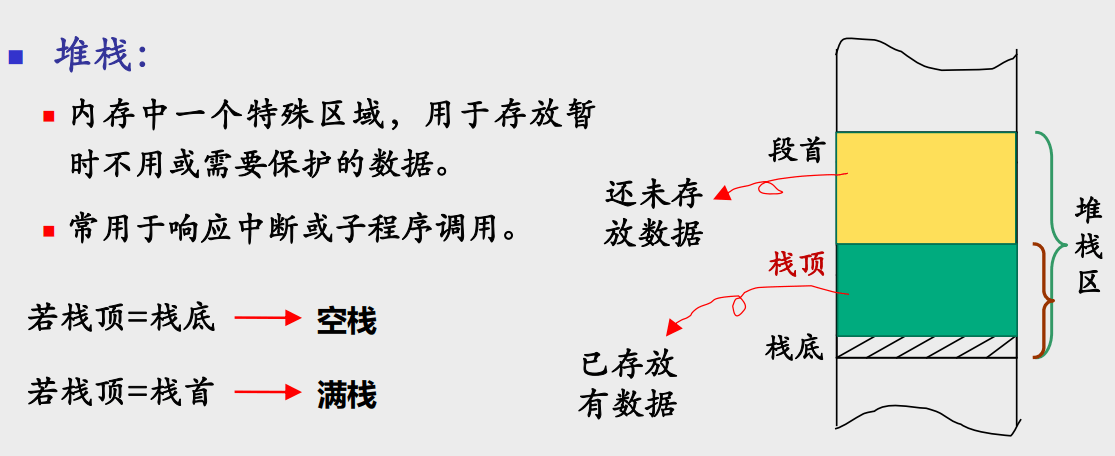

SP:堆栈指针寄存器,其内容为栈顶的偏移地址

- BP:基址指针寄存器,常用于在访问内存时存放内存单元的偏移地址。

BX 与 BP 在应用上的区别:

- 作为通用寄存器,二者均可用于存放数据;

作为基址寄存器,用 BX 表示所寻找的数据在数据段;用 BP 则表示数据在堆栈段。

变址寄存器

SI:源变址寄存器

- DI:目标变址寄存器

-

控制寄存器

IP:指令指针寄存器,其内容为下一条要取的指令的偏移地址

FLAGS:标志寄存器,存放运算结果的特征

CF(Carry Flag)

- 进位标志位。加 (减) 法运算时,若最高位有进 (借) 位则 CF=1

- PF(Parity Flag)

- 奇偶标志位。运算结果的低 8 位中 “1” 的个数为偶数时 PF=1

- AF(Auxiliary Carry Flag)

- 辅助进位标志位。加 (减) 操作中,加减法做到一半时有没有形成进位 / 借位,如果有则 AF=1

- ZF(Zero Flag)

- 零标志位。当运算结果为零时 ZF=1

- SF(Sign Flag)

- 符号标志位。当运算结果的最高位为 1 时,SF=1

OF(Overflow Flag)

TF(Trap Flag)

- 陷阱标志位,也叫跟踪标志位。TF=1 时,使 CPU 处于单步执行指令的工作方式。

- IF(Interrupt Enable Flag)

- 中断允许标志位。IF=1 使 CPU 可以响应可屏蔽中断请求。

DF(Direction Flag)

作用

- 用于存放相应逻辑段的段基地址

- 8086/8088 内存中逻辑段的类型

- 代码段 —— 存放指令代码

- 数据段 —— 存放操作的数据

- 附加段 —— 存放操作的数据

- 堆栈段 —— 存放暂时不用但需保存的数据。

- CS

- 代码段寄存器,存放代码段的段基地址。

- DS

- 数据段寄存器 ,存放数据段的段基地址。

- ES

- 附加段寄存器,存放数据段的段基地址。

SS

内存分段管理思想

- 实地址模式下的内存地址变换

- 段寄存器的应用

-

内存储器管理

8088 CPU 是 16 位体系结构的微处理器

- 可以同时处理(产生)16 位二进制码

- 直接管理 64K 个内存单元

如何使 8088 CPU 管理 1MB 内存

物理地址:每个内存单元在整个内存空间中的唯一地址

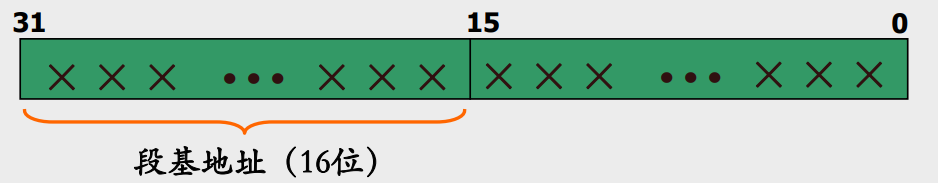

内存地址变换:将 32 位的逻辑地址 (段基地址+偏移地址) 变换为 20 位物理地址

内存单元的编址

内存每个单元的地址在逻辑上都由两部分组成:

- 段 (基) 地址

- 指示存储单元在整个内存空间中处于哪个区域 (段)

- 段内地址 (相对地址 / 偏移地址)

- 指示存储单元在段中的相对位置 (与段中第 1 个单元的距离)

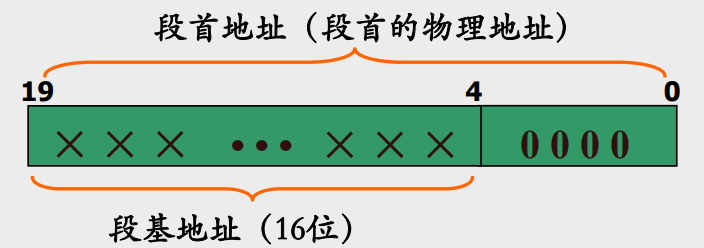

- 逻辑段的起始地址称为段首

- 每个逻辑段内的第一个单元

- 由偏移地址的定义得:段首的偏移地址为 0

- 段 (基) 地址

由于段首的偏移地址为 0,所以将后 16 位 0 写为 4 位 0,这样 16 位段基地址加上 4 位偏移地址构成 20 位的物理地址

物理地址 = 段基地址 × 16+偏移地址

-

逻辑段

【例】1M 的内存空间需要 20 位的地址来管理,而 8088 是 16 位的体系结构,能够管理的内存空间是 64K,现在想让 8088CPU 能够管理 1M 大小的内存空间,就需要对内存空间进行分段。

物理分段的话,1M 的内存空间可以分为 16 个 64K 大小的内存空间,也就是将 1M 的内存空间分为 16 个物理上的内存段

- 物理分段可能会造成内存空间的浪费,所以我们在内存管理上常采用逻辑分段的方式

- 逻辑分段可以根据需要不断调整段的大小,同一块内存区域在不同的时间点可以属于不同的程序,也叫分时复用。逻辑段并不是物理上真实存在的段,而是逻辑上的段

由于段基地址有 16 位,所以在逻辑层面上内存空间最多可以分为 64K 个逻辑段

段寄存器

作用:用于存放相应逻辑段的段基地址

- 8088/8086 内存中逻辑段可以有 64K 个,它们可以分为四种类型

- 代码段 —— 存放指令代码

- 数据段 —— 存放操作的数据

- 附加段 —— 存放操作的数据

- 堆栈段 —— 存放暂时不用但需保存的数据,比如子函数调用等

- 8086/8088 内存中每类逻辑段的数量

- 最多为 64K 个

- 四种类型的逻辑段对应着四个段寄存器。段寄存器的值表明相应逻辑段的段基地址在内存中的位置:

- CS:代码段寄存器,存放代码段的段基地址。

- DS:数据段寄存器 ,存放数据段的段基地址。

- ES:附加段寄存器,存放数据段的段基地址。

- SS:堆栈段寄存器, 存放堆栈段的段基地址

- 每个程序最多只能分为 4 段

【例 1】已知数据的段基地址和偏移地址,计算该数据所在内存单元的物理地址

- 问:设某操作数存放在数据段,DS=250AH,数据所在单元的偏移地址 = 0204H。

答:则该操作数所在单元的物理地址为:

内存的分段是逻辑分段,不是物理段。各个逻辑段在地址上可以不相连、可以部分重合,也可以完全重合。

- 每个内存单元具有唯一物理地址,但可能具有多个逻辑地址。即:

- 一个内存单元可以同时处于两个逻辑段

- 一个内存单元可以在不同的时刻属于相同 (或不同) 类型的段

- 一个内存单元在同一时刻可以属于不同类型的段

- 同一程序模块装入内存时,不同类型的段可以装入在相同 / 不同的物理空间

- 两个逻辑段完全重合或部分重合

两个不同的程序模块装入内存时, 同一类型的逻辑段也可以装入相同或不同的物理空间中

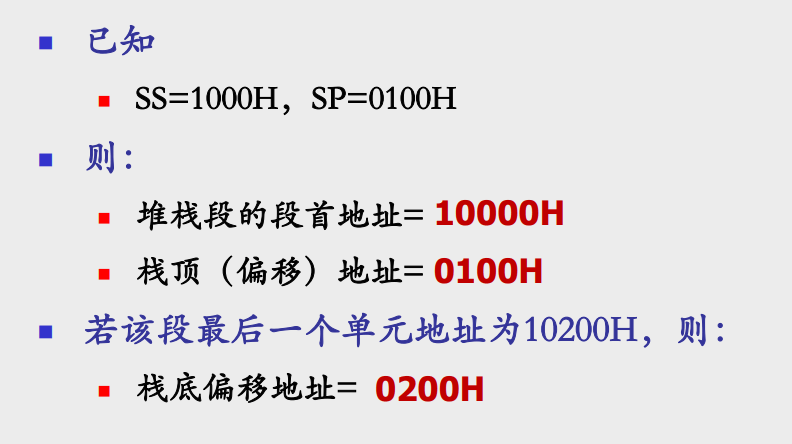

堆栈及堆栈段的使用

【例】已知段基地址 1000H 和物理地址 10200H,求偏移地址

偏移地址 = 物理地址 - 段基地址 × 16

10200H - 1000H × 16 = 10200H - 10000H = 0200H

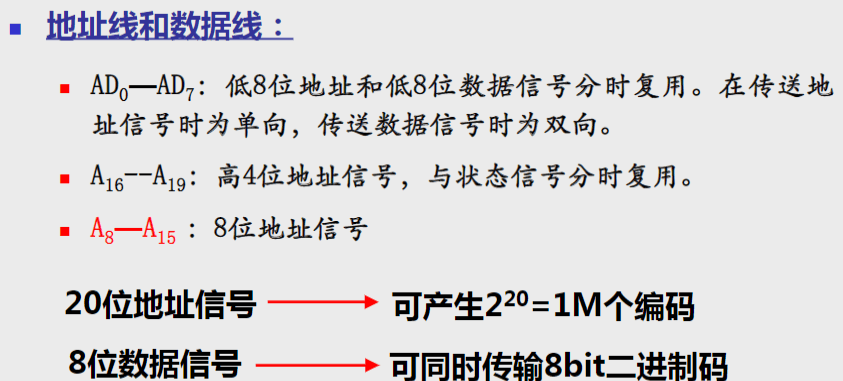

8088 系统总线

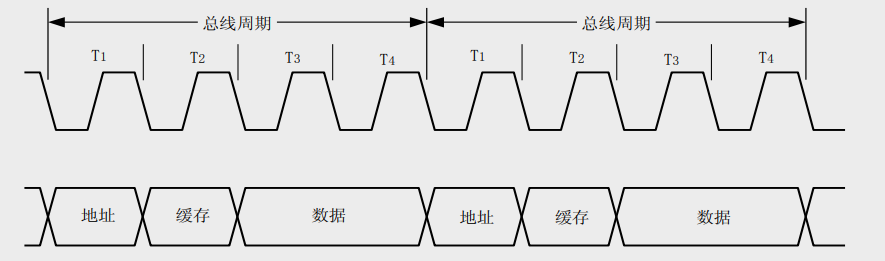

CPU 工作时序:

- CPU 各引脚信号在时间上的关系

- 总线周期:

- CPU 完成一次访问内存(或接口)操作所需要的时间。

- 一个总线周期至少包括 4 个时钟周期。

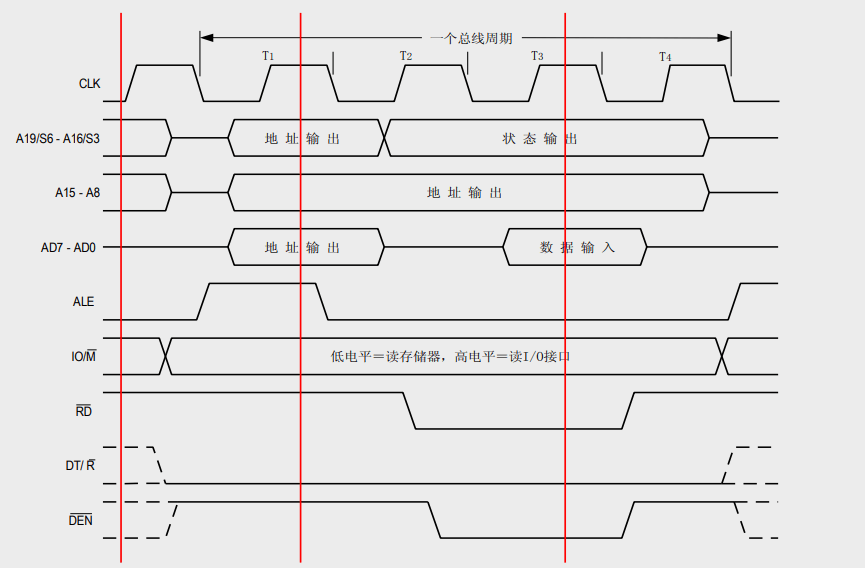

总线的工作时序图

【例】8088 最小模式下的读总线周期的工作时序

- 横坐标是时间轴,纵坐标是各个引脚信号的幅值

- 竖着看时序图,各个时刻,每个引脚信号的信息

- CLK:时钟信号,CPU 工作基准时间

- A19/S6-A16/S3:总线信号,4 根信号线的集合,高 4 位地址信号状态信号分时复用,这里只关心它的状态是否有效;鼓起来表示有效,凹下去表示无效

- AD7-AD0:低 8 位地址和低 8 位数据信号分时复用。在传送地址信号时为单向,传送数据信号时为双向

- IO/#M:是一根信号线,有两种可能的状态 (高电平和低电平)

- 在第一个时间点 (第一条红线)

- 各个信号都处于无效状态,也就是之前的随机状态

在第二个时间点 (第二条红线)

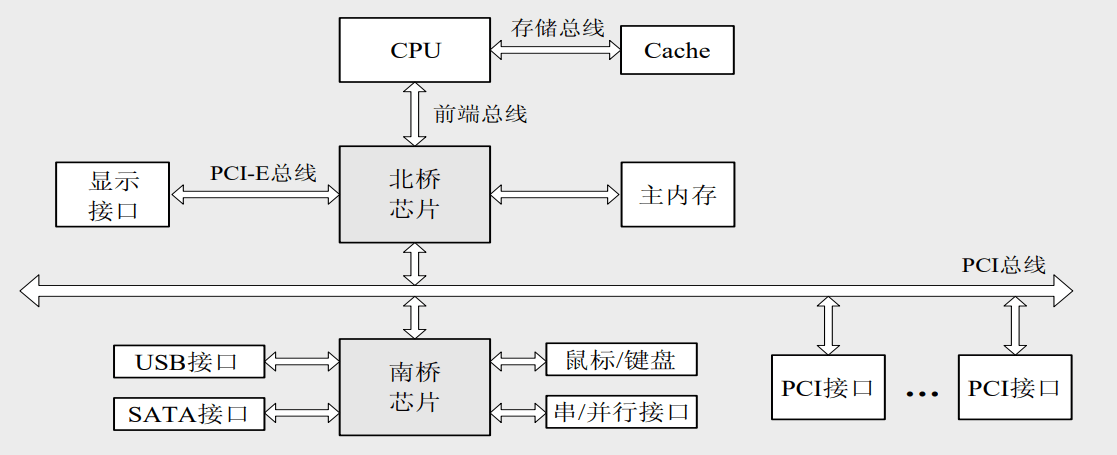

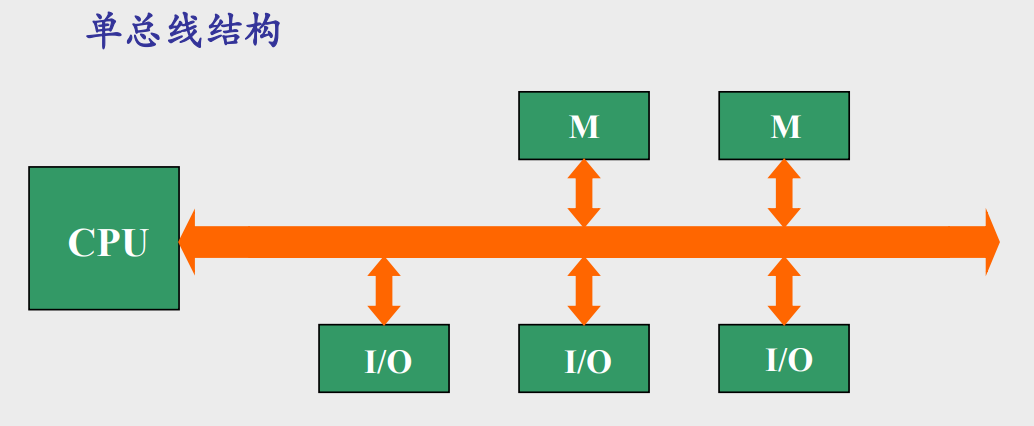

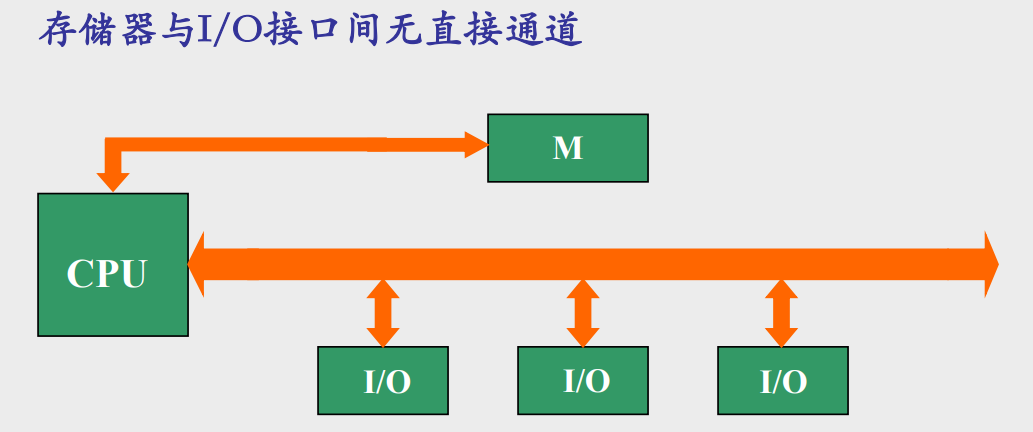

是一组导线和相关的控制、驱动电路的集合。是计算机系统各部件之间传输地址、数据和控制信息的通道。

总线分类

按传输的数据类型可分为三类:

- 地址总线 (AB)

- 数据总线 (DB)

- 控制总线 (CB)

按层次结构分为

单总线结构

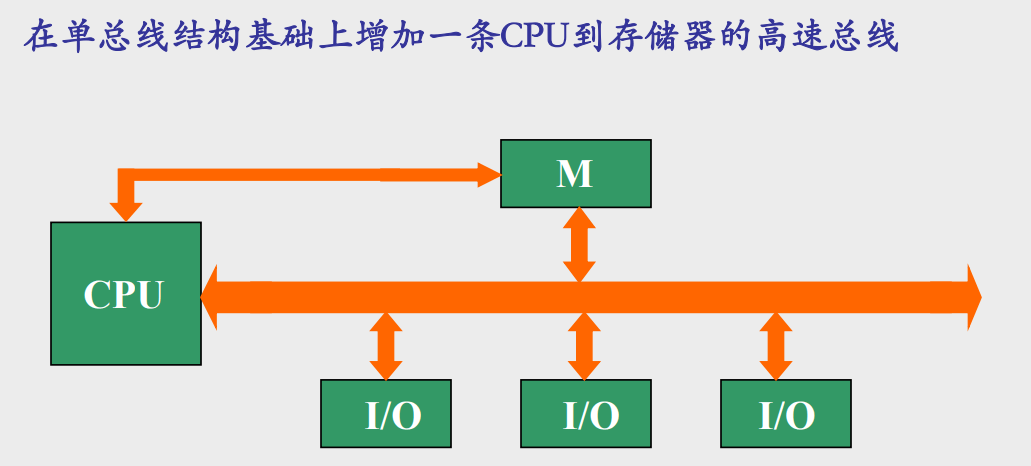

- 双总线结构

- 面向 CPU 的双总线结构

- 面向主存的双总线结构

- 多总线结构

总线功能

- 数据传送

- 仲裁控制

- 出错处理

-

总线性能指标

总线带宽 (B/S)

- 单位时间内总线上可传送的数据量

- 总线带宽 = 位宽 × 工作频率

- 总线位宽 (bit)

- 能同时传送的数据位数

- 总线的工作频率 (MHz)

- 总线带宽 = (位宽 / 8) × ( 工作频率 / 每个存取周期的时钟数 )

有关总线的更多内容可见计算机组成原理——总线系统:传送门