- Storage Capacitor

- Storage Capacitor,即存储电容,它通过存储在其中的电荷的多和少,或者说电容两端电压差的高和低,来表示逻辑上的 1 和 0。

- Access Transistor,即访问晶体管,它的导通和截止,决定了允许或禁止对 Storage Capacitor 所存储的信息的读取和改写。

- Wordline,即字线,它决定了 Access Transistor 的导通或者截止。

- Bitline,即位线,它是外界访问 Storage Capacitor 的唯一通道,当 Access Transistor 导通后,外界可以通过 Bitline 对 Storage Capacitor 进行读取或者写入操作。

1.1 数据读写原理

- 读数据时,Wordline 设为逻辑高电平,打开 Access Transistor,然后读取 Bitline 上的状态

- 写数据时,先把要写入的电平状态设定到 Bitline 上,然后打开 Access Transistor,通过 Bitline 改变 Storage Capacitor 内部的状态。

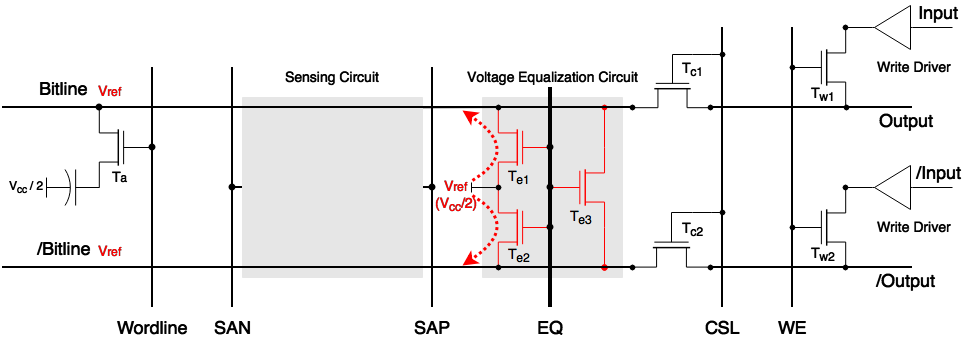

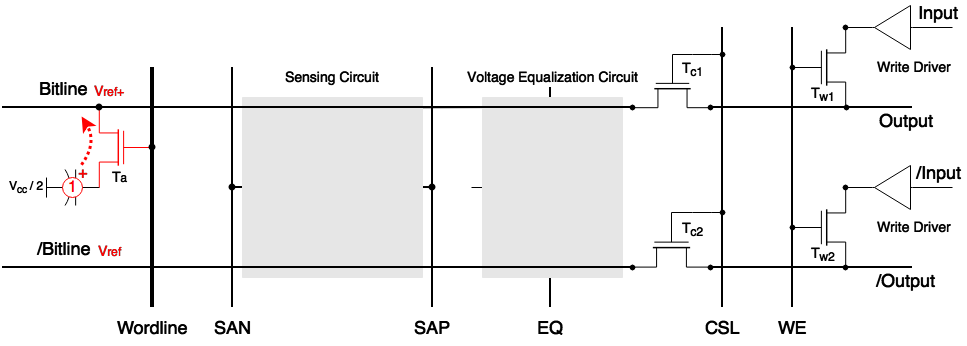

- Differential Sense Amplifier

2.1 Read Operation

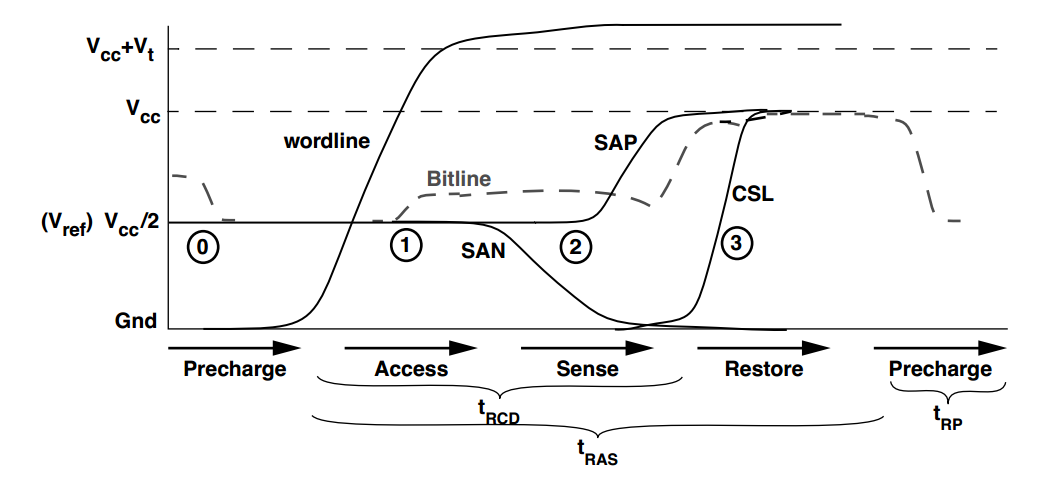

2.1.1 Precharge

2.1.2 Access

2.1.3 Sense

2.1.4 Restore

2.1.5 Timing

- Write Operation

3.1 Write Recovery

- 参考资料

- Memory Systems - Cache Dram and Disk

原创文章,转发请注明出处。蜗窝科技