alias: spacer,side wall

tag:

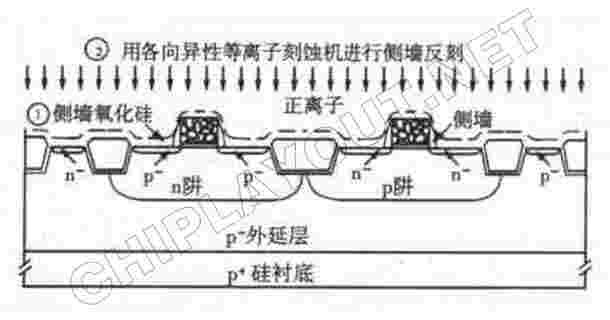

为了防止大剂量的源漏注入过于接近沟道,从而导致沟道过短甚至源漏连通,在 CMOS 的 LDD 注入之后要在多晶硅栅的两侧形成侧墙。侧墙的形成主要有两步:

- 在薄膜区利用化学气相淀积设备淀积一层二氧化硅。

- 然后利用干法刻蚀工艺刻掉这层二氧化硅。

由于所用的各向异性,刻蚀工具使用离子溅射掉了绝大部分的二氧化硅,当多晶硅露出来之后即可停止反刻,但这时并不是所有的二氧化硅都除去了,多晶硅的侧墙上保留了一部分二氧化硅。这一步是不需要掩膜。

- CMOS 制作基本步骤的相关文章

- CMOS 制作步骤(一):双阱工艺(twin well process)

- CMOS 制作步骤(二):浅槽隔离工艺 STI(shadow trench isolation process)

- CMOS 制作步骤(三):多晶硅栅结构工艺 (poly gate structural process)

- CMOS 制作步骤(四):轻掺杂漏注入工艺 LDD(lightly doped drain implants process)

- CMOS 制作步骤(五):侧墙的形成(side wall spacer formation)

- CMOS 制作步骤(六):源 / 漏注入工艺(S/D implant process)

- CMOS 制作步骤(七):接触(孔)形成工艺(contact formation)

- CMOS 制作步骤(八):局部互连工艺 LI(Local Interconnect process)

- CMOS 制作步骤(九):Via-1, Plug-1 及 Metal-1 互连的形成(Via-1 and Plug-1 formation)

- CMOS 制作步骤(十):Via-2, Plug-2,Metal-2 及 Top Metal 形成(Via-2,Plug-2,metal2 interconnect and top metal formation)

转载自网络的内容未用作任何商业用途,如有侵权请告知删除!本站的原创文章请在转载时注明来源 <《芯片版图》本文链接:https://www.chiplayout.net/cmos-formation-side-wall.html订阅本站:https://www.chiplayout.net隐私政策:https://www.chiplayout.net/privacy-policy

分类 Process