本文由 简悦 SimpRead 转码, 原文地址 www.wowotech.net

作者:codingbelief 发布于:2016-7-27 22:12 分类:基础技术

DRAM 原理 3 :DRAM Device

作者:codingbelief 发布于:2016-7-27 22:12 分类:基础技术

相关文章:

DRAM 原理 2 :DRAM Memory Organization

DRAM 原理 5 :DRAM Devices Organization

- SDRAM Interface

| Symbol | Type | Description |

|---|---|---|

| CLK | Input | 从 Host 端输出的同步时钟信号 |

| CKE | Input | 用于指示 CLK 信号是否有效,SDRAM 会根据此信号进入或者退出 Power down、Self-refresh 等模式 |

| CS# | Input | Chip Select 信号 |

| CAS# | Input | Column Address Strobe,列地址选通信号 |

| RAS# | Input | Row Address Strobe, 行地址选通信号 |

| WE# | Input | Write Enable,写使能信号 |

| DQML | Input | 当进行写数据时,如果该 DQML 为高,那么 DQ[7:0] 的数据会被忽略,不写入到 DRAM |

| DQMH | Input | 当进行写数据时,如果该 DQMH 为高,那么 DQ[15:8] 的数据会被忽略,不写入到 DRAM |

| BA[1:0] | Input | Bank Address,用于选择操作的 Memory Bank |

| A[12:0] | Input | Address 总线,用于传输行列地址 |

| DQ[15:0] | I/O | Data 总线,用于传输读写的数据内容 |

1.1 SDRAM Operations

| Command | CS# | RAS# | CAS# | WE# | DQM | BA[1:0] & A[12:0] | DQ[15:0] |

|---|---|---|---|---|---|---|---|

| Active | L | L | H | H | X | Bank & Row | X |

| Read | L | H | L | H | L/H | Bank & Col | X |

| Write | L | H | L | L | L/H | Bank & Col | Valid |

| Precharge | L | L | H | L | X | Code | X |

| Auto-refresh | L | L | L | H | X | X | X |

| Self-refresh | L | L | L | H | X | X | X |

| Load Mode Register | L | L | L | L | X | REG Value | X |

1.1.1 Active

1.1.2 Read

1.1.3 Write

1.1.4 Precharge

1.1.5 Auto-Refresh

1.1.6 Self-Refresh

1.2 Address Mapping

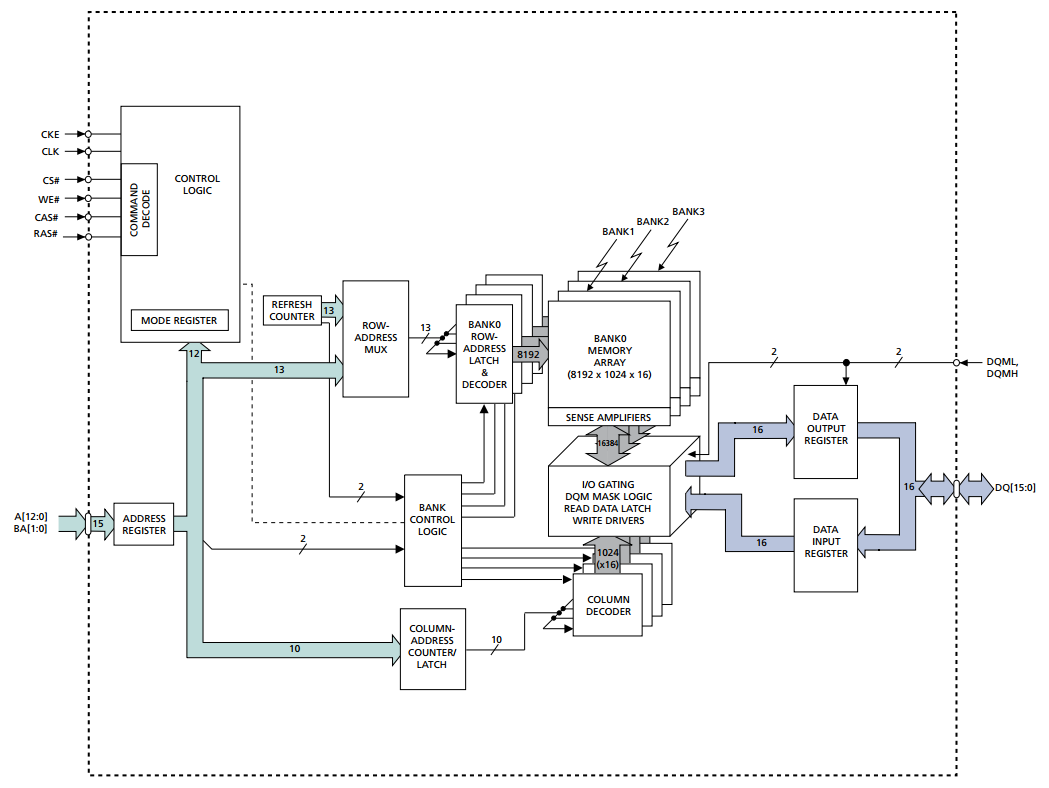

- SDRAM 内部结构

2.1 Control Logic

2.2 Row & Column Decoder

2.3 Memory Array

2.4 IO

2.5 Refresh Counter

- 不同类型的 SDRAM

3.1 SDR 和 DDR

| DDR SDRAM Standard | Bus clock (MHz) | Internal rate (MHz) | Prefetch (min burst) | Transfer Rate (MT/s) | Voltage |

|---|---|---|---|---|---|

| DDR | 100–200 | 100–200 | 2n | 200–400 | 2.5/2.6 |

| DDR2 | 200–533.33 | 100–266.67 | 4n | 400–1066.67 | 1.8 |

| DDR3 | 400–1066.67 | 100–266.67 | 8n | 800–2133.33 | 1.5 |

| DDR4 | 1066.67–2133.33 | 133.33–266.67 | 8n | 2133.33–4266.67 | 1.05/1.2 |

3.2 LPDDRx

3.3 GDDRx

- 参考资料

- Memory Systems - Cache Dram and Disk

- 大容量 DRAM 的刷新开销问题及优化技术综述 [PDF]

- Micron Technical Note - General DDR SDRAM Functionality [PDF]

- Everything You Need To Know About DDR, DDR2 and DDR3 Memories [WEB]

- 記憶體 10 年技術演進史 [WEB]