5.1 PLD的基本概念

可编程阵列

什么是PLD

PLD是用户根据需要自行设计芯片中特定逻辑电路的器件。所有的PLD都是由可编程阵列组成。

所谓可编程阵列是行列导线组成的导电网格。在网格的交叉线上通过熔断金属丝或者E**2**COMS管等连接技术来实现逻辑1或者0.

与阵列

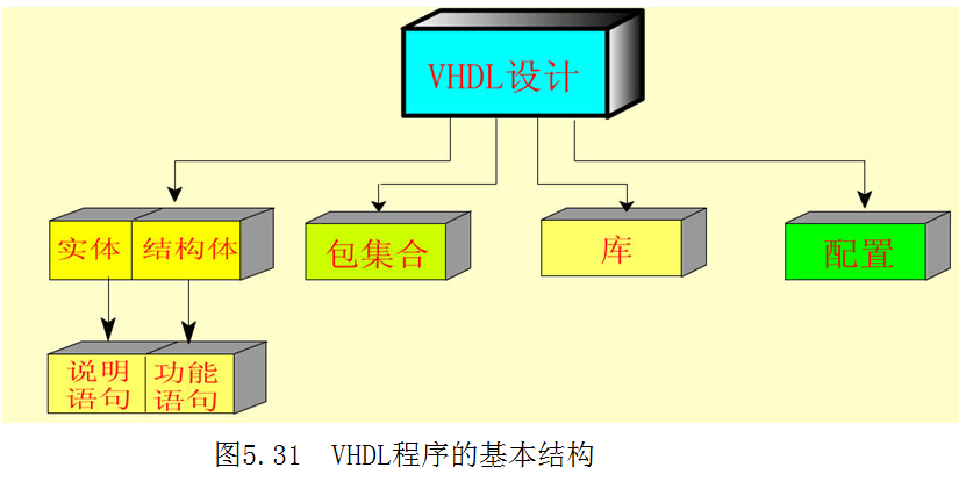

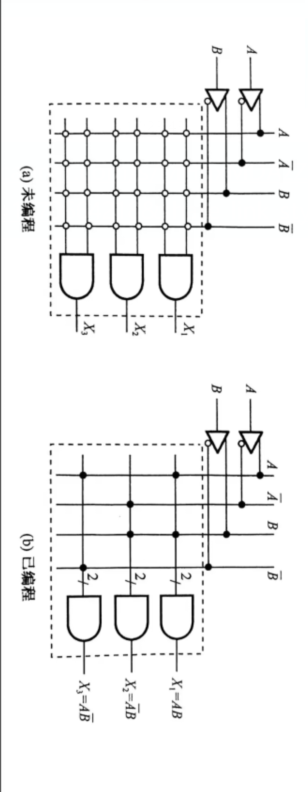

如图所示,就是一种与阵列,输入端是A和B,输出端是X1、X2、X3。

为什么被称为可编程阵列?原因在于如图(a)所示,导电网格导通了所有输入的可能性,只需要每一行保留需要的网格点,就可以实现自我调节最终的输出,例如图(b)。

注意这里的图(b),这里再与门输入前有个2,表示这是一个

**2输入与门**。

或阵列

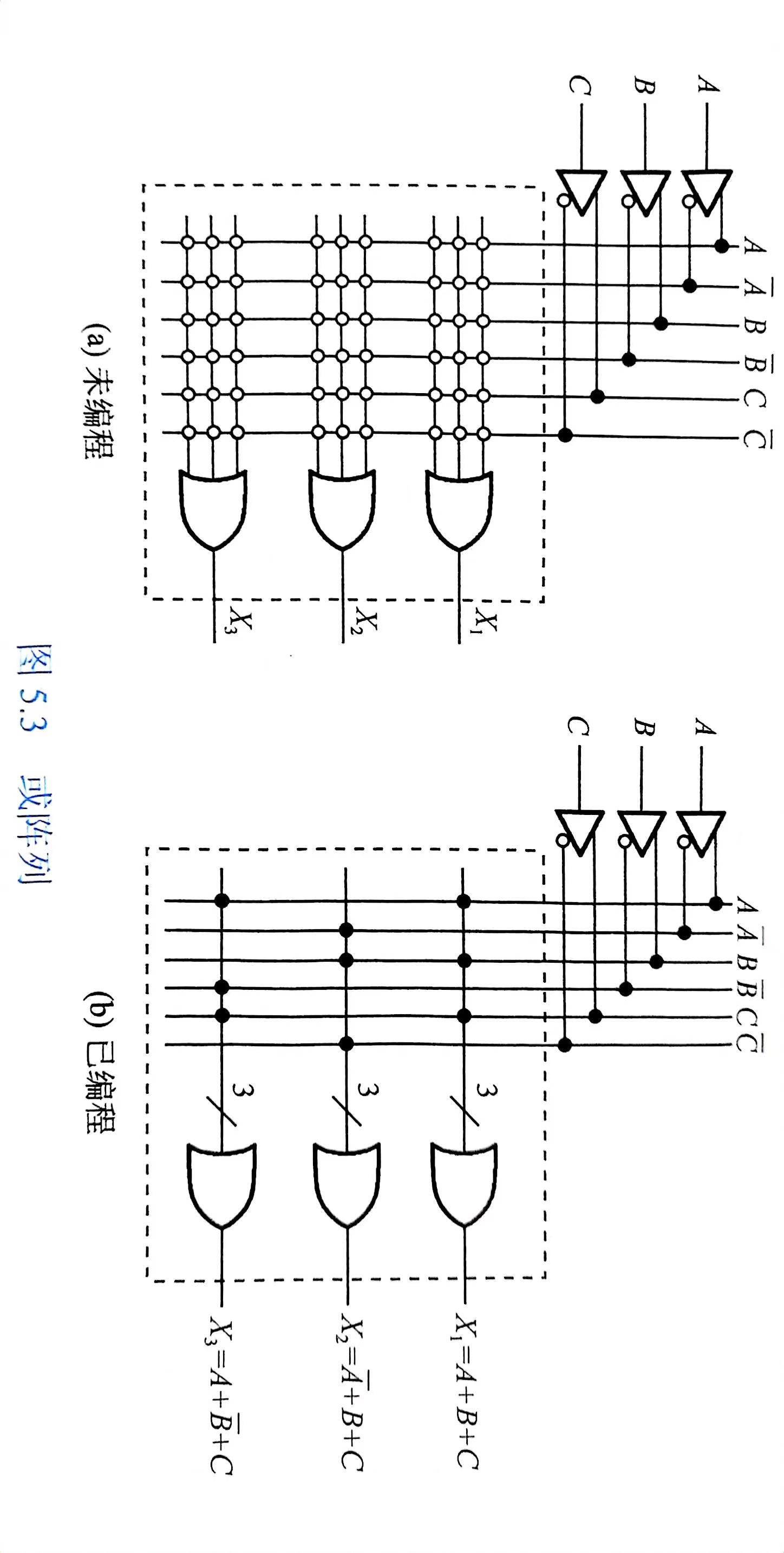

如图所示:

解析一下这里的X输出。在每一行交叉处有黑点的就表示一个输入,比如第一行中,A、B、C是有黑点标注的,所以最终X1的输出为A + B + C。

可编程连接技术

连接技术有以下4种:

熔丝技术:编程之前,熔丝通连接(原始),状态称为逻辑1 ;对选定熔丝熔断后的状态称为逻辑0。非易失。反熔丝技术:这种连接与熔丝连接正好相反,不是破坏连接,而是建立连接。非易失。E2PROM技术:加电的方式可以擦除或重写,ISP在系统编程SRAM技术:SRAM存储元通过将触发器实现连接、断开。易失,每次加电,PLD编程数据必须重新写入。PLD的类型

PLD的类型主要有两种:

简单可编程逻辑器件SPLD

- PROM:一次可编程制度存储器

- PAL:可编程阵列逻辑

- PLA:可编程阵列逻辑

- GLA:通用阵列逻辑

- 复杂可变成功逻辑器件CPLD

本质上CPLD是**利用可编程的互连总线连接起来的多路SPLD。