内容和参考

内容

学习RISC-V的基础知识,包含:

- RISC-V的发展历史 和 现状

- RISC-V的产品评估

相关资料

- RISC-V官网 : 提供了 官方标准手册 等内容

- RSIC-V core-socs : RISC-V生态系统中可用的知识产权(IP)内核和SoC的集合

RISC-V的历史

就像 诗词一样,我们需要了解历史 以及 作者当时的情况,才更能体会到作者 写诗词的心态以及想表达的内容;

同样,了解一个物品的发展历史,才能对这个事情有更透彻的理解,所以这里先学习下RISC-V的发展历史:

参考: RISC-V学习总结之历史与现状

RISC-V指令集现状介绍

参考: 计算机体系架构基础 -RISC-V 指令集现状介绍

RISC-V 的官网为www.riscv.org

在2018年前后,众所周知的RISC-V指令集可分为:IMACFD

- I 整型基本指令集

- M 乘除基本指令集

- A 原子操作指令集

- C 压缩指令集

- F 单精度浮点指令集

- D 双精度浮点指令集

经过这几年开源工作组的推动,目前RISC-V指令集的发展现状为:

注:

状态:(Ratified-已发布,Draft-草案 )

| 指令类型 | 指令集 | 版本 | 状态 | 描述 | 网址 |

|---|---|---|---|---|---|

| 整型基本指令集 I-必须实现一种 | RV32E | v1.9 | Draft | 32-bit基本整型指令集(16个寄存器) | https://github.com/riscv/riscv-isa-manual |

| RV32I | v2.1 | Ratified | 32-bit基本整型指令集 | ||

| RV64I | v2.1 | Ratified | 64-bit基本整型指令集 | ||

| RV128I | v1.7 | Draft | 128-bit基本整型指令集 | ||

| 内存模型-必有 | RVWMO | v2.0 | Ratified | RISC-V 内存模型 | |

| MACFD指令集 | M | v2.0 | Ratified | 乘除指令集 | |

| A | v2.1 | Ratified | 原子操作指令集 | ||

| C | v2.0 | Ratified | 压缩指令集 | ||

| F | v2.2 | Ratified | 单精度浮点指令集 | ||

| D | v2.2 | Ratified | 双精度浮点指令集 | ||

| Q | v2.2 | Ratified | 四精度浮点指令集 | ||

| Zicsr | v2.0 | Ratified | CSR 访问指令集,从I指令集分离 | ||

| Zifencei | v2.0 | Ratified | ICache 与DCache 同步指令集,从I指令集分离 | ||

| Counter | v2.0 | Ratified | 读取架构计数器指令集,从I指令集分离 | ||

| USHM四种模式 | M-Mode | v1.11 | Ratified | RISC-V 特权模式Machine-Mode | |

| S-Mode | v1.11 | Ratified | RISC-V 特权模式SuperVisor-Mode | ||

| H-Mode | v0.6.1 | Draft | RISC-V 特权模式Hypervisor-Mode | ||

| U-Mode | RISC-V 非特权模式User-Mode | ||||

| V | v0.10 | Draft | Vector 指令集 | https://github.com/riscv/riscv-v-spec | |

| B | v0.93 | Draft | 比特操作指令集 | https://github.com/riscv/riscv-v-spec | |

| P | Draft | Pack-SIMD 指令集 | https://github.com/riscv/riscv-p-spec | ||

| J | Draft | 动态翻译语言指令集 | https://github.com/riscv/riscv-j-extension | ||

| Debug | v1.0 | Ratified | RISC-V Debug 架构 | https://github.com/riscv/riscv-debug-spec | |

| Trace | v1.0 | Ratified | RISC-V Trace 架构 | https://github.com/riscv/riscv-trace-spec |

以上是指令集目前进展,这里补充几点:

基础部分:

- 在RISC-V 架构中,必须实现RV32I , RV32E, RV64I, RV128I 基本指令集的一种,以及RVWMO的内存模型;

在RISC-V指令集架构中,RV32I/RV32E, RV64I, RV128I 是互相独立的基本指令集,

不过RISCV架构也描述64位处理执行32位程序的特权架构,但是目前Linux还未对这方面进行支持;

USHM四种模式必须支持UHM三种,H-Mode(类似于ARM 的Hypervisor EL2) 将会是RISC-V走向成熟的一个标志性的标准,暂时还未发布;

- Debug和Trace架构也必须支持,调试用;

- C指令集提高了RISC-V指令的代码密度,但是目前仍然有很多工程师在评估RISC-V时,觉得RSICV的代码密度还是比ARM 的代码密度大,RSIC-V也有代码密度相关的组,具体在https://github.com.cnpmjs.org/riscv/riscv-code-size-reduction,希望能提供一定的帮助。

新增部分:

- V指令集和P指令集其实在一定程度上存在冲突,至于两者以后是同时存在,还是只留其一,笔者不好判断,但不管如何V指令集还是正统。

- B指令集的设计者还是挺牛逼的,把标准,电路实现和编译器的工作都做完了,且开源,省了其他人设计的功夫,但笔者个人觉得B指令集设计还是过于复杂,可以仅仅实现其中的部分指令。 听描述好像与 X86的 BSR和BSF等 bit位扫描指令一样,用来加速bitmap的查找定位;

- J指令集貌似一直没有太大的进展。

以上是指令集的相关情况,对于软硬件的实现,RISC-V也提供了相应的开源支持,希望感兴趣的读者参与,详细的信息可以查阅网址https://riscv.org/exchange

处理器:

| 处理器 | 开发语言 | 描述 | 网址 |

|---|---|---|---|

| rocket | Chisel | 5-stage 顺序流水线 | https://github.com/chipsalliance/rocket-chip |

| boom | Chisel | 乱序流水线 | https://github.com/riscv-boom/riscv-boom |

| NutShell | Chisel | 乱序流水线,由中科院”一生一芯“计划演进的高性能流水线 | https://github.com/OSCPU/NutShell |

工具链:

| 工具链 | 网址 |

|---|---|

| GCC : 编译器 | https://github.com/riscv/riscv-gcc |

| LLVM:模块化、可重用的编译器以及工具链技术的集合 | https://github.com/llvm |

仿真器:

| 仿真器 | 描述 | 网址 |

|---|---|---|

| spike | RISC-V 指令功能模拟器,但仅限于指令功能,暂时无法在上面运行Linux等操作系统 | https://github.com/riscv/riscv-isa-sim |

| qemu | RISC-V 指令功能模拟器,能够比较运行Linux等操作系统,是在没有硬件条件下,进行程序开发的最好模拟工具 | https://github.com/riscv/riscv-qemu |

操作系统:

| 操作系统 | 网址 |

|---|---|

| Linux Kernel | https://github.com/riscv/riscv-linux |

| RT-Thread | https://github.com/RT-Thread |

| LiteOS | https://github.com/LiteOS/LiteOS_Lab/ |

RISC-V当前产品评估

参考: RSIC-V core-socs - RISC-V生态系统中可用的知识产权(IP)内核和SoC的集合。

首先要排除几个大类:

- 32-bit的支持(学习用,但现在商用都是64-bit起步)

- Primary Language(这部分也不是我的专业, 但主流是 Chisel,Verilog, SystemVerilog

- Spec:商用尽可能选择非draft版本;

经过排除后, 这里选择几个市场比较主流的产品进行评估:

注:因为我是从事软件的,所以产品评估比较 关注软件部分

主要评估以下部分:生态(操作系统, 编译器, 第三方软件, 调试和跟踪等支持), CPU架构及流水线, 系统总线, 性能和功能等;

基础知识

指令流水

流水线形式 同时执行: 取指,译码,执行 (访存,回写)等处理

多发射

但是随着集成电路发展,很多人不满足这样的效率,萌生出一次我直接执行两条毫无关系的指令。也就是一次发射两条指令。多发射就是这个意思。显然生活中肯定一心不能二用,但是现在可以增加部件,也就是组装线上坐多个人也就是多条流水线,实现了多发射。

乱序执行

由于在指令在一定逻辑上只能按照顺序执行,比如疫情期间在家办公,计划的顺序是起床、等快递来送菜、做早饭、吃早饭、回复邮件、开始工作。但是快递小哥迟迟不来,咱们是不是得一直等着他来送菜再进行下面的事情?显然不会,你一定会把等菜、做饭、吃饭等一系列步骤放着,先去执行另一系列的步骤(发邮件、工作),因为这两个系列的步骤是完全不相关的。放在CPU中的逻辑时,某条指令需要访存,访存的时候多级cache不命中、内存缺页等原因导致访存时间延长,这个时候是不是也像快递小哥迟迟不来一样,这个时候咱们就要先放弃这一系列的事情,先去执行后面的与之无关指令。等访存结束再去回去执行之前被耽搁的指令,这就是乱序执行(因为指令的顺序被打乱了)。这样的代价在哪里?,为什么叫乱序执行,不叫乱序提交,那就是因为提交顺序(最后结果)必须正确,比如一个寄存器按照原本的顺序是 被改成3、3被访问、被改成5、5被访问,显然前两个跟后两个没有关系,如果出现了乱序执行,先执行了后两个,那么寄存器最后结果就是3了,后续跟这个寄存器打交道的指令都会出错(原本希望最后是5),所以提交顺序一定要正确,所以设计了保留站和ROB(重排序缓冲),那就是标记指令本来的执行顺序,在写回(最后一级流水线)的时候、如果比自己标记好小的指令不提交,自己就在ROB中呆着等待原本在自己前面的指令提交。这样就保证了既节省时间又能正确提交。

超标量

上面是说的都是一个核同时只能执行一条指令,超标量就是一个核同时可以执行多条指令。

浮点运算

FLOAS=核数单核主频CPU单个周期浮点计算值。

上述三个参数中,核数,单核主频在CPU型号都会标明,只有CPU单个周期浮点计算值: FPS的时间 这个要深入思考一下。

参考: https://software.intel.com/content/www/cn/zh/develop/articles/a-simple-example-to-measure-the-performance-of-an-intel-mkl-function.html

CPU性能评估标准及工具

Unixbench: UnixBench一个基于系统的基准测试工具,不单纯是CPU 内存 或者磁盘测试工具。测试结果不仅仅取决于硬件,也取决于系统、开发库、甚至是编译器。

MIPS: Million Instructions executed Per Second

DMIPS: Dhrystone Million Instructions executed Per Second

MFLOPS: Million Floating-point Operations Per Second

MIPS,DMIPS,MFLOPS是常用的CPU性能评估标准。注意MIPS只适合评估标量机,而MFLOPS比较适用于衡量向量机的性能。

MIPS

DMIPS

D是Dhrystone的缩写,他表示了在Dhrystone这样一种测试方法下的MIPS,Dhrystone是一种整数运算测试程序。<br /> 用DMIPS来衡量CPU性能存在很大的缺陷。DMIPS并非字面上每秒百万条指令的意思,而是运行一个叫Dhrystone的基准程序时表现出来的相对性能高低的单位,很多场合人们也习惯用MIPS作为这个性能指标的单位。因为基于程序的测试容易受到恶意优化的干扰,并且DMIPS指标值的发布不受任何机构的监督,所以使用DMIPS进行评估时要慎重。<br /> ARM一直采用比较保守的值作为CPU的DMIPS的标称值。DMIPS另外一个缺点是不能测量处理器的数字信号处理能力和Cache/MMU子系统的性能。因为Dhrystone测试程序不包含DSP表达式,只包含一些整型运算和字符串处理,并且测试程序偏小,几乎可以完整地放在Cache里面运行而无需与外部存储器进行交互。这样就难以反映处理器在一个真实系统中的真正性能。<br /> DMIPS的计算方法:Dhrystone tries to represent the result more meaningfully than MIPS (million instructions per second), because MIPS cannot be used across different instruction sets (e.g. RISC vs. CISC) for the same computation requirement from users. Thus, the main score is just Dhrystone loops per second. Another common representation of the Dhrystone benchmark is the DMIPS - Dhrystone MIPS - obtained when the Dhrystone score is divided by 1,757 (the number of Dhrystones per second obtained on the VAX 11/780, nominally a 1 MIPS machine).<br /> 对于同一个计算程序,在不同的指令集(如CISC和RISC)的机器上所产生的指令数是不一样的,此时用MIPS来比较就失去意义了,而用DMIPS来比较就有意义。在同相同指令集的机器上所产生的指令数是一样(当然编译器和libc也是一样的情况下),用MIPS来比较就有意义。

MFLOPS

是一种**基于浮点运算的CPU测试程序,当然,这种测试的结果也以 MFLOPS来加以表示,代表了CPU处理浮点运算的能力**。

总结

CPU性能评估采用综合测试程序,较流行的有**Whetstone 和 Dhrystone 两种。**[**Dhrystone**](https://www.cnblogs.com/henjay724/p/10856831.html)**/[Coremark](https://www.cnblogs.com/ImagineMiracle-wxn/p/CPU_CoreMark_test.html)主要用于测整数计算能力,计算单位就是DMIPS。采用Whetstone 主要用于测浮点计算能力,计算单位就是MFLOPS。**

常见芯片的跑分结果

Roy Longbottom的网站收集记录了很多款处理器的Dhrystone跑分结果 : http://www.roylongbottom.org.uk/dhrystone%20results.htm#anchorAndroid

EEMBC已经上传了592款型号的微控制器CoreMark跑分结果,可以在EEMBC的coremark/scores

公司及产品信息

就目前市场比较主流的RISC-V研发公司和产品简单介绍和了解下,主要参考: RISC-V学习总结之历史与现状

ARM

因为现在移动端的市场主体就是ARM,也在过去很多年都占有老大的地位;

RISC-V作为新兴产品,暂时只能主打:性价比,开源,不牵扯到政治因素,贸易战等优势,来逐步去替代一些市场,

所以对比都以ARM的IP为基准进行比较,这里先简单说下ARM的产品:

Cortex-M/A/R本质区别:

我们都知道Cortex-M, Cortex-A, Cortex-R 应用在不同场景,但Cortex-M, Cortex-A, Cortex-R架构本质区别是什么?

以下三段转载自《ARM Cortex-M处理器入门》A系列:

- Application Processors(应用处理器)–面向移动计算,智能手机,服务器等市场的的高端处理器。这类处理器运行在很高的时钟频率(超过1GHz),支持像Linux,Android,MS Windows和移动操作系统等完整操作系统需要的内存管理单元(MMU)。 如果规划开发的产品需要运行上述其中的一个操作系统,你需要选择ARM 应用处理器。

- R系列:Real-time Processors(实时处理器)–面向实时应用的高性能处理器系列,例如硬盘控制器,汽车传动系统和无线通讯的基带控制。多数实时处理器不支持MMU,不过通常具有MPU、Cache和其他针对工业应用设计的存储器功能。实时处理器运行在比较高的时钟频率(例如200MHz 到 >1GHz ),响应延迟非常低。虽然实时处理器不能运行完整版本的Linux和Windows操作系统,但是支持大量的实时操作系统(RTOS)。

- M系列:Microcontroller Processors(微控制器处理器)–微控制器处理器通常设计成面积很小和能效比很高。通常这些处理器的流水线很短,最高时钟频率很低(虽然市场上有此类的处理器可以运行在200Mhz之上),不支持MMU。 并且,新的Cortex-M处理器家族设计的非常容易使用。因此,ARM 微控制器处理器在单片机和深度嵌入式系统市场非常成功和受欢迎。

所以,ARM的Cortex系列对不同市场的产品,硬件部分有了一定的调整,主要包括:

| 比较内容 | Cortex-A | Cortex-R | Cortex-M |

|---|---|---|---|

| 是否支持MMU | 支持,可选关闭 | 不支持 | 不支持 |

| 时钟 | 非常高 >1GHz | 频率较高 200MHZ-1GHZ | 频率很低 200MHz左右 |

| 面积 | 很大 | 较大 | 面积很小和能效比很高 |

| 流水线 | 流水线级别高 | 流水线很短 |

其实,Cortex-A系列可以完成Cortex-R和Cortex-M的工作, 只要把MMU关闭就可以,不过性价比 和 面积占比、功耗等 来说比较差;

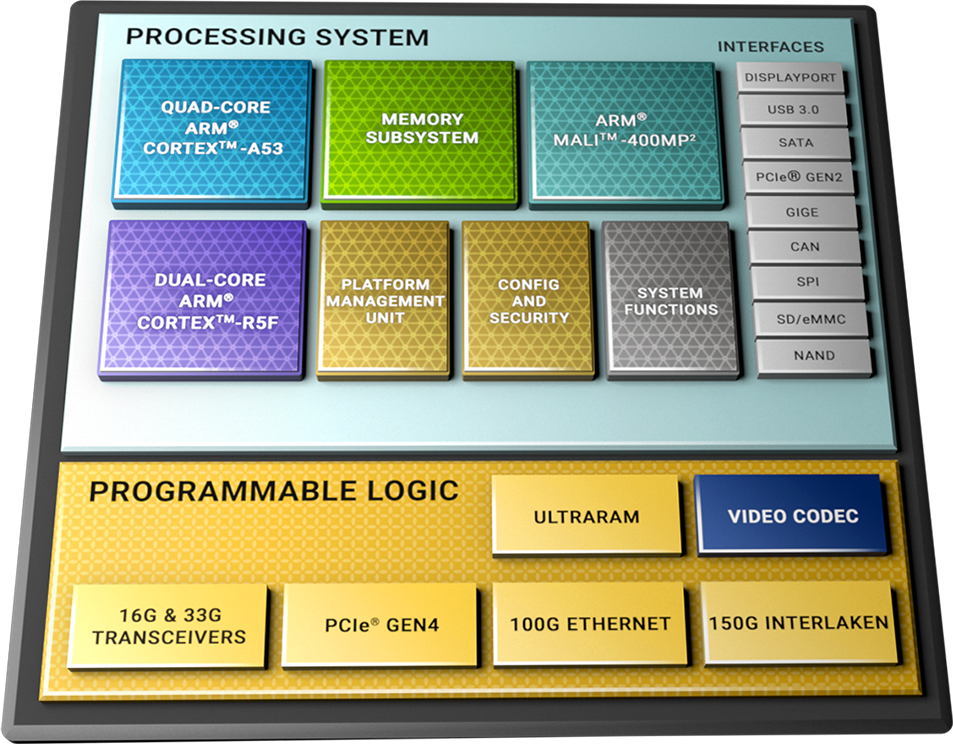

因此 ARM有了以下集成:

异构处理器

STM32MP157 是 ST公司首个 异核架构的处理器,包含两个Cortex-A内核和一个Cortex-M内核。是一款具有Arm Dual Cortex-A7 800 Mhz、Arm Cortex-M4实时协处理器、3D GPU、TFT/MIPI DSI显示器和FD-CAN的MPU。

zynqmp ultrascale+ 也采用了 将 Cortex-A53和 Cortex-R系列集成到一起的异构处理器;

big.LITTLE 设计

现在的处理器因为功能的复杂,都支持了多核SMP;

但 使用同样处理器的多核在实际场景中,有点 大材小用; 无论什么任务,都是主处理器来处理;

因此,有了big.LITTLE设计:big.LITTLE 处理的设计旨在为适当的作业分配恰当的处理器。

比如,多核中 有 Cortex-A78处理高性能任务, Cortex-A53处理调度等任务;

SiFive和StarFive

相关参考:

- 官网:https://www.sifive.com/documentation

- 官网提供的IP:SiFive Core IP

- 官网调试方式 insight: SiFive Insight

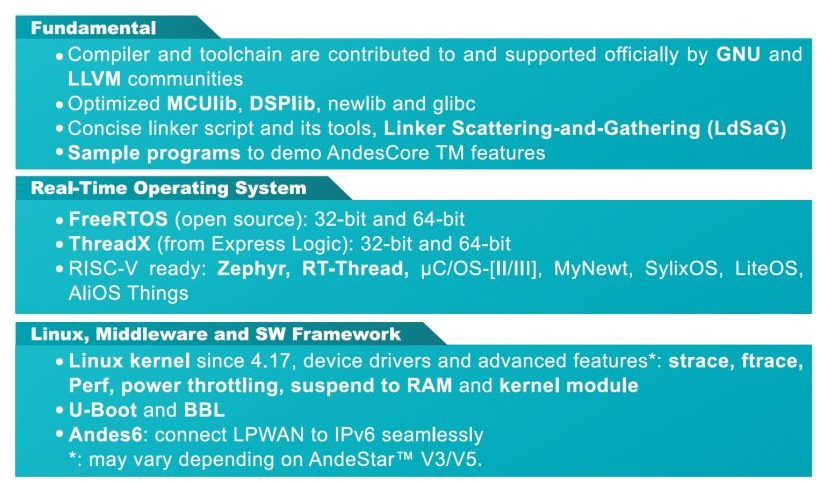

- 官网提供生态: Software

2015年,3名RISC-V发明者创办SiFive公司,SiFive联合以google为首的公司作为创始会员创立RISC-V基金会,这三位大佬同时创造了Chisel语言(Constructing Hardware in a Scala Embedded Language,硬件构建语言);同时, RISC-V基金会也是 RISC-V标准的指定者;

SiFive是2015年7月由RISC-V发明者创立的用于推动RISC-V商业化的公司。SiFive是SaaS(Software-as-a-Service)服务商,提供基于RISC-V指令集架构的商业化处理器IP、开发工具和芯片解决方案。

2018年8月在中国注册独立公司 赛昉科技(StarFive)用于为国内客户提供服务。

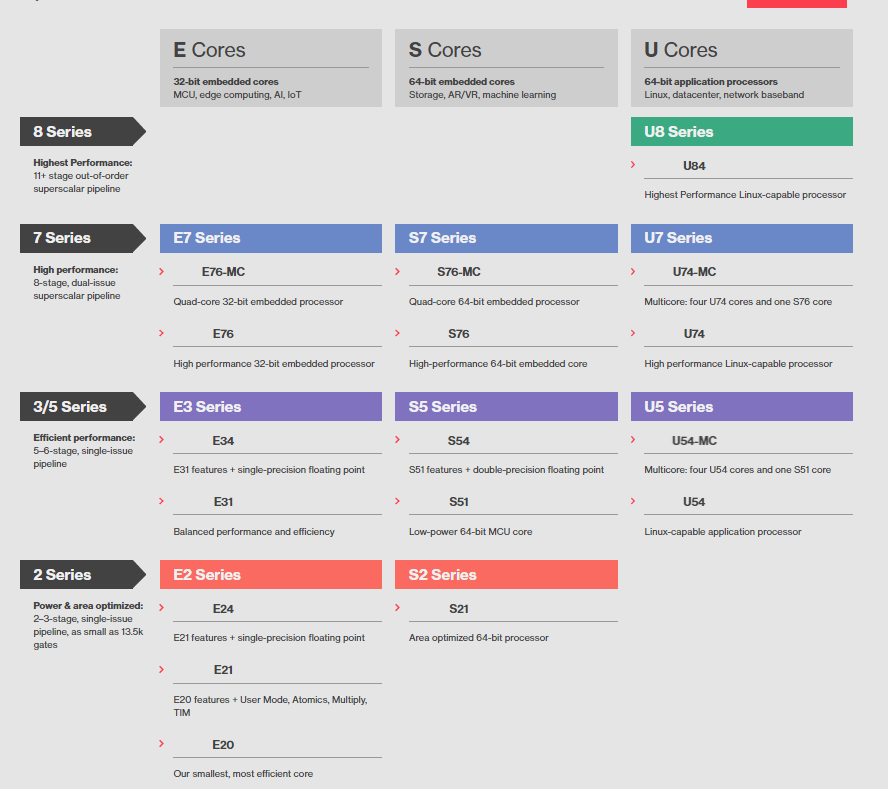

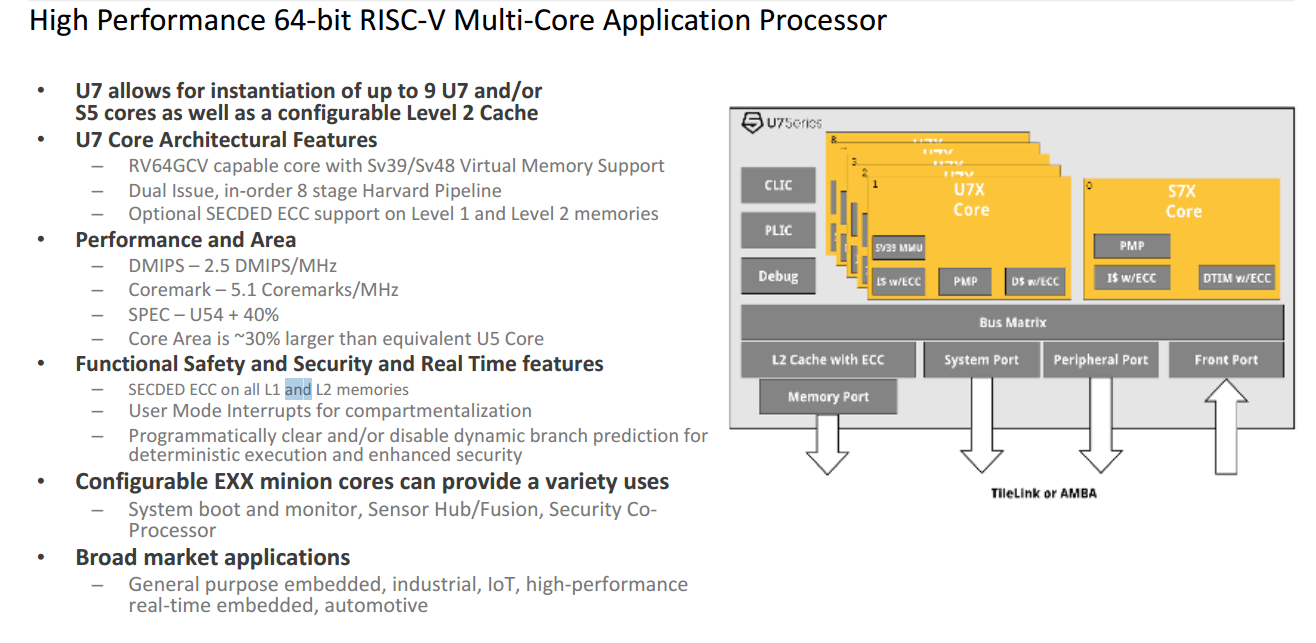

IP产品:

我们知道,ARM Cortex分为3个系列,即M,R和A,分别是针对应用嵌入式(Microcontroller)、实时(Real-Time)和操作系统(Application)3个领域,分别对应Cortex-M、Cortex-R、Cortex-A 3个系列。SiFive提供的RISC-V IP对标的也做了3个系列内核,如下,

E核,32位嵌入式内核,用于边缘计算,AI和物联网方向,对标ARM Cortex-M系列;

S核,64位嵌入式内核,用于存储、AR/VR、机器,对标ARM Cortex-R系列;

U核,64位应用处理器,用于数据中心、网络基带等方向,对标ARM Cortex-A系列;

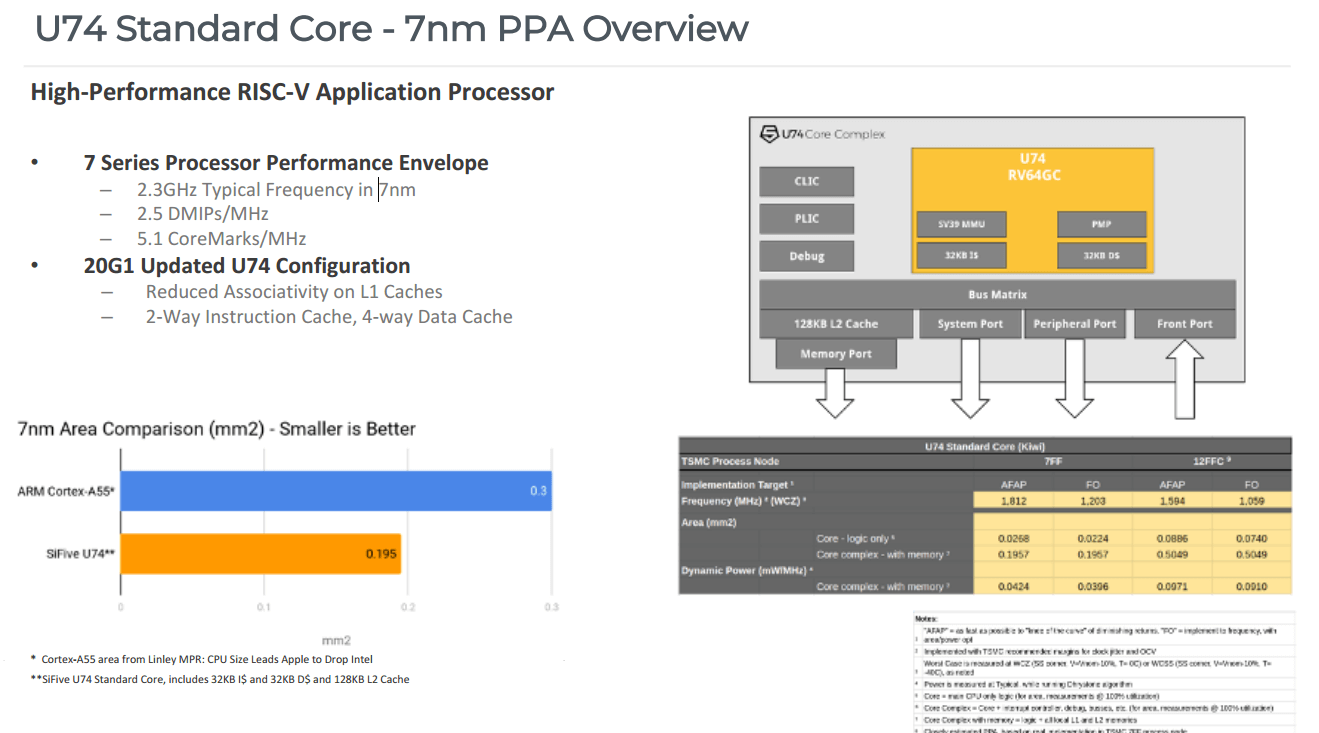

目前U系列已经可支持到:

U84系列对标的 Cortex-A72

U74对标的是Cortex-A55

且支持类似ARM的 异构架构,比如U740MC 可以将4核U74+1核S78结合在一起

问题:

是否仍不支持 类似ARM的Big.Little架构?

SiFIVE对浮点数的性能指标是多少?

SiFIVE的调频调压数据,对于DVFS的支持? 参考 功耗与性能系列之DVFS功能特性介绍

可否借用个 HiFive Unmatched 的开发板验证下软件功能?好像还带PCIE RC和SWITCH了。

S系列,在实时性上有哪些优势? 面积小?时钟高?

是否给提供RTOS系统支持?还是需要自己移植;

**

**

debug和trace

debug 类似于照相机, 将CPU运行中 某一张截图(状态)打印出来;

trace 就像录像机, 将CPU运行一段时间类得指令打印出来;

https://www.sifive.com/technology/sifive-insight 提供了一些IDE分析工具来帮忙调试。

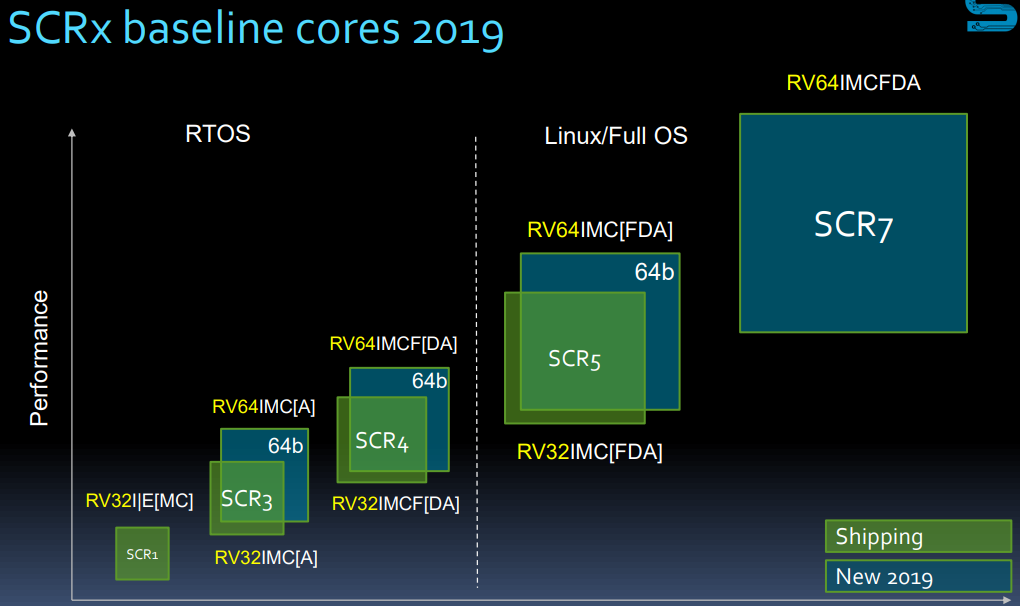

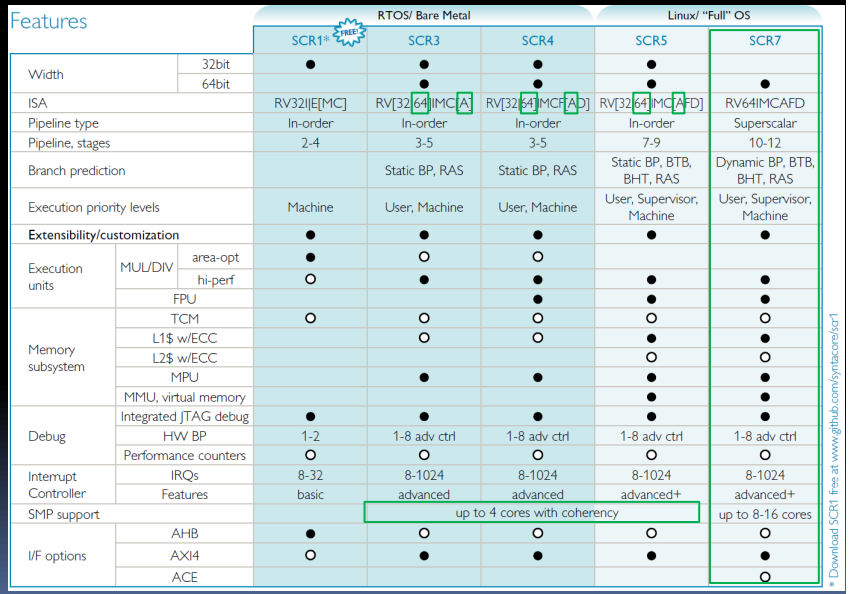

syntacore

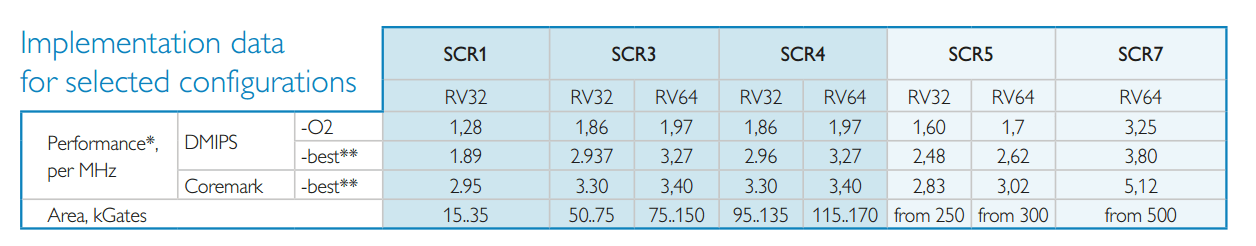

SCR系列IP产品:

支持SCR1-SCR7,其中 SCR1-SCR4 不支持MMU,只支持RTOS实时系统;

SCR5-SCR7 对标的是Cortex-A系列,支持MMU,支持Linux系统;

SCR系列性能评估

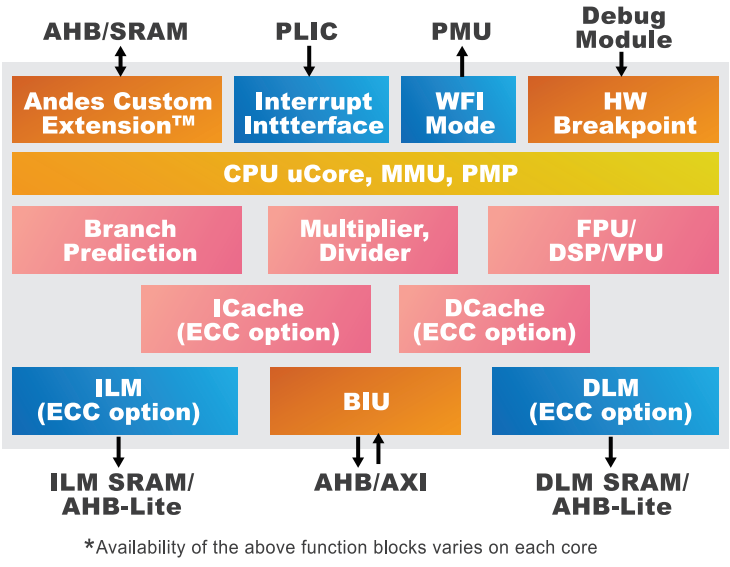

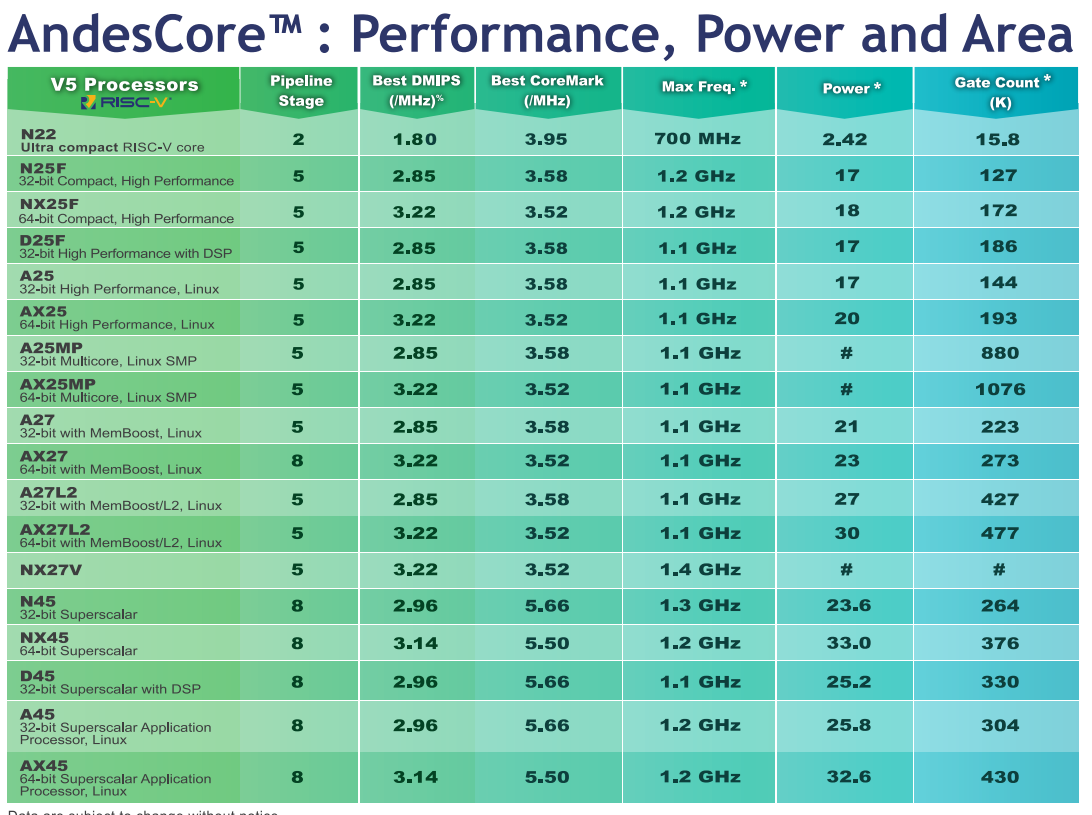

Andes 晶心科技

官网:http://www.andestech.com/cn/risc-vandes/

产品列表及参考手册: http://www.andestech.com/cn/%e4%ba%a7%e5%93%81%e4%b8%8e%e8%a7%a3%e5%86%b3%e6%96%b9%e6%a1%88/andescore-processors/

综合评估

生态评估

| 相关比较 | SiFive | Syntacore | Andes |

|---|---|---|---|

| 操作系统支持 | 支持Linux,支持RTOS | 支持Linux,支持RTOS | 支持Linux,支持RTOS |

| 编译器支持 | GNU嵌入式工具链 | - Stable GCC-based C/C++ compiler toolchain |

| IDE工具 | | 模拟器和仿真 | QEMU支持 | QEMU支持 | 未找到 | | 调试器和跟踪器 | Jtag+OpenOCD, Trace32等,JLINK | JTAG+OpenOCD | JTAG+OpenOCD | | 参考网址 | https://www.sifive.com/software | https://syntacore.com/page/products/sw-tools | http://www.andestech.com/cn/%e4%ba%a7%e5%93%81%e4%b8%8e%e8%a7%a3%e5%86%b3%e6%96%b9%e6%a1%88/andesoft-sw-stack/ |

其他信息

RISC-V需求:

- 可寻址64位地址空间-64位指令集;

- 性能超过M3,要求实时性好;

- 有比较好的生态,稳定可靠,技术支持

- 能够运行实时操作系统RTOS,调试/开发容易

- 支持MMU,后期可运行Linux系统

- more?

声明:

因为单纯要支持RTOS和实时性好,选用Cortex-R系列产品就好, 面积小,功耗低,频率较低, 性能也不错,不支持MMU;

但要支持Linux等高性能应用系统,那么只能选用 Cortex-A系列产品,面积大,功耗较高,频率高,性能更好,支持MMU;

是否可选用 异构架构,类似于 Cortex-A53+Cortex-R系列, 或者 U74-MC(4个U74+1个S76)等,根据实际应用部署合适的产品;