IO虚拟化

问题:

- 什么是IO虚拟化?有什么作用?

- 常见得IO虚拟化有哪些种类?怎么开启?

- IO虚拟化得原理是什么?是怎么做到IO虚拟化得?

- 代码实现细节是什么?

参考文章:

- 虚拟化技术 - I/O虚拟化[一] : 知乎大神的几个关于IOMMU的描述很是到位。

- 虚拟化技术 - I/O虚拟化[二]

- SMMU和IOMMU技术[一]

- SMMU和IOMMU技术[二]

- PCIE得直通和SRIOV : 描述了硬件虚拟化得种类及对比

- Intel® Virtualization Technology for Directed I/O

- vfio概述(vfio/iommu/device passthrough)

- AMD IOMMU Specification

- Kernelgo系列

IO虚拟化基础

什么是IO虚拟化?有什么作用?

IO虚拟化: 在虚拟化系统中,I/O外设只有一套,需要被多个guest VMs共享。

VMM/hypervisor提供了两种机制来实现对I/O设备访问: 透传(passthrough)和 模拟(emulation)

常见得IO虚拟化有哪些种类?怎么开启?

Intel® Virtualization Technology for Directed I/O 中 Chapter 2.4 中描述了 I/O Virtualization的分类:

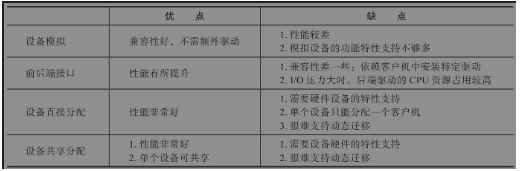

一般情况下VMM支持I/O虚拟化可以通过以下四种方式实现:

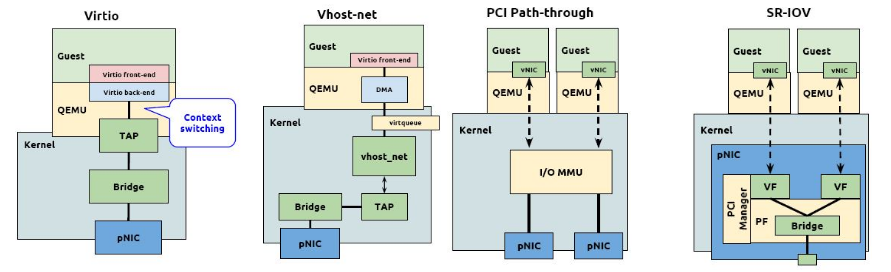

- 设备模拟(纯软件模拟)。即VMM的软件模拟一个现有的I/O设备,老毛病:兼容性好,性能和功能较差。

- 前后端驱动接口-纯软件模拟,在第一种基础上引入新的I/O操作接口,这些接口针对I/O虚拟化进行一定的优化,这样虽然能够解决一定的性能问题,但是兼容性问题又出现了,因为需要使用新的操作接口。这个可以看看后边的virtio半虚拟化。

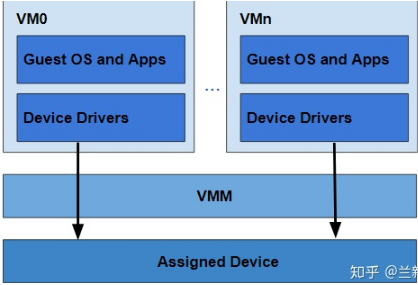

- 硬件分配,直接将I/O设备分配给某个VM(Virtual Machine),这样只有指定的VM能够使用该I/O设备,并且I/O设备的驱动位于VM中,并且VM能够直接对I/O设备进行操作,这样性能和兼容性都能达到最佳,但是一个I/O设备只能给一个VM使用。

这就是Intel VT-d技术 - I/O设备分享,这是硬件分配方式的一种扩展,主要还是需要I/O设备本身需要支持一定的功能,如能够同时提供多个功能接口,比如PCIe设备的SR-IOV功能,即PCIe设备本身能够将一个物理PCIe设备,变成多个逻辑设备,这多个逻辑设备共享该PCIe设备上的物理资源,并且可以独立地分配给不同的VM。

这就是Intel VT-c技术

四种方式得对比:

PCI得直通和SRIOV 中描述了硬件虚拟化得性能对比 以及 架构

如何开启IO虚拟化:

- 前两种使用纯软件模拟,不在考虑范围。(软件虚拟IO)

- 后两种基本都依赖主机端和PCIE得硬件支持,所以开启方式一样-硬件开启虚拟化。

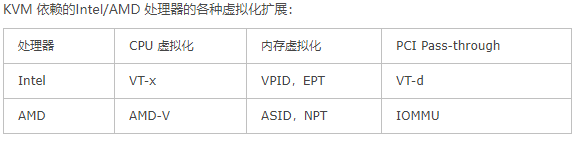

基础知识:《Intel架构简介-个人整理》中描述了Intel VT的技术相关细节:

相关参考: 10th Generation Intel® Core™ Processors, Datasheet Volume 1 of 2 # Intel CPU手册 Technologies章简述 Intel® Virtualization Technology Requirements # 虚拟化的技术需求:支持VT-x和VT-d Intel® Desktop Boards require the following components to support Intel VT or Intel VT-d:

- Intel Processor that supports Intel VT

- BIOS with Intel VT or VT-d support (found on the Security menu in BIOS setup)

- A third-party VMM (virtual machine manager) may also be required

Does My Processor Support Intel® Virtualization Technology? # windows下如何查看自己CPU是否支持虚拟化 Using Intel® Virtualization Technology (Intel® VT) with Intel® QuickAssist Technology : 如何开启Intel的虚拟化 和

Intel ® Virtualization Technology (Intel ® VT) for DirectedI/O (Intel ® VT-d)

Intel® Virtualization Technology for Directed I/O :描述VT-d的虚拟化技术

- I/O Device Assignment and Security

- DMA Remapping

- Interrupt Remapping

- Reliability

首先确保CPU支持虚拟化 (SR-IOV得后边单独讨论)

# Intel系列CPU支持虚拟化的标志为“vmx”,AMD系列CPU的标志为“svm”baiy@baiy-ThinkPad-E470c:~$ grep -E 'svm|vmx' /proc/cpuinfoflags : ..... vmx .....

然后在BIOS开启了虚拟化配置

在Linux 中GRUB加入启动参数

# /etc/default/grub中加入:GRUB_CMDLINE_LINUX_DEFAULT="intel_iommu=on iommu=pt"或者GRUB_CMDLINE_LINUX_DEFAULT="amd_iommu=on iommu=pt"sudo update-grub && sudo update-grub2

预留问题:

iommu=pt的作用是什么?

相关参考:

http://mails.dpdk.org/archives/dev/2014-October/007014.html

和

https://community.mellanox.com/s/article/understanding-the-iommu-linux-grub-file-configuration

IOMMU简述(重点)

本章主要参考以下几篇文章,整理下比较关键的点:

虚拟化技术 - I/O虚拟化[一]

虚拟化技术 - I/O虚拟化[二]

SMMU和IOMMU技术[一]

SMMU和IOMMU技术[二]

虚拟化得几个地址(复习)

- 1)客户机虚拟地址,GVA(Guest Virtual Address)

- 2)客户机物理地址,GPA(Guest Physical Address)

- 3)宿主机虚拟地址,HVA(Host Virtual Address)

- 4)宿主机物理地址,HPA(Host Physical Address)

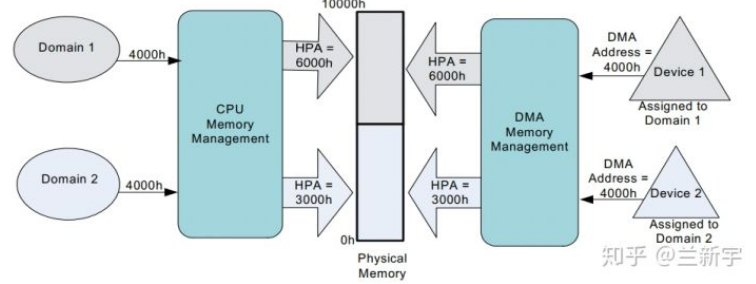

内存虚拟化中,EPT等页表加入了GPA<->HPA得转换,使得Guest可以快速得访问到HPA;

IOMMU的出现

基础概念:大部分IO设备是支持DMA得,但DMA传输时,使用总线地址(也就是dma_map_single和dma_alloc_coherent 最后得到的dma_addr_t).

其实,在以前,总线地址就是CPU存储域的物理地址。但因为一些设备 与 HOST端 地址总线位宽不一致,导致了只能访问 部分 存储空间的限制(比如16M)。

所以引入了IOMMU,使得DMA传输时,可以用另一套地址:虚拟地址,也就是IOVA。

Guest上使用得是GPA, DMA必须使用HPA;因此有了IOMMU(AMD)和机制,将GPA的地址转为HPA的地址;

然而,不和AMD使用相同的名字是Intel一贯的路数,所以Intel通常更愿意把这种硬件辅助的I/O虚拟化技术叫做VT-d(Virtualization Technology for Direct I/O)。作为后起之秀的ARM自然也不甘示弱,推出了对应的SMMU(System MMU)。

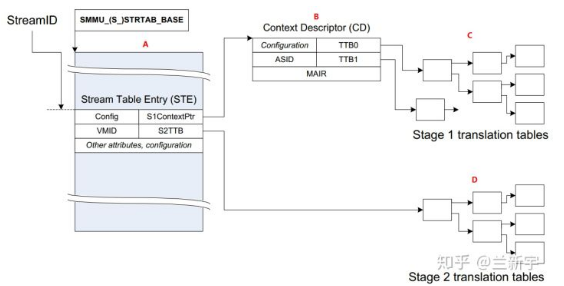

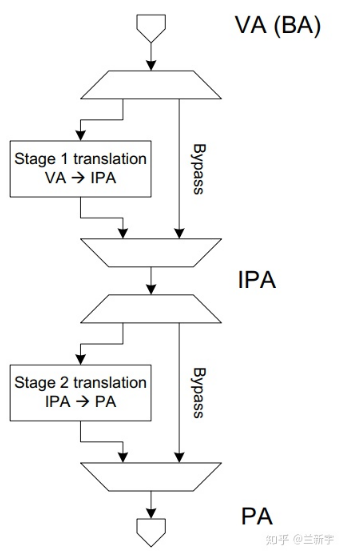

stage的概念:

stage 1的GVA->GPA(按ARM的叫法则是VA->IPA)的转换。

stage 2的GPA->HPA(IPA->PA)的转换

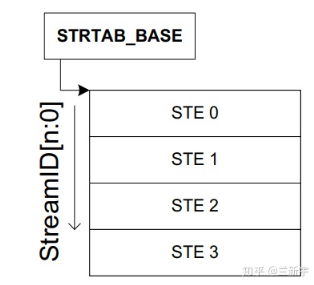

在INTEL X86上,每一个Guest 也叫domain, 给每一个domain 都建立一个EPT页表(来支持stage2 GPA->HPA)的转换. 在IOMMU中,建立一个表,根据BDF为索引(StreamID),来查找表对应的STE.

然后每个STE,内部包含两个页表指针:

S2TTB(Stage 2 Translate Table Base)直接指向对应domain(VMID)的EPT页表地址,这样就可以支持虚拟化了。

S1ContextPTR :根据ASID(PCIE下是PASID,也就是进程ID)来索引到对应进程号,这样就可以找到进程页表,然后将S1指向进程页表就OK了。也就吧DMA导入到用户空间可见。

另外,我们知道,基于Linux内核的主页表外,每一个进程(基于自己的进程ID)都有自己的页表项(要不怎么会都用0-3G)。

IOMMU使用stage2 GPA->HPA 进行地址转换。 那么只需要让DMA在过IOMMU时,也指向对应Guest的EPT页表,那么就可以支持虚拟化场景了。

IOMMU也支持stage1 GVA->GPA转换, 所以在知道进程ID的情况,我们只需要将GPA 按照 进程的页表 进行转换下,那么就可以到GVA,让DMA可以在用户空间可见。

两级Stage 均可配置使能或禁止使能。

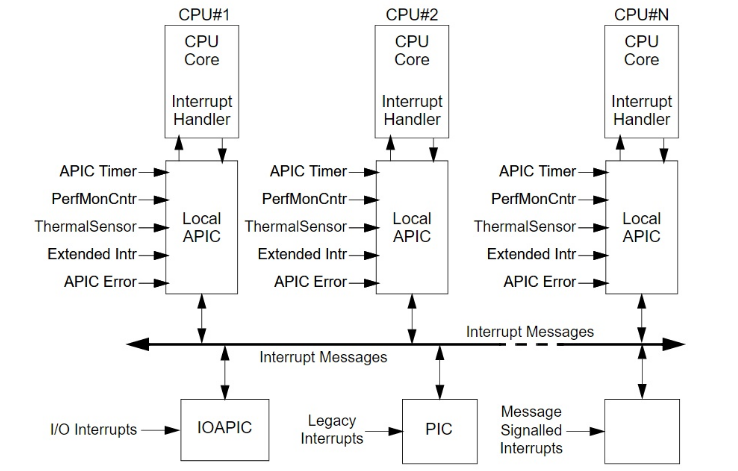

中断重映射 和 中断发布

参考以下文章,已经描述的很清楚了

- 虚拟化技术 - 中断虚拟化

- Intel VT-d(3)- Interrupt remapping

- Intel VT-d(4)- Interrupt Posting

- VT-d Interrupt Remapping

- VT-d Posted Interrupt

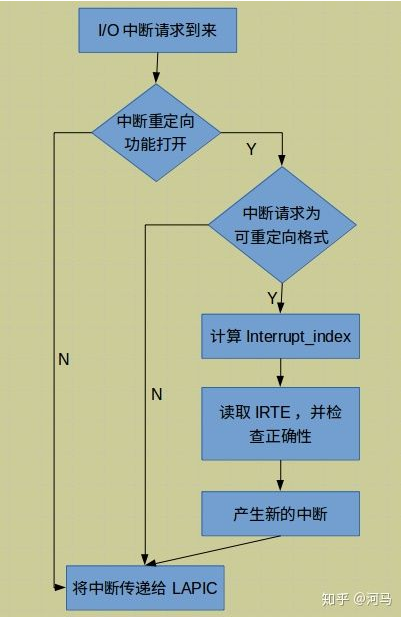

先简单记录下流程:

检测硬件支持

从ACPI中可以检测到 Intel DMAR中DRHD的个数,每个DRHD中包含了 Capability Register 和 Extended Capability Register 。

其中 Capability Register [59] == 1 代表支持 Posted Interrupt Support(PI)。

其中 Extended Capability Register [3] == 1 代表支持 Interrupt Remapping Suppor(IR)。

且中断重定向映射功能打开: Global Status Register的IRES为1

给每个DRHD申请Interrupt Remapping Table

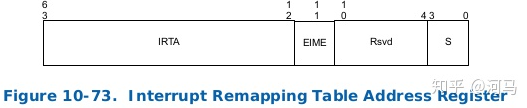

在内存中申请 64K*128bit的空间,因为每个中断信息为128-bit,最大支持64K(无论是MSI DATA寄存器,还是Interrupt Remap Table Address Register,

都只给预留了64K的索引)个中断。 这个中断数组-entry 为单层表,一个128bit数据对应一个中断,称为:Interrupt Remap Table Entry。

然后将地址和大小告诉 Interrupt Remap Table Address Register 。 其中需要初始化中断的属性(参考vt-d 9.10章节进行初始化)。

中断触发时,根据BDF作为sources-ID,以及MSI的 Address 和 Data寄存器,找到这个数组的索引。然后根据索引,找到 Interrupt Remap Table Entry(IRTE),检查

IRTE中的(IRTE Mode, [15])位来判断中断类型: 0为remapping中断,1为Posted 中断。

remapping中断解析:

posted中断后续在研究。

Intel VT-D技术(自己看的)

在上边主要研究了 IO虚拟化的种类,和 如何使用。

但 关于硬件虚拟化的原理是什么?为什么能带来加速?提供了哪些使用方式?

相关参考:

- 10th Generation Intel® Core™ Processors, Datasheet Volume 1 of 2

- Intel® Virtualization Technology for Directed I/O (主要部分)

- intel VT-D (iommu) spec 解读

在 10th Generation Intel® Core™ Processors, Datasheet Volume 1 of 2 中 简要描述了第10代CPU内部关于VT的特性;

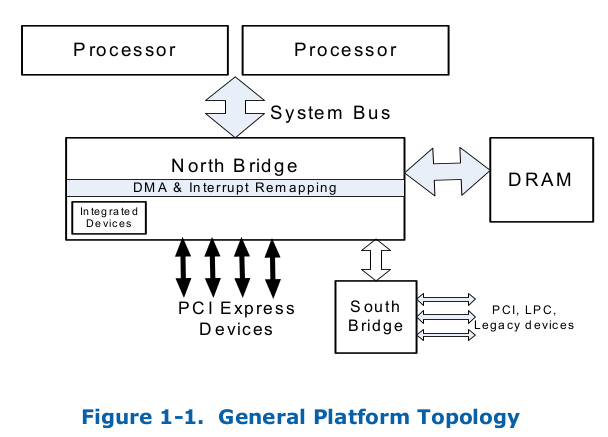

X86通用平台拓扑结构

Intel®Virtualization Technology For Directed I/O Overview

IO虚拟化的基础要求是:所有上述I / O虚拟化模型的一般要求是能够隔离和限制设备对管理设备的分区所拥有资源的访问。 Intel VT-D 提供了下述能力:

- I/O device assignment - 灵活的分配IO设备到VMs,提供隔离和保护;

- DMA remapping - DMA地址转换

- Interrupt remapping: - 隔离并路由正确的中断到VM

- Interrupt posting - 直接投递中断

- Reliability - 记录和报告 DMA/中断的错误

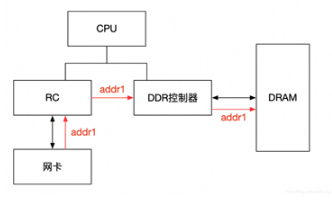

DMA remapping(其实就是IOMMU)

在之前基础上,我们知道: DOMAIN(Guest)访问,用的是GHA->GPA,但DMA访问硬件需要HPA,所以硬件IO虚拟化支持都会在IO与DMA层加入一个 IOMMU/DMA REMAPPING/SMMU层,这样DMA直接使用GPA即可;

VFIO概述 中描述了 DMAR(IOMMU)的作用:

- 屏蔽物理地址,起到保护作用。典型应用包括两个:一是实现用户态驱动,由于IOMMU的映射功能,使HPA对用户空间不可见,在vfio部分还会举例。二是将设备透传给虚机,使HPA对虚机不可见,并将GPA映射为HPA

- IOMMU可以将连续的虚拟地址映射到不连续的多个物理内存片段,这部分功能于MMU类似,对于没有IOMMU的情况,设备访问的物理空间必须是连续的,IOMMU可有效的解决这个问题

参考: vfio概述(vfio/iommu/device passthrough)

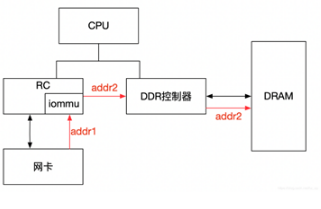

无IOMMU情况 启动IOMMU情况

首先要明确一个事: 这个操作是基于DMA的,DMA主要用来 外设 和 主存 进行数据交互的,且都用的是总线物理地址。

DMA remapping 为设备访问内存的隔离 提供了一个硬件支持,通过 一个特定的页表集(位于硬件缓存 来加速地址转换) 使得一个设备 可以被分配给特定的Domain(Guest)OS;

当位于Domain OS的设备试图访问 主存, DMA remapping 硬件接管这个请求,然后管理访问权限和实际的内存物理地址进行转换; 一个设备可以用一个DMA Remapping表, 也可多个设备共用 (其实就是IOMMU_GROUP的说法);

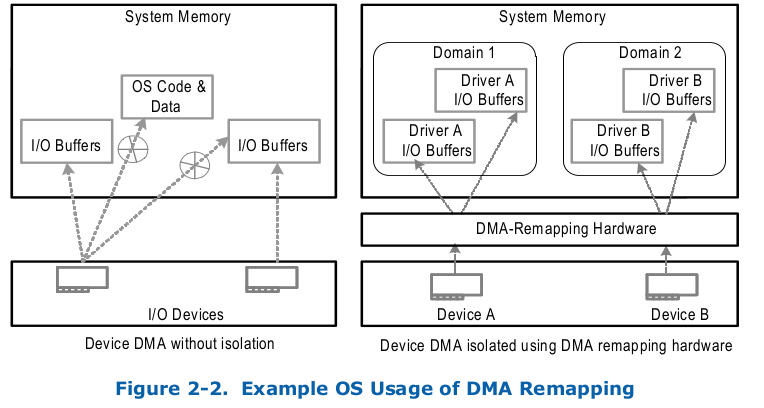

OS Usages of DMA Remapping (IOMMU的优点)

可参考 IOMMU简述

- OS Protection: 操作系统可以定义一个包含其关键代码和数据结构的domain,并限制系统中所有I / O设备对该domain的访问。 这允许操作系统通过设备驱动程序对设备进行不正确的编程来限制其数据和代码的错误或意外损坏,从而提高了操作系统的健壮性和可靠性。

- Feature Support :操作系统可以使用domain来更好地管理从旧版设备到高内存的DMA(例如,访问4GB以上内存的32位PCI设备)。 这是通过对I / O页表进行编程以将DMA从这些设备重新映射到高内存来实现的。 没有这样的支持,软件就必须通过OS的“反弹缓冲区(bounce buffers)”来复制数据

- DMA Isolation:OS可以通过创建多个domain并将一个或多个I / O设备分配给每个域来管理I / O。每个设备驱动程序都会在操作系统中显式注册其I / O缓冲区,然后操作系统会使用硬件实施DMA域保护,从而将这些I / O缓冲区分配给特定的domain。

Shared Virtual Memory(SVM功能):对于支持适当PCI Express1功能(PCI Express *基本规范中的进程地址空间ID - PASID功能)的设备,操作系统可以使用DMA重映射硬件功能与I / O设备共享应用程序进程的虚拟地址空间。共享的虚拟内存以及对I / O PAGE-FAULT的支持,使应用程序可以将任意数据结构自由地传递到图形处理器或加速器等设备,而无需进行数据固定和编组的开销。。

参考:[共享虚拟存储系统](https://www.cnblogs.com/shaohef/p/12079657.html) <br />

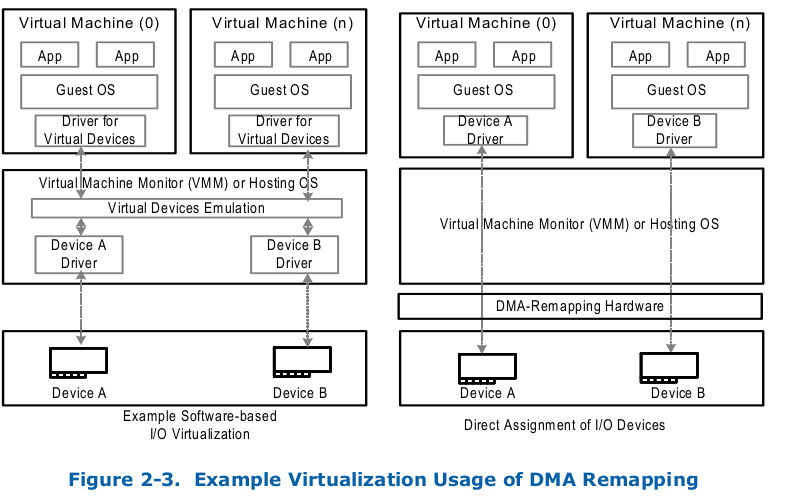

VMM Usages of DMA Remapping

以前IO虚拟化都是纯软件模拟,每个请求都会进VMM层,导致性能很慢;

现在不怕了, 有DMA Remapping这玩意,外设可以直接绕过VMM层给指定的Guest,然后访问Device基本不用经过VMM层(只有在配置访问或中断管理时要进入VMM);(注:该模型为设备直通模式,设备同时只能被一个设备使用)

为了支持I / O设备的直接分配,VMM必须强制隔离DMA请求。可以将I / O设备分配给域,并且可以使用重映射硬件将DMA从I / O设备限制为当前由其域拥有的物理内存。对于可能在物理内存中重定位的域,可以对重映射硬件进行编程以执行必要的转换。

I/O设备分配允许其他I/O共享用法(不懂)-例如,将I/O设备分配给为其他用户分区提供I/O服务的I/O分区。重新映射硬件使能虚拟化软件,以选择设备分配和基于软件的I / O虚拟化方法的正确组合。

DMA重新映射还支持基于硬件的I/O虚拟化技术,例如SR-IOV)和Intel®可扩展I/O虚拟化(Intel®可扩展IOV)。借助SR-IOV功能,可以将设备物理功能配置为支持多个虚拟功能(VF)

DMA Remapping Usages by Guests

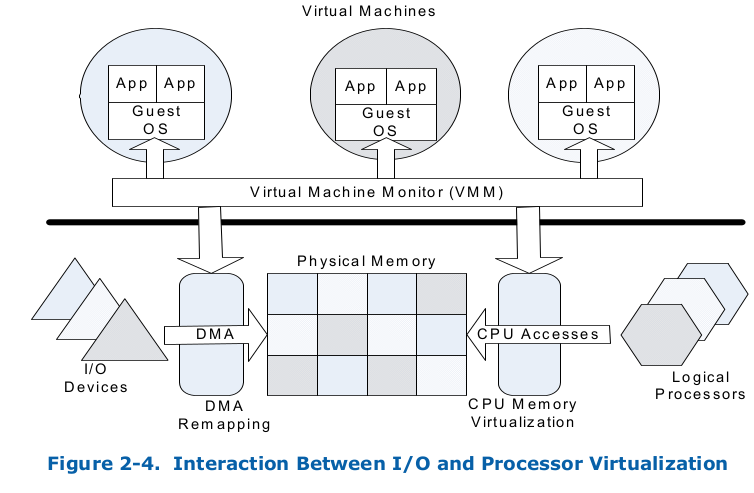

Interaction with Processor Virtualization

Guest访问主存通过 VMM,将GPA转为HPA(EPT页表)

IO设备访问主存,通过DMA Remapping,将GPA转成了HPA

这样,处理器内存管理和DMA内存管理都在VMM的控制之下。

Hardware Support for Interrupt Remapping

Interrupt remapping 为 I/O设备中断请求的remapping和路由 提供了硬件支持;

Interrupt Isolation

Interrupt Migration

x2APIC Support

DMA Remapping

Type of DMA requests

EP端有两种DMA请求:

- Requests without address-space-identifier,不带地址空间ID的, 只是正常读写DDR的DMA请求;

- Requests with address-space-identifier, 带ID的DMA请求,这个TLP包附带额外信息,包含PASID;

Domains and Address Translation

注:Inbound:PCI域訪问存储器域, Outbound:存储器域訪问PCI域

重点: A domain is abstractly defined as an isolated environment in the platform, to which a subset of the

host physical memory is allocated. I/O devices that are allowed to access physical memory directly

are allocated to a domain and are referred to as the domain’s assigned devices. For virtualization

usages, software may treat each virtual machine as a domain. The isolation property of a domain is achieved by blocking access to its physical memory from

resources not assigned to it. Multiple isolated domains are supported in a system by ensuring that all

I/O devices are assigned to some domain (possibly a null domain), and that they can only access the

physical resources allocated to their domain. The DMA remapping architecture facilitates flexible

assignment of I/O devices to an arbitrary number of domains. Each domain has a view of physical

address space that may be different than the host physical address space. Remapping hardware

treats the address in inbound requests as DMA Address.Depending on the software usage model, the DMA address space of a device (be it a PhysicalFunction, SR-IOV Virtual Function, or Intel®Scalable

IOV Assignable Device Interface (ADI)) may be the Guest-Physical Address (GPA) space of a virtual

machine to which it is assigned, Virtual Address (VA)space of host application on whose behalf it is

performing DMA requests, Guest Virtual Address (GVA) space of a client application executing within a

virtual machine, I/O virtual address (IOVA) space managed by host software, or Guest I/O virtual

address (GIOVA) space managed by guest software. In all cases, DMA remapping transforms the

address in a DMA request issued by an I/O deviceto its corresponding Host-Physical Address (HPA).

domain 在Intel中被定义为: 平台上的一块 占用一部分主机内存的一个隔离环境, 被分配到这个隔离环境的I/O设备 , 允许直接访问到这个隔离环境的物理内存。

域的隔离属性是通过 : 阻止从未分配的资源 对其物理内存的访问来实现的。

Multiple isolated domains 的实现是通过: 所有被分配到domain的I/O设备 只能访问 分配给当前域的 物理资源。

DMAR架构 方便灵活的分配I/O设备到任意数量的域。每一个域 有一些和 HPA不同的物理地址空间-GPA;

中断重映射

基础知识:虚拟化技术 - 中断虚拟化

本文主要翻译: Intel® Virtualization Technology for Directed I/O (第五章)

Interrupt Remapping

中断重新映射架构 使 系统软件可以 控制和审查 所有中断 (由 所有中断源 产生的外部中断请求,包括来自中断控制器(I/OxAPIC),支持MSI / MSI-X的设备(包括EP, root-ports和Root-Complex))的请求。

注:由 Interrupt Remapping硬件本身生成的中断(故障事件和失效完成事件)不受中断重映射的约束。

外设中断请求在 RC上 显示为向 中断地址范围0xFEEX_XXXXh 写入请求。 由于 中断请求作为写请求到达RC,因此 中断重映射 与 重映射硬件单元 位于同一位置。

通过 Extended Capability Register 报告中断重映射功能

Identifying Origination of Interrupt Requests

识别中断请求的来源:

为了支持domain-isolation ,平台硬件必须能够为每个中断消息唯一地标识请求者(source-id)。 平台中的中断源以及在这些请求中使用source-id可以分类如下

- Message Signaled Interrupts from PCI Express Devices : 【我们只看这个,源ID就是BDF号,后边别纠结了】

PCI Express设备发出的消息信号中断

—对于来自PCI Express设备的消息信号中断请求,source-id是PCI Express 事务header中的requester-id。 设备的 requester-id 由配置软件分配的PCI Bus/Device/Function number组成,并且唯一标识发起I / O请求的硬件功能。

- Message Signaled Interrupts from Root-Complex Integrated Devices

- Message Signaled Interrupts from Devices behind PCI Express to PCI/PCI-X Bridges

- Message Signaled Interrupts from Devices behind Conventional PCI bridges

- Legacy pin interrupts

- Other Message Signaled Interrupts

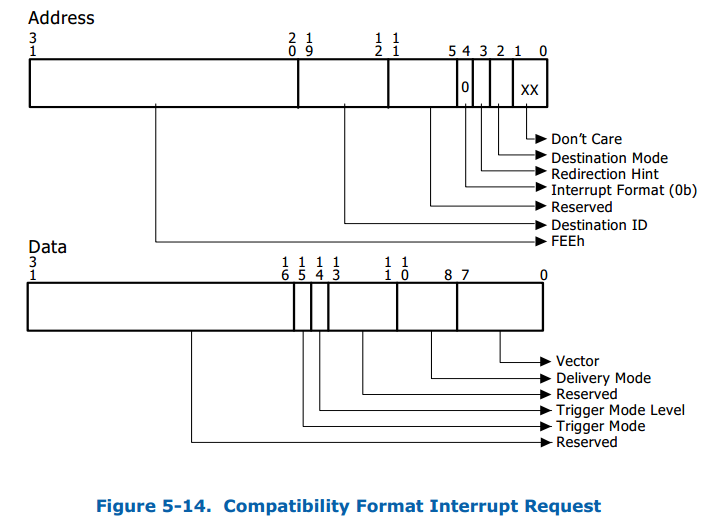

Interrupt Request Formats On Intel® 64 Platforms

支持两种中断请求格式: 兼容模式主要为了 兼容 不支持中断重映射的平台。

Interrupt Requests in Compatibility Format 兼容模式(不关注)

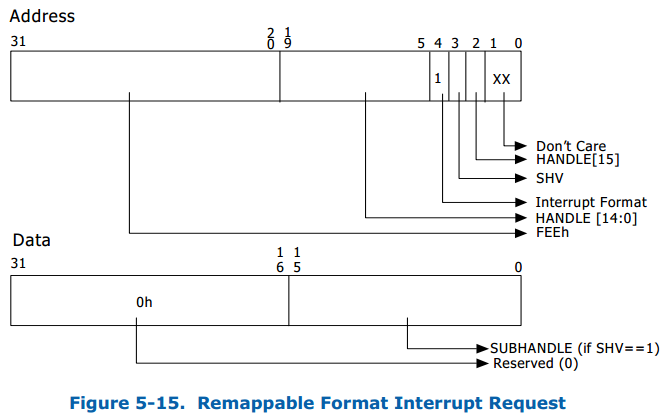

Interrupt Requestsin Remappable Format 可重映射模式(重点)

这里需要注意的是:

Interrupt Format: 必须为1,用来 启动 Interrupt remapping

Handle[15:0]: 16位句柄。 interrupt remapping hardware 硬件使用该句柄来标识中断请求。 16位句柄为 每个中断重映射硬件单元提 供64K唯一中断请求。

SVH为1时,支持subhandle,SVH为0时,不支持subhandle。

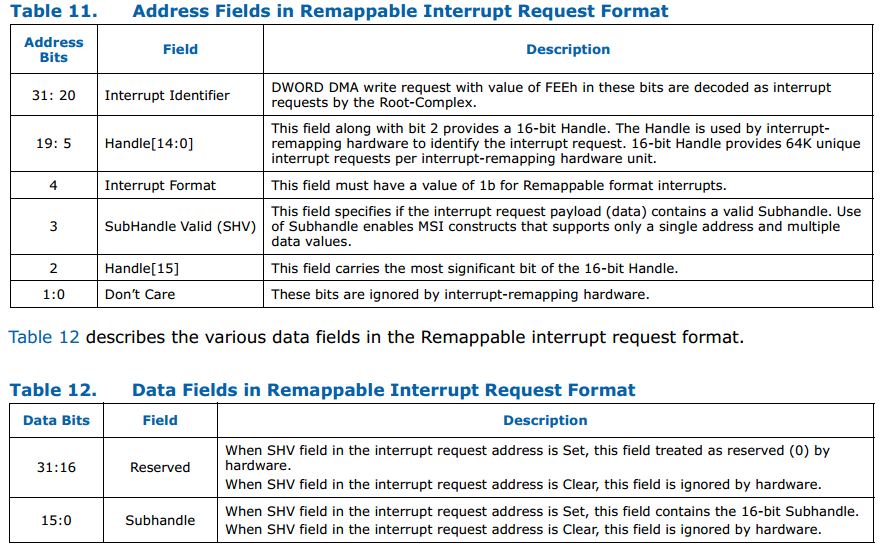

Interrupt Remapping Table

中断重映射硬件利用 驻留在内存中的单级别表,称为 中断重映射表。 预计中断重映射表将由系统软件设置,并且其基地址和大小通过中断重映射表地址寄存器指定。 该表中的每个条目的大小均为128位,称为中断重映射表条目(IRTE)。第9.10节说明了IRTE格式。

对于可重映射格式的中断请求,中断重映射硬件将如下计算“ interrupt_index”。 根据 可重映射的中断格式,Handle,SHV和subhandle 分别是中断地址和数据中的字段

if (address.SHV == 0) {interrupt_index = address.handle;} else {interrupt_index = (address.handle + data.subhandle);}

中断重映射表地址寄存器 由软件编程,以指定中断重映射表中的IRTE数量(中断重映射表中的IRTE的最大数量为64K)。

平台中的 重新映射硬件单元 可以被配置为 share interrupt-remapping table 或者 use independent tables。

interrupt_index用于索引 中断重映射表中适当的IRTE。 如果计算出的interrupt_index值等于或大于重新映射表中IRTE的数量,则硬件会将中断请求视为错误。

与所有中断属性都编码在中断请求地址/数据中的兼容中断格式不同,可重映射中断格式仅指定计算interrupt_index所需的字段。

重新映射的中断请求的属性通过以下方式指定 interrupt_index引用的IRTE。

中断重映射体系结构定义了对硬件的支持,以缓存常用的IRTE以提高性能。对于软件可能需要动态更新IRTE的用途,体系结构定义了使IEC无效的命令。第6章介绍了缓存结构和相关的无效命令。

Interrupt-Remapping Hardware Operation

中断处理流程:

- 硬件外设给主机0xFEEx_xxxx 写入一个DWORD=4字节的数据

- 未启用中断重映射时(全局状态寄存器中的IRES字段为Clear),所有中断请求均按照 兼容性中断请求格式进行处理。

- 中断使能后-IRES为1,处理流程如下:

兼容格式中断:

如果启用了扩展中断模式(设置了中断重新映射表地址寄存器中的EIME字段),或者禁用了兼容格式中断(全局状态寄存器中的CFIS字段为Clear),则兼容格式中断被blocked.。

否则,兼容性格式中断将作为传递处理(bypasses中断重新映射)

Remappable 格式中断:

首先,检查 Remappable interruptre 请求中的保留字段 ,必须为零。 如果保留的字段检查失败,则中断请求将被阻止。 如果检测通过,从中断请求中检索Source-id,Handle,SHV和Subhandle字段。

硬件根据第5.1.3节中所述的算法计算interrupt_index。 验证计算出的interrupt_index小于在“中断重映射表地址寄存器”中配置的中断重映射表大小。 如果边界检查失败,则中断请求将被阻止

如果以上边界检查成功,则从中断条目高速缓存中检索对应于interrupt_index值的IRTE,或从中断重新映射表中获取该中断。 如果在扩展功能寄存器中将连贯(C)字段报告为“清除”,则从内存进行的IRTE提取不会监听处理器缓存。

硬件必须以单个操作读取整个IRTE(原子操作),并且不能使用多次读取来获取IRTE的内容,因为软件可能会自动更改IRTE的内容。 报告内存类型支持(ECAP_REG中的MTS = 1)的硬件实现必须对IRTE提取使用回写(WB)内存类型。 如果IRTE中的“当前(P)”字段为“清除”,则中断请求将被阻止并视为故障

如果存在IRTE(P = 1),则硬件会按照第9.10节中所述,通过对IRTE中的SVT,SID和SQ字段进行编程来验证中断请求者。 如果源ID检查失败,则中断请求将被阻止。

如果存在IRTE(P = 0),硬件以可重映射的格式解释IRTE(如第9.10节所述)。 如果检测到对可重映射格式IRTE的编程无效,则中断请求将被阻止。如果以上检查成功,则根据IRTE字段的编程会生成重新映射的中断请求

导致中断请求被blocked的上述任何检查均被视为中断重新映射故障条件。 在5.1.4.1有描述

编程中断源以生成可重映射的中断

软件执行以下一般步骤来配置中断源以生成可重映射的中断:

- 分配IRTE表,并按照9.10节中所述的IRTE格式对重新映射的中断属性进行编程

- 对中断源进行编程,以生成具有可重映射格式的中断,并带有适当的句柄,子句柄和SHV字段,这些字段可将分配的IRTE的索引有效编码为5.1.3节中定义的interrupt_index。 可以使用handle,subhandle和SHV字段以下列方式之一对interrupt_index进行编码:

SHV = 0; handle = interrupt_index;

SHV = 1; handle = interrupt_index; subhandle = 0;

SHV = 1; handle = 0; subhandle = interrupt_index;

SHV = 1; handle = interrupt_index - subhandle;

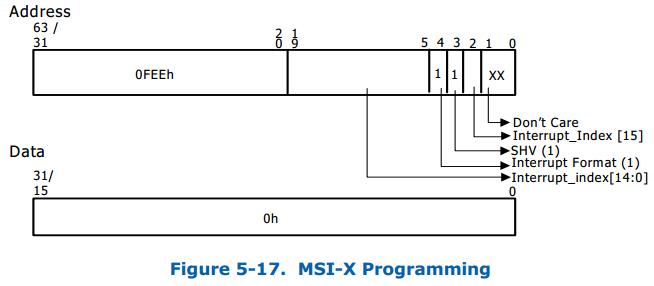

以下小节介绍了I / OxAPIC,MSI和MSI-X中断源的示例编程,以按照可重映射中断请求格式生成中断。【这里暂时只看MSI/MSIX】

这里 只解释生疏的字段:

地址寄存器配置:

[19:5]+[2] : Interrupt index[15:0], 重点IRTE表的索引。 2^16,所以IRTE表最多64K

[4]: 为1表示支持中断可映射格式。

[3]: subhandle

Data register is programmed to 0h

中断发布Interrupt Posting

TBD

===============================TBD—-需要整理部分

在《KVM实战基础中》,了解到硬件加速的虚拟化,不仅仅是 svm|vmx , 还有一部分IO上的虚拟化加速。

SMMU?IOMMU和VT-d?

内存访问方式: 每个VM中CPU使用的虚拟地址叫GVA(Guest Virtual Address) ,在被自己的MMU翻译后为GPA(Guest Phisical Address) ,Intel VT-x技术中拓展了EPT页表项,在硬件上可以转换成HPA(Host Physical Address)

IO在CPU访问外设时也可以走这条路,但似乎忘记了DMA这个东西,DMA是外设和主存间交互的,需要HPA; 所以在硬件支持上,DMA下边加了一层MMU,AMD叫IOMMU,ARM叫SMMU,Intel叫VT-d。

在《虚拟化基础知识》中,描述了硬件虚拟化,提到了以下几点:

- Intel对外设IO硬件支持VT-d/VT-c技术。

- 通过VT-d和VT-c,支持了外设到VM的直通模式

硬件辅助的IO虚拟化主要包括英特尔VT-d, AMD的IOMMU(AMD-Vi)和PCI-SIG 的SR-IOV。前两种属于Directed I/O。物理设备直接分配给虚拟机使用,通过硬件芯片完成GPA到MA 的翻译。IOV 通过在硬件设备中增加一个PCIe 设备,用于呈现一个PF或多个VF,从而可以将每个VF单独分配给不同的虚机使用。

比如内存外设统一编址的MMIO(Memory-mapped I/O),VMn访问时,可通过GHA->GPA->HPA转换。 所以VMn中CPU访问内存没有问题。

https://www.cnblogs.com/sammyliu/p/4548194.html

https://zhuanlan.zhihu.com/p/93289632

https://blog.csdn.net/W1107101310/article/details/80085382?utm_medium=distribute.pc_aggpage_search_result.none-task-blog-2first_rank_v2~rank_v25-5-80085382.nonecase&utm_term=dma%E5%8E%9F%E7%90%86%20linux