PCIE得复位机制

相关参考

参考

传统的复位方式 和 FLR

PCI Express Base_r5_1 6.6 PCI Express Reset - Rules (P552)

Cold Rset

在描述电源信号的时候, 提到过:PCIE支持3.3V和12V供电,

PCIE主要使用Vcc-12V供电,Vaux-3.3V主要是电源管理相关,为了降低功耗和缩短恢复时间使用。

Cold Rset主要复位的是12V,复位除电源管理部分的所有复位。

除非彻底断掉,一般3.3V电源管理模块不断电。

Warm Reset

Spec无强制规定,自定义复位。不过多解释

Hot Reset

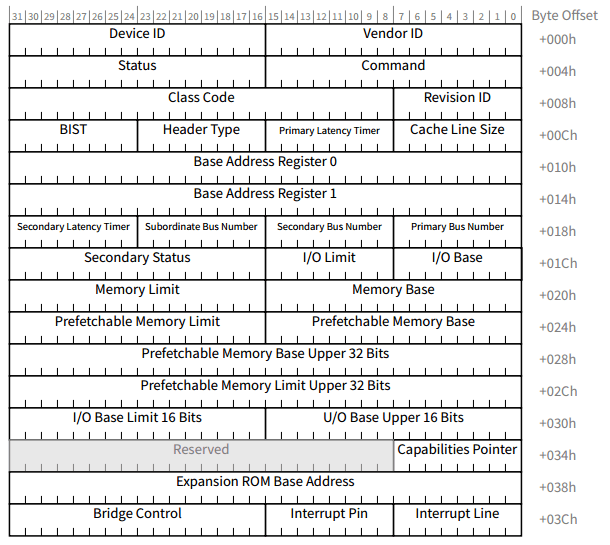

PCIE桥的配置空间参考:PCI Express Base_r5_1 7.5.1.3 Type 1 Configuration Space Header

这里会用到: 7.5.1.3.13 Bridge Control Register (Offset 3Eh) 中的 Secondary Bus Reset 位 写1 可以使用Host Rset(PCI总线,

使用RST#信号复位, PCIE设备使用TS1和TS2序列对下游设备进行Host Rset)

PCI Express Base_r5_1 P552描述: There is an in-band mechanism(带内机制) for propagating Conventional Reset across a Link. This is called a hot reset and is described in Section 4.2.4.9.2 . There is an in-band mechanism for software to force a Link into Electrical Idle, “disabling” the Link. The Disabled L TSSM state is described in Section 4.2.5.9 , the Link Disable control bit is described in Section 7.5.3.7 , and the Downstream Port Containment mechanism is described in Section 6.2.10 . Disabling a Link causes Downstream components to undergo a hot reset. Note also that the Data Link Layer reporting DL_Down status is in some ways identical to a hot reset -see Section 2.9 .

触发Hot Rset的情况: 当PCIE设备出现某种异常时,可以使用软件手段对设备进行复位。

- 软件给EP对应的上游桥设备的 Secondary Bus Reset 写1时,触发Hot Rset。

- 链路层向事务层报告DL_DOWN (PCI Express Base_r5_1 P212页: While in DL_Inactive 描述)

注:当Switch设备 收到Up Stream的Hot Reset,那么先广播给下游设备后,在复位自己。 当下游设备是PCIE-2-PCI桥时,

给PCI设备发送RST#

可以通过 lspci -t 或者 ls -al /sys/bus/pci/devices/ 查看 指定设备的 上游桥设备的BDF号sudo setpci -s 00:01.1 3E.B=40然后lspci 查看Bridge Control中是否修改成功lspcisudo setpci -s 00:01.1 3E.B=00

Hot Reset的行为

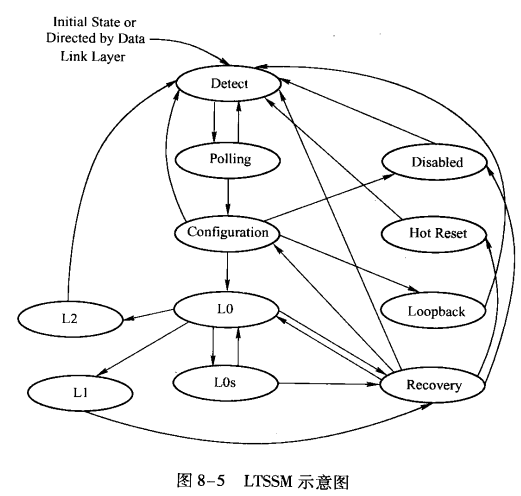

链路状态机进入到Hot Reset 后。回退到Detect状态。

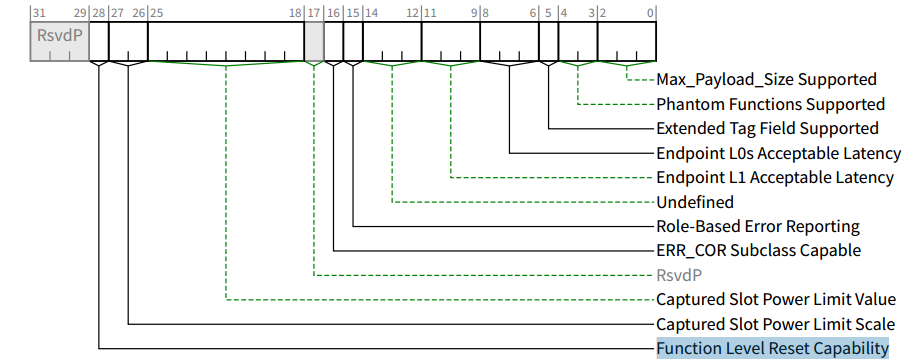

FLR

PCIe总线自V2.0加入了功能层复位(Function Level Reset,FLR)的功能。该功能主要针对的是支持多个功能的PCIe设备(Multi-Fun PCIe Device),可以实现只对特定的Function复位,而其他的Function不受影响。当然,该功能是可选的,并非强制的(SRIOV中PF是必须的)。软件可以通过查询配置空间中的设备功能寄存器(Device Capability Register)来查询该PCIe设备是否支持FLR。如下图所示:

之前看Synopsys的IP: 错误理解:支持FLR方式的PCIe设备需要在其BAR空间中提供一个寄存器,当系统软件对该寄存器的Function LevelReset位写1时,PCIe设备将使用FLR方式复位PCIe设备的内部逻辑。

这种做法好像很无语,因为标准规定:100ms内必须完成FLR复位,在内核代码 pci_flr中根本没 用户自定的操作接口,只能按照标准版本去进行FLR, 不允许有自定义的操作。 让ASIC修复

FLR的应用场景

在一个大规模的并行处理系统中,系统软件使用分区的概念管理所以硬件资源,包括处理器资源和所以IO资源,这些IO资源中通常会包含PCIe设备。

在这种处理器系统中,任务在指定的分区中运行,当这个任务执行完毕后,系统软件需要调整硬件资源的分区。此时受到影响的PCIe设备需要使用FLR方式复位内部的逻辑,以免造成对新的分区的资源污染,并保护之前任务的结果。

当PCIe设备使用FLR方式进行复位时,有些与PCIe链路相关的状态和寄存器并不会被复位:

Ø Sticky Registers。与传统的复位方式相同,FLR方式不能复位这些寄存器,但是系统软件对部分Sticky Registers进行修改。当Vaux(备用电源)被移除后,这些寄存器中的保存的数据才会丢失。

Ø HwIint类型的寄存器。在PCIe设备中,有效配置寄存器的属性为HwIint,这些寄存器的值由芯片的配置引脚决定,后者上电复位后从EEPROM中获取。Cold和Warm Reset可以复位这些寄存器,然后从EEPROM中从新获取数据,但是使用FLR方式不能复位这些寄存器。

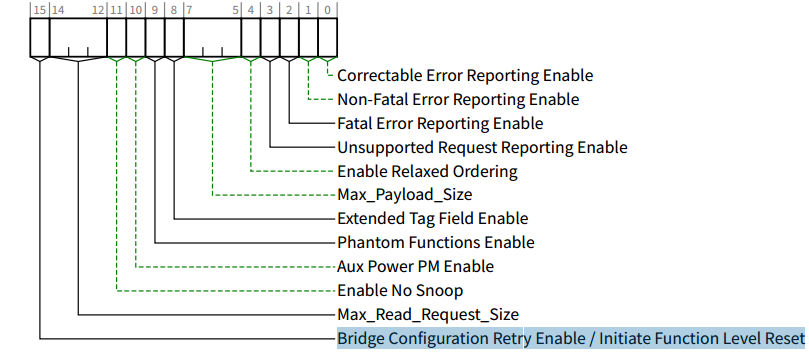

Ø 此外,还有一些特殊的配置寄存器不能被FLR方式复位,如Max_Payload_Size、RCB和一些与电源管理、流量控制和链路控制直接相关的寄存器。

Ø FLR方式不会影响LTSSM状态机。

FLR的机制

FLR只复位对应Function的内部状态和寄存器(使其暂时不变化,Making it quiescent),但是并不影响Sticky bits、有硬件初始化的值(Hardware-initialized bits)和链路专用寄存器(比如Captured Power,ASPM Control、Max Payload Size以及VC等寄存器)。

如果该设备在FLR前,发出了Assert INTx中断消息,必须在开始FLR之前在发出对应的Deassert INTx消息,除非该INTx已经被与其他Function共享了。当收到FLR后,该Function的所有的其他功能都应被立即停止(Required to cease)。

此外,PCIe Spec还明确给出了FLR的完成时间应在100ms以内。

PCIe Spec还明确规定了,当某个Function处于FLR状态时的一些特性:

· 该Function不能有任何与外界通信的(外部)接口;

· 该Function必须将任何软件可读取的状态(可能包括加密信息等)打乱。换句话说,任何内部存储都必须被清零或者随机化;

· 该Function必须可以被另一个Diver配置为一般模式;

· 该Function必须为其收到的包含有FLR信息的配置写(Configuration Write)返回一个Completion,然后再进行FLR操作。

在进入FLR状态后,还需要:

· 该Function接收到的任何请求都应该被直接丢弃,且不登记(Logging),也不报错误。但是FC Credits必须要被更新,以维持链路的正常操作;

· 该Function接收到的任何Completion都应该被当做Unexpected Completions,然后直接丢弃,且不登记,也不报错。

FLR复位代码实现

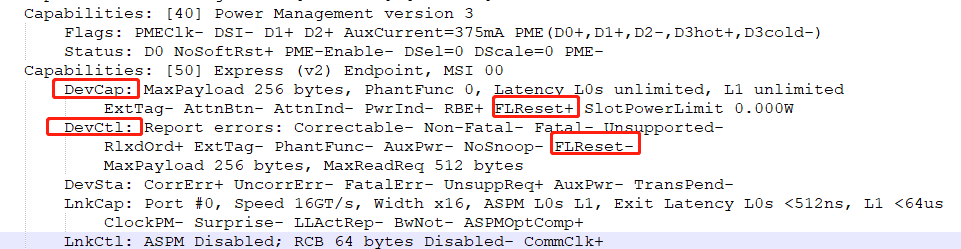

pcie_has_flr检测 Device Capabilities Register (Offset 04h) 是否支持flr功能

pcie_flr 给Device Control Register (Offset 08h) bit[15]写1,然后轮训60s检测是否能重新读取到command配置

pci_reset_function__pci_reset_function_locked(dev);pcie_has_flrpcie_flrpci_wait_for_pending_transaction(dev) // 读取PCIE的状态寄存器,判断是否在pending状态pcie_capability_set_word(dev, PCI_EXP_DEVCTL, PCI_EXP_DEVCTL_BCR_FLR); // 写1复位pci_dev_waitnot ready %dms after %s; waitingnot ready %dms after %s; giving up