PCIE桥的配置空间

参考文档:

- PCI Express Base_r5_1.pdf P7.5.1.3节

- PCI+EXPRESS体系结构导读.pdf P2.3.3节

注:因为配置太多,持续更新中

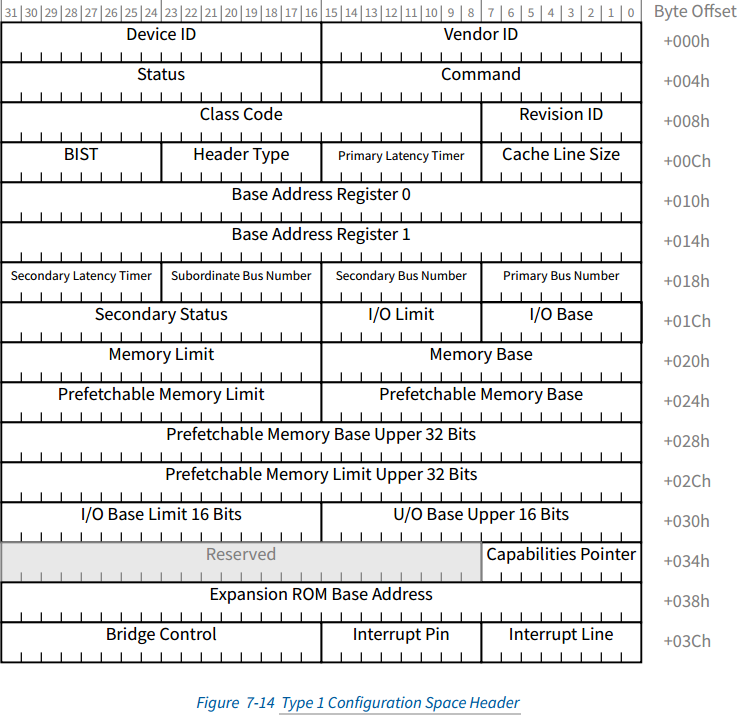

配置空间格式

ID相关

查看ID表(复习)

获取厂家信息:

从pci.ids中进行对比,来查找厂家信息和设备信息。 pci的id表收录在 pci-ids.ucw.cz 中

PCI ID Project at The PCI ID Repository, 注册登陆后(公司是PCI-SIG组织成员),可以增加修改对应device id的描述信息,需要maintainer审批合入后,展示在PCI ID网站上 sudo update-pciids 命令可以更新pci.ids 在此位置/usr/share/misc/pci.ids可以查看更新后pci.ids文件

注:这里边也有Class code表,可以搜索下边关键字

# List of known device classes, subclasses and programming interfaces# Syntax:# C class class_name# subclass subclass_name <-- single tab# prog-if prog-if_name <-- two tabs

Class Code

桥设备的Class Code 在lspci查看时,为: xx xx 06

C 06 Bridge00 Host bridge ###01 ISA bridge02 EISA bridge03 MicroChannel bridge04 PCI bridge ###00 Normal decode01 Subtractive decode05 PCMCIA bridge06 NuBus bridge07 CardBus bridge08 RACEway bridge00 Transparent mode01 Endpoint mode09 Semi-transparent PCI-to-PCI bridge40 Primary bus towards host CPU80 Secondary bus towards host CPU0a InfiniBand to PCI host bridge80 Bridge

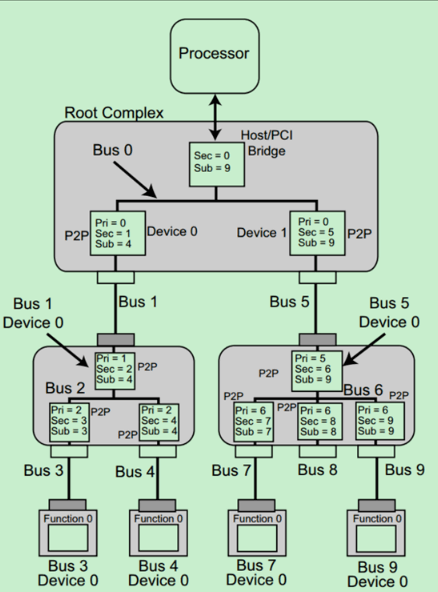

Bus Number相关

sec - secondary bus,下一级bus

pri - primary bus, 上一级bus

sub - subordinate bus,当前总线树的最末级bus号。

IO/MEM BASE/Limit

存放PCI子树中 所有IO/MEM设备的基地址和大小。 MEM的空间大小至少为1M

IO BASE Upper 16BIT/ IO Limit Upper 16BIT

如果PCI仅仅支持16位的IO端口,那么这两个配置只读

如果PCI支持32位的IO端口,那么这两个配置提供了高16位地址。

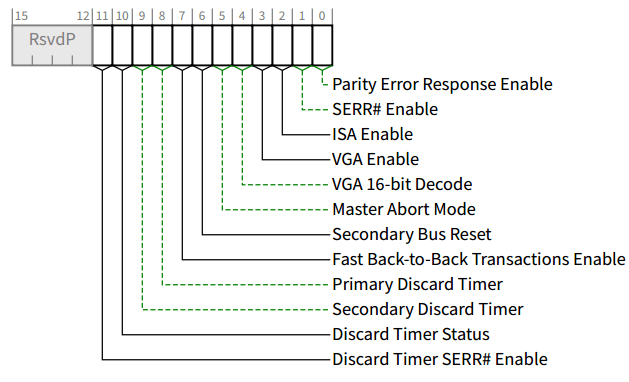

Bridge Control Register

Master Abort Mode

是以前得pci-to-pci bridge, PCIE 必须是是0b, 软件只读

实战解析

(base) baiy@inno-MS-7B89:~$ sudo lspci -s 00:01.1 -vvvvxxxx00:01.1 PCI bridge: Advanced Micro Devices, Inc. [AMD] Device 1483 (prog-if 00 [Normal decode])Control: I/O+ Mem+ BusMaster+ SpecCycle- MemWINV- VGASnoop- ParErr- Stepping- SERR- FastB2B- DisINTx+Status: Cap+ 66MHz- UDF- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- >SERR- <PERR- INTx-Latency: 0, Cache Line Size: 64 bytesInterrupt: pin ? routed to IRQ 26Bus: primary=00, secondary=01, subordinate=01, sec-latency=0I/O behind bridge: 0000f000-00000fffMemory behind bridge: f7900000-f79fffffPrefetchable memory behind bridge: 00000000fff00000-00000000000fffffSecondary status: 66MHz- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort+ <SERR- <PERR-BridgeCtl: Parity- SERR+ NoISA- VGA- MAbort- >Reset- FastB2B-PriDiscTmr- SecDiscTmr- DiscTmrStat- DiscTmrSERREn-Capabilities: [50] Power Management version 3Flags: PMEClk- DSI- D1- D2- AuxCurrent=0mA PME(D0+,D1-,D2-,D3hot+,D3cold+)Status: D0 NoSoftRst- PME-Enable- DSel=0 DScale=0 PME-Capabilities: [58] Express (v2) Root Port (Slot+), MSI 00DevCap: MaxPayload 512 bytes, PhantFunc 0ExtTag+ RBE+DevCtl: Report errors: Correctable+ Non-Fatal+ Fatal+ Unsupported+RlxdOrd+ ExtTag+ PhantFunc- AuxPwr- NoSnoop+MaxPayload 512 bytes, MaxReadReq 512 bytesDevSta: CorrErr- UncorrErr- FatalErr- UnsuppReq- AuxPwr- TransPend-LnkCap: Port #1, Speed 8GT/s, Width x4, ASPM L1, Exit Latency L0s <512ns, L1 <64usClockPM- Surprise- LLActRep+ BwNot+ ASPMOptComp+LnkCtl: ASPM Disabled; RCB 64 bytes Disabled- CommClk+ExtSynch- ClockPM- AutWidDis- BWInt- AutBWInt-LnkSta: Speed 8GT/s, Width x4, TrErr- Train- SlotClk+ DLActive+ BWMgmt+ ABWMgmt-SltCap: AttnBtn- PwrCtrl- MRL- AttnInd- PwrInd- HotPlug- Surprise-Slot #0, PowerLimit 0.000W; Interlock- NoCompl+SltCtl: Enable: AttnBtn- PwrFlt- MRL- PresDet- CmdCplt- HPIrq- LinkChg-Control: AttnInd Unknown, PwrInd Unknown, Power- Interlock-SltSta: Status: AttnBtn- PowerFlt- MRL- CmdCplt- PresDet+ Interlock-Changed: MRL- PresDet- LinkState+RootCtl: ErrCorrectable- ErrNon-Fatal- ErrFatal- PMEIntEna- CRSVisible+RootCap: CRSVisible+RootSta: PME ReqID 0000, PMEStatus- PMEPending-DevCap2: Completion Timeout: Range ABCD, TimeoutDis+, LTR+, OBFF Not Supported ARIFwd-DevCtl2: Completion Timeout: 65ms to 210ms, TimeoutDis-, LTR+, OBFF Disabled ARIFwd-LnkCtl2: Target Link Speed: 8GT/s, EnterCompliance- SpeedDis-Transmit Margin: Normal Operating Range, EnterModifiedCompliance- ComplianceSOS-Compliance De-emphasis: -6dBLnkSta2: Current De-emphasis Level: -3.5dB, EqualizationComplete+, EqualizationPhase1+EqualizationPhase2+, EqualizationPhase3+, LinkEqualizationRequest-Capabilities: [a0] MSI: Enable+ Count=1/1 Maskable- 64bit+Address: 00000000fee00000 Data: 0000Capabilities: [c0] Subsystem: Advanced Micro Devices, Inc. [AMD] Device 1234Capabilities: [c8] HyperTransport: MSI Mapping Enable+ Fixed+Capabilities: [100 v1] Vendor Specific Information: ID=0001 Rev=1 Len=010 <?>Capabilities: [150 v2] Advanced Error ReportingUESta: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-UEMsk: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-UESvrt: DLP- SDES+ TLP- FCP+ CmpltTO- CmpltAbrt- UnxCmplt- RxOF+ MalfTLP- ECRC- UnsupReq- ACSViol-CESta: RxErr- BadTLP- BadDLLP- Rollover- Timeout- NonFatalErr-CEMsk: RxErr- BadTLP- BadDLLP- Rollover- Timeout- NonFatalErr-AERCap: First Error Pointer: 00, GenCap+ CGenEn- ChkCap+ ChkEn-Capabilities: [270 v1] #19Capabilities: [2a0 v1] Access Control ServicesACSCap: SrcValid+ TransBlk+ ReqRedir+ CmpltRedir+ UpstreamFwd+ EgressCtrl- DirectTrans+ACSCtl: SrcValid+ TransBlk- ReqRedir+ CmpltRedir+ UpstreamFwd+ EgressCtrl- DirectTrans-Capabilities: [370 v1] L1 PM SubstatesL1SubCap: PCI-PM_L1.2- PCI-PM_L1.1+ ASPM_L1.2- ASPM_L1.1+ L1_PM_Substates+L1SubCtl1: PCI-PM_L1.2- PCI-PM_L1.1- ASPM_L1.2- ASPM_L1.1-L1SubCtl2:Capabilities: [3c4 v1] #23Capabilities: [400 v1] #25Capabilities: [410 v1] #26Capabilities: [440 v1] #27Kernel driver in use: pcieport00: 22 10 83 14 07 04 10 00 00 00 04 06 10 00 81 0010: 00 00 00 00 00 00 00 00 00 01 01 00 f1 01 00 2020: 90 f7 90 f7 f1 ff 01 00 00 00 00 00 00 00 00 0030: 00 00 00 00 50 00 00 00 00 00 00 00 ff 00 12 0040: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 0050: 01 58 03 c8 00 00 00 00 10 a0 42 01 22 80 00 0060: 5f 29 00 00 43 38 73 01 40 00 43 70 00 00 04 0070: 00 00 40 01 10 00 01 00 00 00 00 00 df 19 70 0080: 06 04 00 00 0e 00 00 00 03 00 1f 00 00 00 00 0090: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00a0: 05 c0 81 00 00 00 e0 fe 00 00 00 00 00 00 00 00b0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00c0: 0d c8 00 00 22 10 34 12 08 00 03 a8 00 00 00 00d0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00e0: 00 00 00 00 ff ff ff ff 00 00 00 00 00 00 00 00f0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00