上拉电阻和下拉电阻二者共同的作用是:避免电压的“悬浮”,造成电路的不稳定。

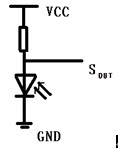

一、上拉电阻如图所示:

1、概念:将一个不确定的信号,通过一个电阻与电源VCC相连,固定在高电平;

2、上拉是对器件注入电流,灌电流;

3、当一个接有上拉电阻的IO端口设置为输入状态时,它的常态为高电平。

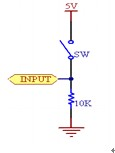

二、下拉电阻如图所示:

1、 概念:将一个不确定的信号,通过一个电阻与地GND相连,固定在低电平;

2、下拉是从器件输出电流,拉电流;

3、当一个接有下拉电阻的IO端口设置为输入状态时,它的常态为低电平。

三、小应用:

1.对于一些高输入阻抗的电路,引脚悬空容易受到外界的干扰(即使是很低的能量耦合至电路),此时设置上下拉电阻提供了一个相对低阻的通路。因为在低阻上产生一定的电压所需的能量是比高阻的情况大得多的,这就减少了一部分能量较弱的干扰信号的影响,降低受干扰的概率。

2.对于COMS输入,为防止静电击穿,设置一个上或下拉电阻,提供一个相对的低阻回路,以泄放存储的电荷,不让电压积累。

3.对于高速电路,传输线效应开始显现,设置上下拉电阻主要用以阻抗匹配,减少反射,保证电平能够被正确读写。

4.加上下拉电阻确定电平状态,输入或输出可能存在偏流,设置上下拉电阻使偏流流经电阻产生一固定的状态的偏置电压。

对于输入来说,偏流极小,即使悬空高阻下可能会有相对较大的输入电压,且不稳定,加下拉,偏流流过电阻产生的压降仍极小,可认为将输入电平确定为低。

对于输出来说,通常针对的是集电极(漏极)开路(OC)的情况,加上拉电阻确定输出电压的变动范围。

上述的情况也不过是普遍上的一种描述,真正上下拉电阻的作用还是得根据具体的问题进行分析,有的时候加个上拉也许只会为了获得与其他部件不同的微量的延迟,难以穷举。多在实践中分析和体会吧。

我的GitHub地址:https://github.com/heizemingjun

我的博客园地址:http://www.cnblogs.com/chenmingjun

我的蚂蚁笔记博客地址:http://blog.leanote.com/chenmingjun