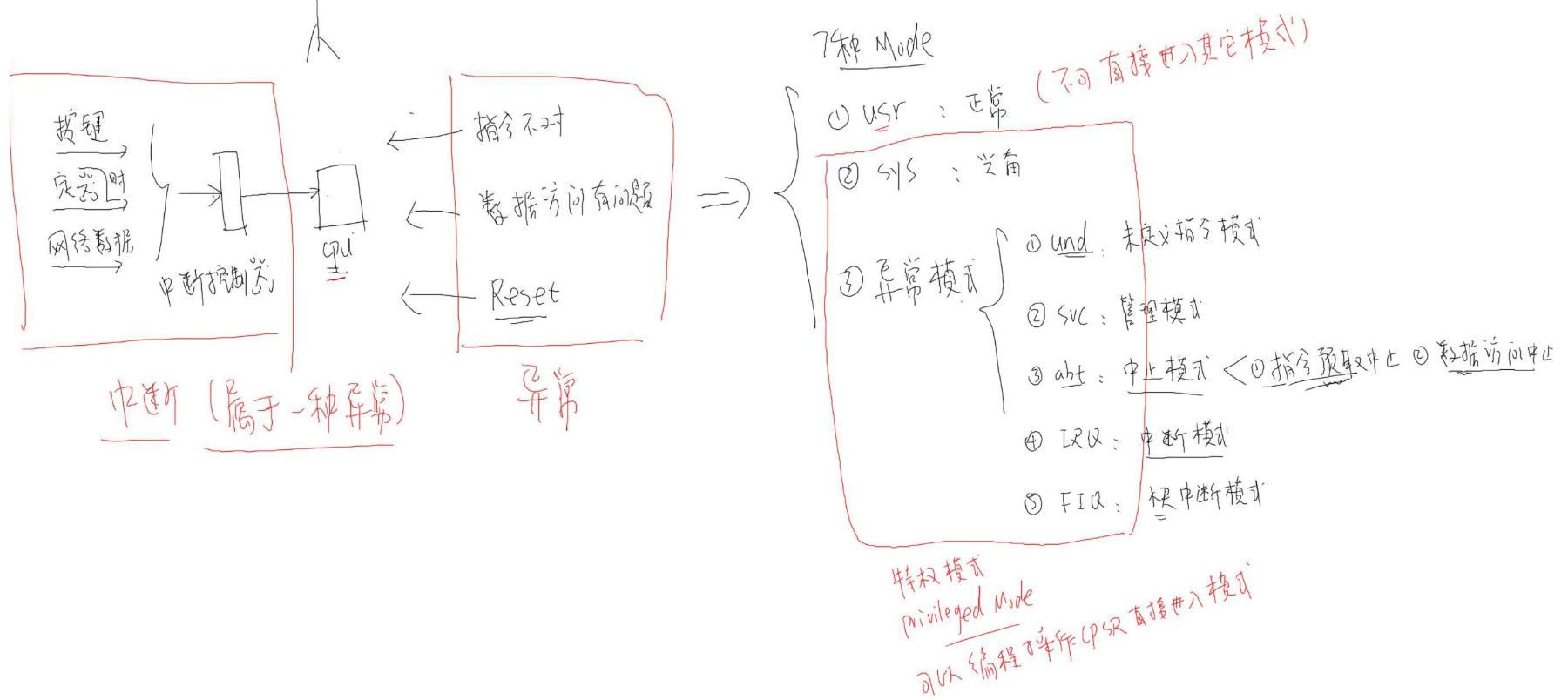

- ARM9和cortex A7的CPU模式、状态、寄存器,以及发生异常时的处理细节,几乎是一模一样的

- 跟ARM9相比,多了2中Mode:Monitor、Hyp

- 除usr模式外,其他模式是特权模式。usr模式下,无法通过修改CPSR寄存器进入其他模式。在其他模式下,可以通过修改CPSR寄存器进入其他模式(特权模式下各模式之间可以任意切换)

- 某一个中断可以配置为快中断,从而进入快中断FIQ模式

- ARM芯片为什么会有这么多模式?

- 显然,发生某种异常时会进入对应的异常模式;在异常模式下更容易处理这种异常

- 每种模式下都有什么差别呢?

- 实际上都是寄存器的差别

- 异常模式下的LR寄存器用来保存发生异常时的指令地址,以后返回时就返回该地址所指示的地方

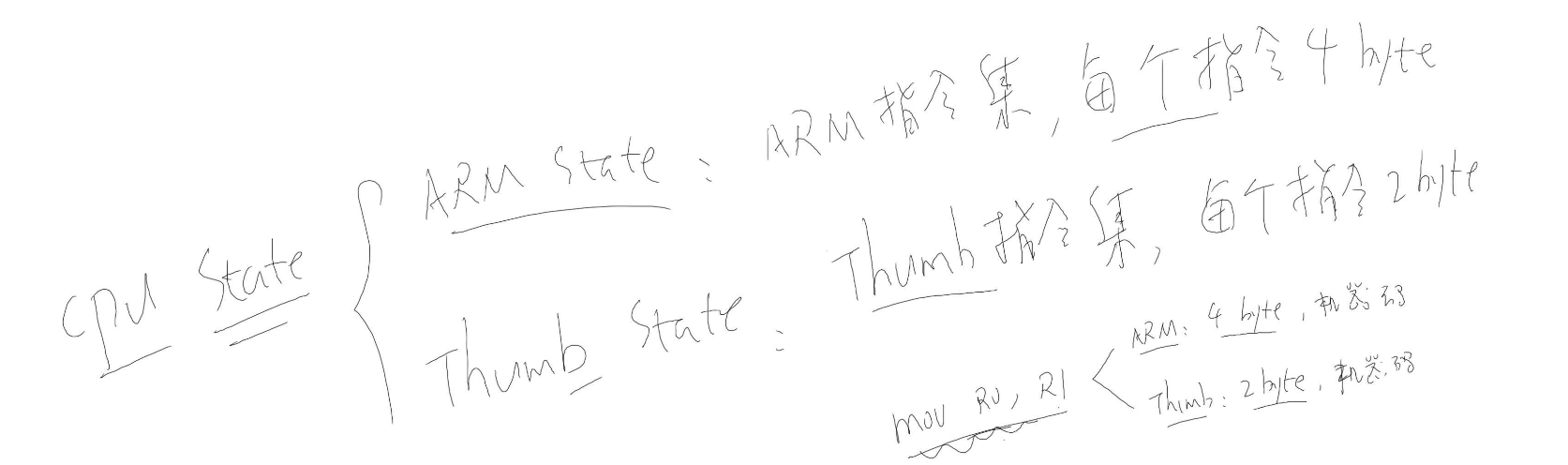

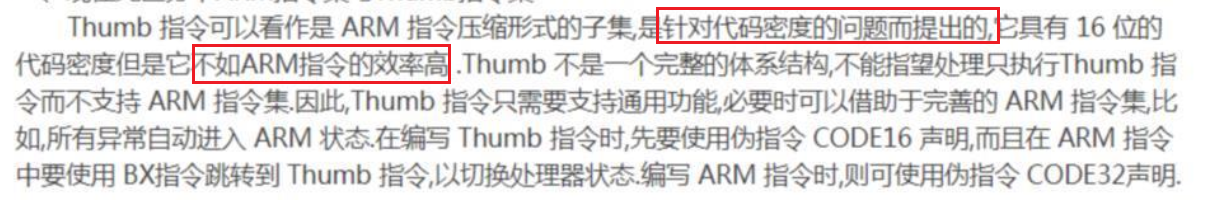

- ARM架构CPU有ARM state和Thumb state两种CPU执行状态

- Thumb state的指令密度更高,ARM state的执行效率更高

- CPSR状态寄存器:

- 低5bit(bit0-bit4)用来表示处于什么模式,当处于特权模式时还可以修改这5bit来切换模式(当然,用户模式下是没有权限修改的)

- bit5表示工作模式:ARM或Thumb

- bit7是IRQ中断的总开关,只有enable时CPU才能感知到中断控制器发来的中断

- bit28-bit31是状态位,用来记录程序执行过程中的状态

- 发生异常时,这些寄存器是如何协同工作的呢?

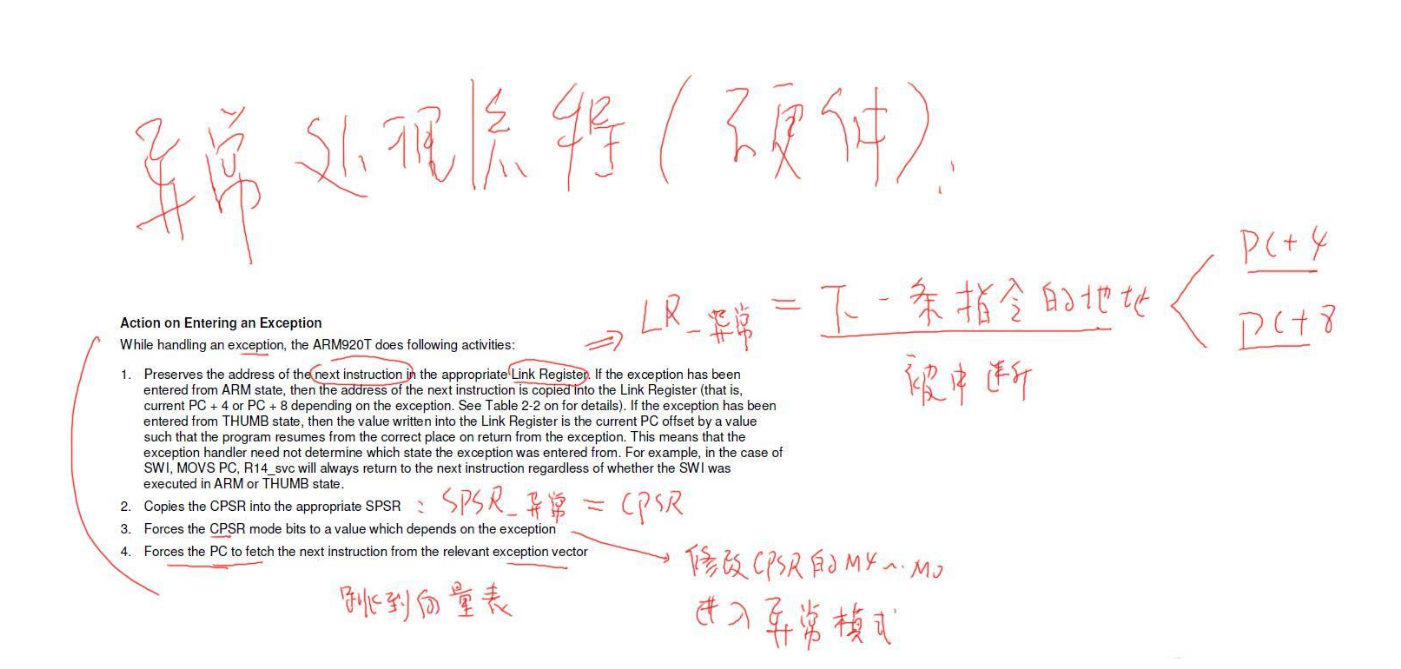

- 异常处理流程中进入异常时硬件部分的实现:

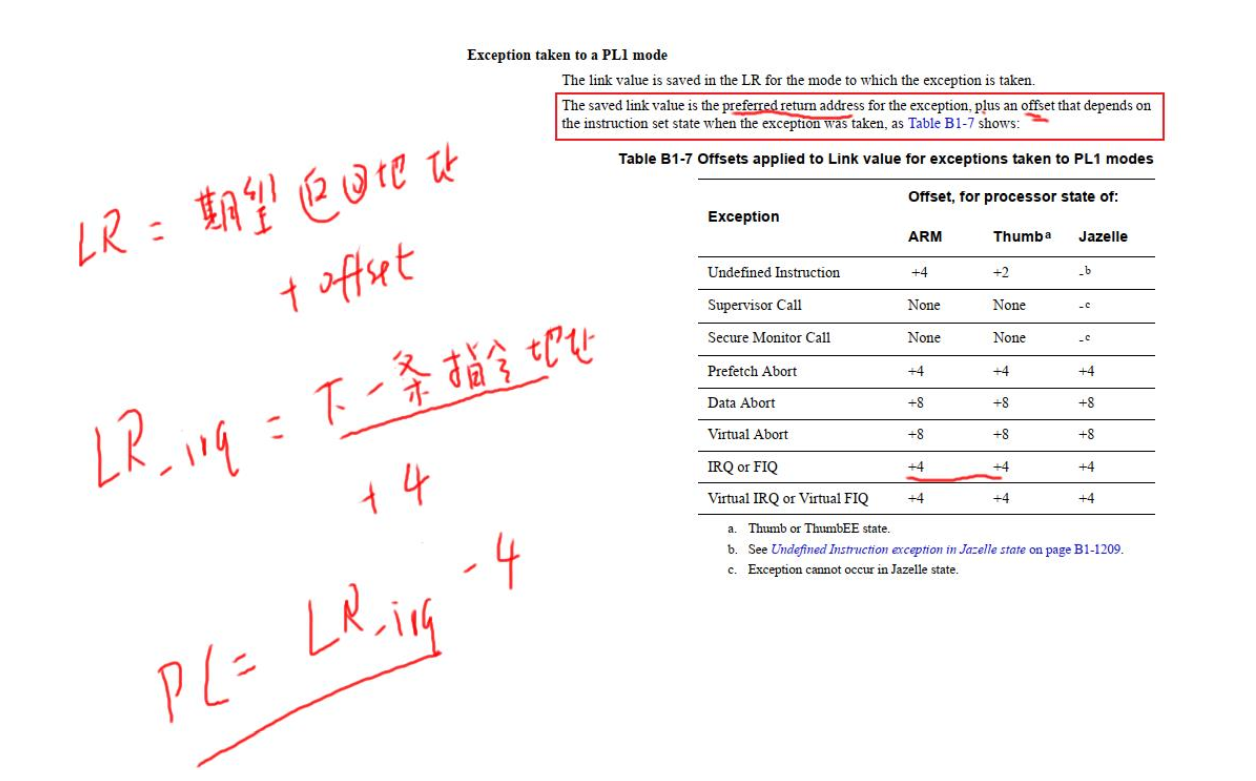

- 发生异常时,把下一条指令的地址保存在LR寄存器中,可能是PC+4或者PC+8;到底是哪个取决于不同的情况

- 把CPSR保存到SPSR中;然后修改CPSR的模式位进入异常模式

- 跳转到向量表

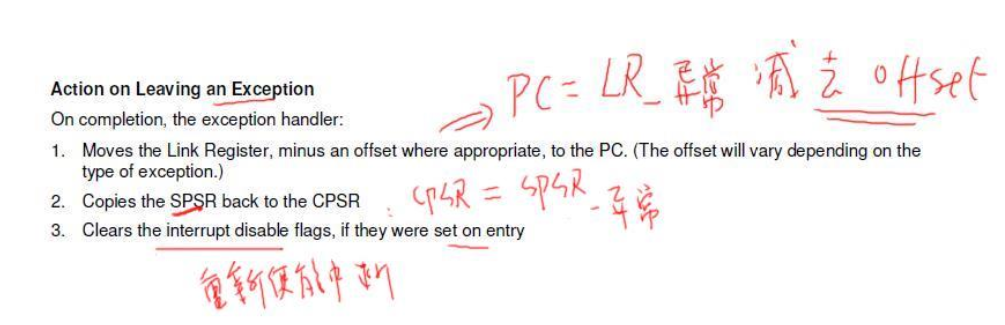

- 退出异常时硬件部分的实现:

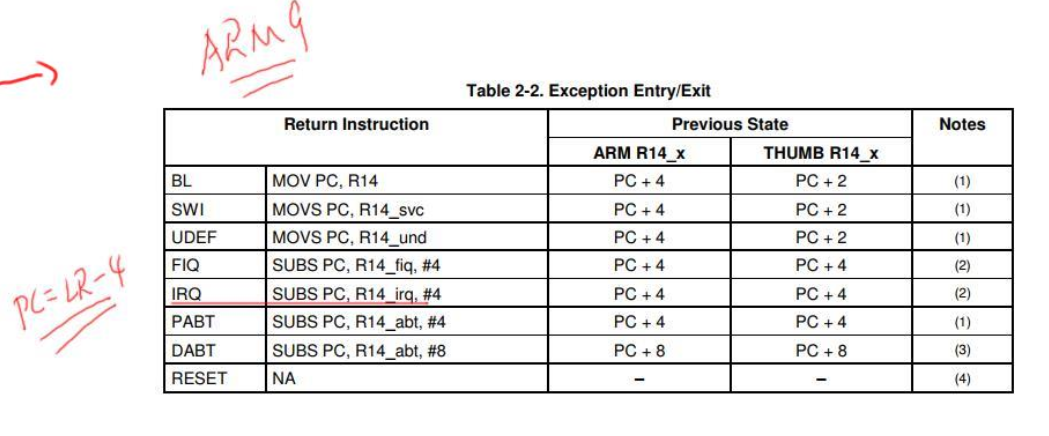

- 将LR寄存器的值减去一个offset赋给PC;减去的offset可通过查表得知

- 将SPSR的值恢复到CPSR中

- 重新使能中断

- 异常处理流程中进入异常时硬件部分的实现:

- 对于ARM9和A7,返回时的地址offset有些差别

- 对于ARM9

- 对于A7:

- 对于ARM9

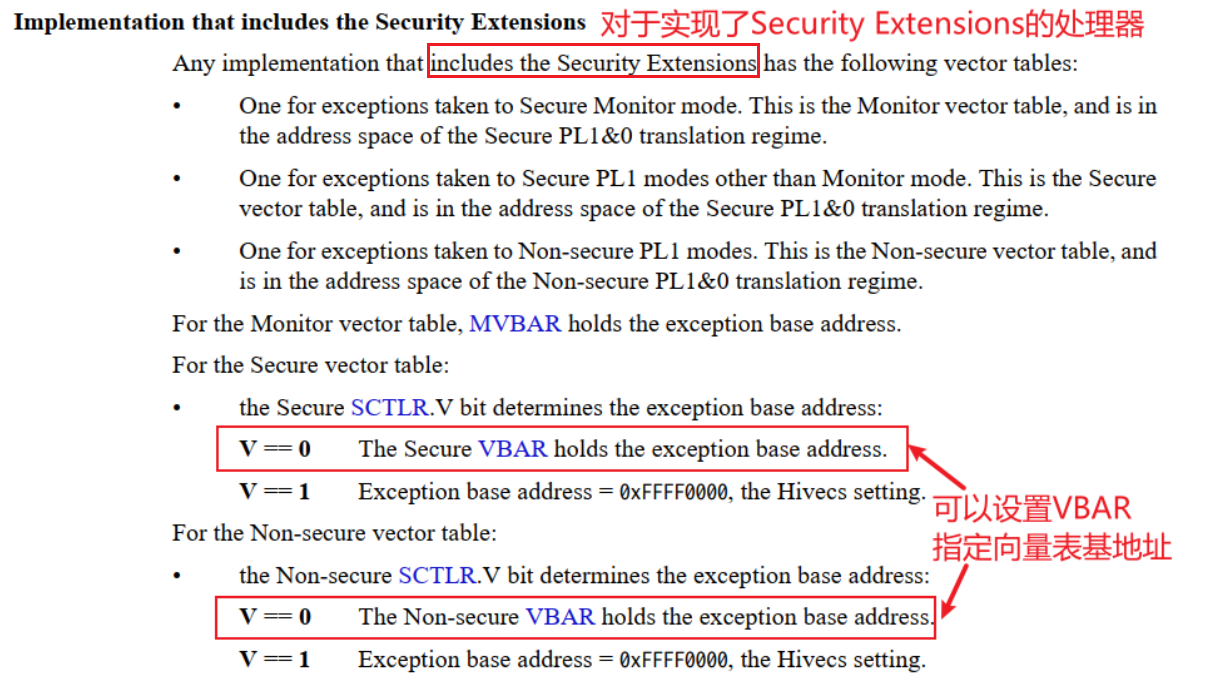

- 在ARM9里,异常向量表基地址只有两个取值:0、0xFFFF0000。对于cortex A7,它的异常向量表基地址是可以修改的

发生异常时,我们的CPU会做什么事情

- 硬件确定要进入哪种异常模式

- LR寄存器被更新,它表示处理完异常后要返回到哪里,这个值可能需要修改。

- SPSR = 被中断时的CPSR

- 对于”Security Exceptions”,……,本课程不涉及

- 更新异常模式下的CPSR:设置模式位、设置mask bit(屏蔽其他异常)、设置指令集状态位

- PC = 异常入口地址

- 从PC所指示地方执行程序

从异常中退出,要做什么事情?

- 让LR减去某个值,然后赋值给PC(PC = 某个异常LR寄存器减去 offset)

减去什么值呢?

也就是我们怎么返回去继续执行原来的程序,根据下面这个表来取值:

如果发生的是SWI可以把 R14_svc复制给PC

如果发生的是IRQ可以把R14_irq的值减去4赋值给PC - 把CPSR的值恢复(CPSR 值等于 某一个一场模式下的SPSR)

- 清中断(如果是中断的话,对于其他异常不用设置)

- 让LR减去某个值,然后赋值给PC(PC = 某个异常LR寄存器减去 offset)

参考:

《ARM体系结构与编程》作者:杜春雷ARM ArchitectureReference Manual ARMv7-A and ARMv7-R edition.pdfS3C2440A_UserManual_Rev13.pdf:没错,这个手册里描述得更清晰