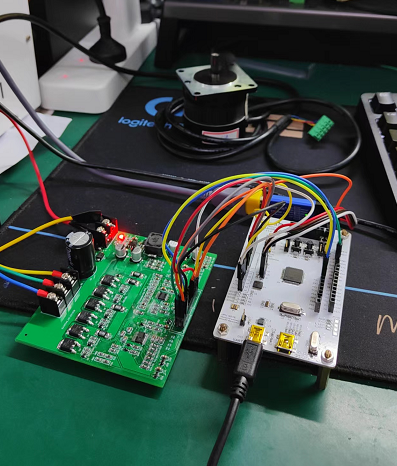

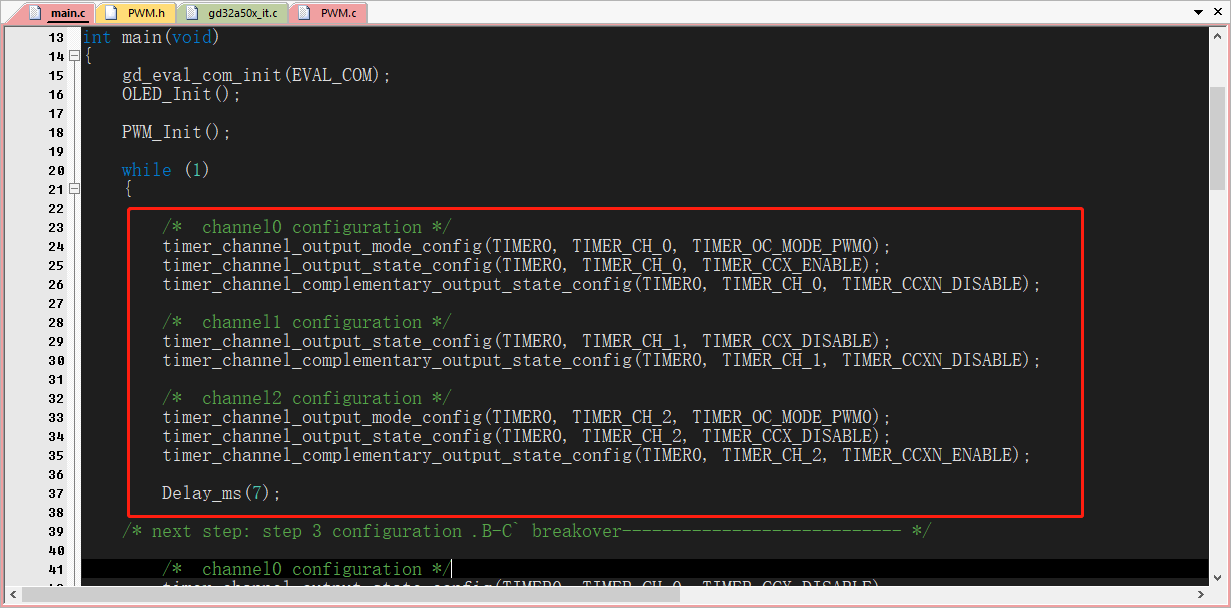

想让电机转起来,最粗暴的方式就是直接在主循环中进行六步换相,当然每一步之间最好有个延时,不然也转不起来。

#include "gd32a50x.h"#include "systick.h"#include "gd32a503r_start.h"#include <stdio.h>#include "main.h"#include "OLED.h"#include "PWM.h"__IO uint32_t step = 1;int main(void){gd_eval_com_init(EVAL_COM);OLED_Init();PWM_Init();while (1){/* channel0 configuration */timer_channel_output_mode_config(TIMER0, TIMER_CH_0, TIMER_OC_MODE_PWM0);timer_channel_output_state_config(TIMER0, TIMER_CH_0, TIMER_CCX_ENABLE);timer_channel_complementary_output_state_config(TIMER0, TIMER_CH_0, TIMER_CCXN_DISABLE);/* channel1 configuration */timer_channel_output_state_config(TIMER0, TIMER_CH_1, TIMER_CCX_DISABLE);timer_channel_complementary_output_state_config(TIMER0, TIMER_CH_1, TIMER_CCXN_DISABLE);/* channel2 configuration */timer_channel_output_mode_config(TIMER0, TIMER_CH_2, TIMER_OC_MODE_PWM0);timer_channel_output_state_config(TIMER0, TIMER_CH_2, TIMER_CCX_DISABLE);timer_channel_complementary_output_state_config(TIMER0, TIMER_CH_2, TIMER_CCXN_ENABLE);Delay_ms(7);/* next step: step 3 configuration .B-C` breakover---------------------------- *//* channel0 configuration */timer_channel_output_state_config(TIMER0, TIMER_CH_0, TIMER_CCX_DISABLE);timer_channel_complementary_output_state_config(TIMER0, TIMER_CH_0, TIMER_CCXN_DISABLE);/* channel1 configuration */timer_channel_output_mode_config(TIMER0, TIMER_CH_1, TIMER_OC_MODE_PWM0);timer_channel_output_state_config(TIMER0, TIMER_CH_1, TIMER_CCX_ENABLE);timer_channel_complementary_output_state_config(TIMER0, TIMER_CH_1, TIMER_CCXN_DISABLE);/* channel2 configuration */timer_channel_output_mode_config(TIMER0, TIMER_CH_2, TIMER_OC_MODE_PWM0);timer_channel_output_state_config(TIMER0, TIMER_CH_2, TIMER_CCX_DISABLE);timer_channel_complementary_output_state_config(TIMER0, TIMER_CH_2, TIMER_CCXN_ENABLE);Delay_ms(7);/* next step: step 4 configuration .B-A` breakover---------------------------- *//* channel0 configuration */timer_channel_output_mode_config(TIMER0, TIMER_CH_0, TIMER_OC_MODE_PWM0);timer_channel_output_state_config(TIMER0, TIMER_CH_0, TIMER_CCX_DISABLE);timer_channel_complementary_output_state_config(TIMER0, TIMER_CH_0, TIMER_CCXN_ENABLE);/* channel1 configuration */timer_channel_output_mode_config(TIMER0, TIMER_CH_1, TIMER_OC_MODE_PWM0);timer_channel_output_state_config(TIMER0, TIMER_CH_1, TIMER_CCX_ENABLE);timer_channel_complementary_output_state_config(TIMER0, TIMER_CH_1, TIMER_CCXN_DISABLE);/* channel2 configuration */timer_channel_output_state_config(TIMER0, TIMER_CH_2, TIMER_CCX_DISABLE);timer_channel_complementary_output_state_config(TIMER0, TIMER_CH_2, TIMER_CCXN_DISABLE);Delay_ms(7);/* next step: step 5 configuration .C-A` breakover---------------------------- *//* channel0 configuration */timer_channel_output_mode_config(TIMER0, TIMER_CH_0, TIMER_OC_MODE_PWM0);timer_channel_output_state_config(TIMER0, TIMER_CH_0, TIMER_CCX_DISABLE);timer_channel_complementary_output_state_config(TIMER0, TIMER_CH_0, TIMER_CCXN_ENABLE);/* channel1 configuration */timer_channel_output_state_config(TIMER0, TIMER_CH_1, TIMER_CCX_DISABLE);timer_channel_complementary_output_state_config(TIMER0, TIMER_CH_1, TIMER_CCXN_DISABLE);/* channel2 configuration */timer_channel_output_mode_config(TIMER0, TIMER_CH_2, TIMER_OC_MODE_PWM0);timer_channel_output_state_config(TIMER0, TIMER_CH_2, TIMER_CCX_ENABLE);timer_channel_complementary_output_state_config(TIMER0, TIMER_CH_2, TIMER_CCXN_DISABLE);Delay_ms(7);/* next step: step 6 configuration .C-B` breakover---------------------------- *//* channel0 configuration */timer_channel_output_state_config(TIMER0, TIMER_CH_0, TIMER_CCX_DISABLE);timer_channel_complementary_output_state_config(TIMER0, TIMER_CH_0, TIMER_CCXN_DISABLE);/* channel1 configuration */timer_channel_output_mode_config(TIMER0, TIMER_CH_1, TIMER_OC_MODE_PWM0);timer_channel_output_state_config(TIMER0, TIMER_CH_1, TIMER_CCX_DISABLE);timer_channel_complementary_output_state_config(TIMER0, TIMER_CH_1, TIMER_CCXN_ENABLE);/* channel2 configuration */timer_channel_output_mode_config(TIMER0, TIMER_CH_2, TIMER_OC_MODE_PWM0);timer_channel_output_state_config(TIMER0, TIMER_CH_2, TIMER_CCX_ENABLE);timer_channel_complementary_output_state_config(TIMER0, TIMER_CH_2, TIMER_CCXN_DISABLE);Delay_ms(7);/* next step: step 1 configuration .A-B` breakover---------------------------- *//* channel0 configuration */timer_channel_output_mode_config(TIMER0, TIMER_CH_0, TIMER_OC_MODE_PWM0);timer_channel_output_state_config(TIMER0, TIMER_CH_0, TIMER_CCX_ENABLE);timer_channel_complementary_output_state_config(TIMER0, TIMER_CH_0, TIMER_CCXN_DISABLE);/* channel1 configuration */timer_channel_output_mode_config(TIMER0, TIMER_CH_1, TIMER_OC_MODE_PWM0);timer_channel_output_state_config(TIMER0, TIMER_CH_1, TIMER_CCX_DISABLE);timer_channel_complementary_output_state_config(TIMER0, TIMER_CH_1, TIMER_CCXN_ENABLE);/* channel2 configuration */timer_channel_output_state_config(TIMER0, TIMER_CH_2, TIMER_CCX_DISABLE);timer_channel_complementary_output_state_config(TIMER0, TIMER_CH_2, TIMER_CCXN_DISABLE);Delay_ms(7);}}/* retarget the C library printf function to the USART */int fputc(int ch, FILE *f){usart_data_transmit(EVAL_COM, (uint8_t)ch);while(RESET == usart_flag_get(EVAL_COM, USART_FLAG_TBE));return ch;}