:::danger

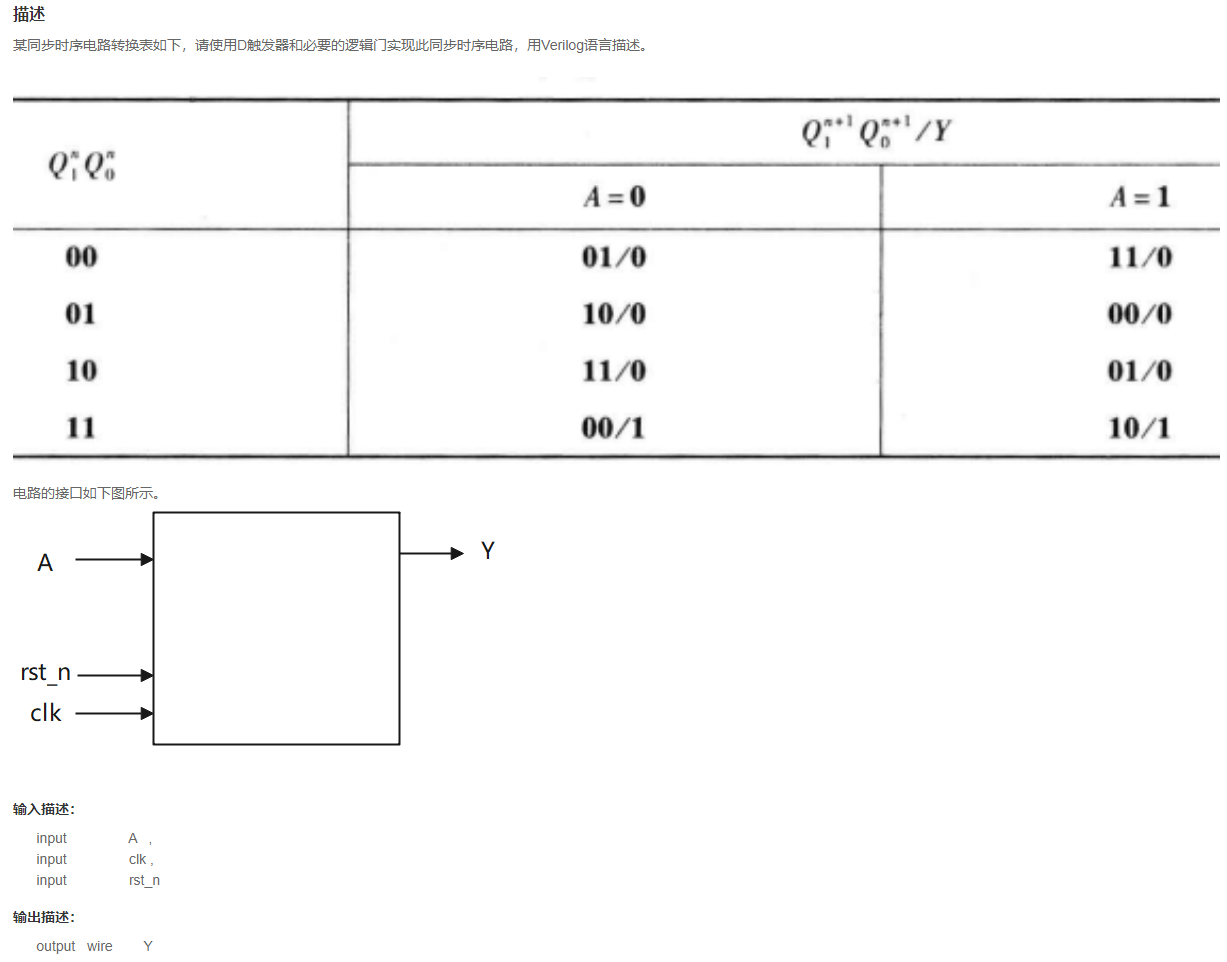

对于时序逻辑电路而言,我们倾向于采用状态机的方式进行解决,当然也可以对逻辑表达式进行化简以后使用转移方式来解决。

:::

:::danger

分析:

:::danger

分析:

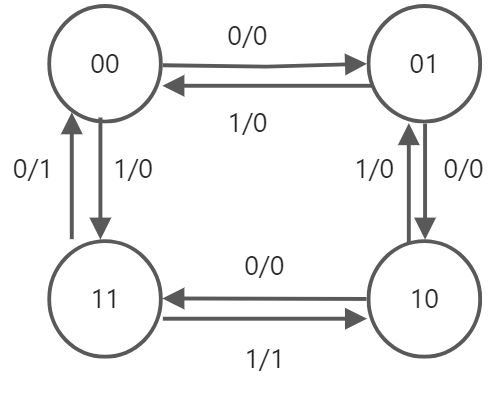

初态为00状态,当输入为0,次态就是01状态并且输出0;

当输入为1,次态就是11状态并且输出0;

以此类推。在实际观察状态转换图的时候,要抓输出为1的状态:即如果现态是11状态,那么当输入为0的时候,次态就是00并且会输出1,当输入为1的时候,次态就是10且会输出1。

:::

FSM实例主要是三段式状态机,其写法可以参考:有限同步状态机

解答:

首先根据状态转换表绘制出状态转换图

`timescale 1ns/1nsmodule seq_circuit(input A,input clk,input rst_n,output wire Y);reg [1:0] cur_state;reg [1:0] nex_state;always @(posedge clk or negedge rst_n) beginif(!rst_n) begincur_state <= 2'b00;nex_state <= 2'b00;endelse begincur_state <= nex_state;endendalways @(*) begincase(cur_state)2'b00 : nex_state = (A == 0)? 2'b01: 2'b11;2'b01 : nex_state = (A == 0)? 2'b10: 2'b00;2'b10 : nex_state = (A == 0)? 2'b11: 2'b01;2'b11 : nex_state = (A == 0)? 2'b00: 2'b10;default : nex_state = 2'b00;endcaseendassign Y = (cur_state == 2'b11)? 1:0;endmodule