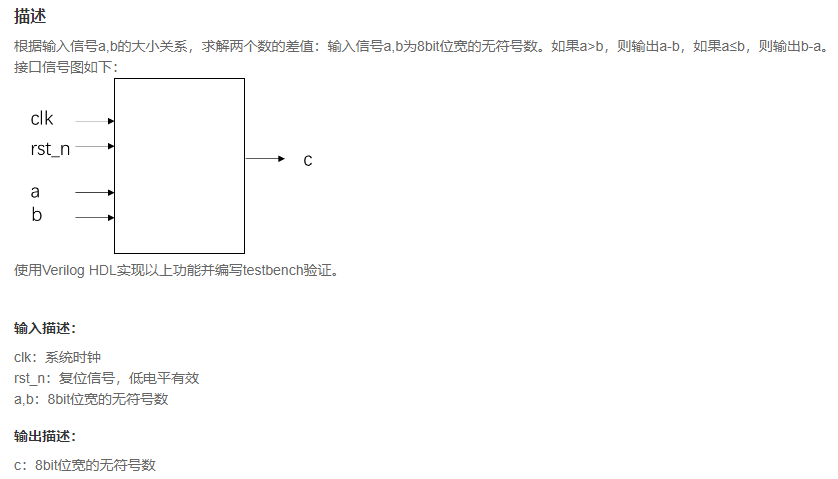

`timescale 1ns/1nsmodule data_minus(input clk,input rst_n,input [7:0]a,input [7:0]b,output reg [8:0]c);//**************code********************//always @(posedge clk or negedge rst_n) beginif(!rst_n) beginc <= 9'b0;endelse beginif(a > b) beginc <= a - b;endelse beginc <= b - a;endendend//**************code********************//endmodule