`timescale 1ns/1nsmodule Tff_2(input wire data, clk, rst,output reg q);//------------------code-------------------reg q1;always @(posedge clk or negedge rst) beginif(!rst) beginq1 <= 1'b0;q <= 1'b0;endelse if(data) beginq1 <= !q1;if(q1) beginq <= !q;endelse beginq <= q;endendelse if(!data) beginq1 <= q1;if(q1) beginq <= !q;endelse beginq <= q;endendend//------------------code-------------------endmodule`timescale 1ns/1nsmodule Tff_2(input wire data, clk, rst,output reg q);//------------------code-------------------reg q1;always @(posedge clk or negedge rst) beginif(!rst) beginq1 <= 1'b0;q <= 1'b0;endelse if(data) beginq1 <= !q1;if(q1) beginq <= !q;endelse beginq <= q;endendelse if(!data) beginq1 <= q1;if(q1) beginq <= !q;endelse beginq <= q;endendend//------------------code-------------------endmodulemodule Tff_2(input wire data, clk, rst,output reg q);//------------------code-------------------reg q1;always @(posedge clk or negedge rst) beginif(!rst) beginq1 <= 1'b0;endelse beginif(data)q1 <= ~q1;elseq1 <= q1;endendalways @(posedge clk or negedge rst) beginif(!rst) beginq <= 1'b0;endelse beginif(q1)q <= ~q;elseq <= q;endend//------------------code-------------------endmodule

更倾向于接法2,将两个触发器分开写复位和触发信号。

:::info

:::info

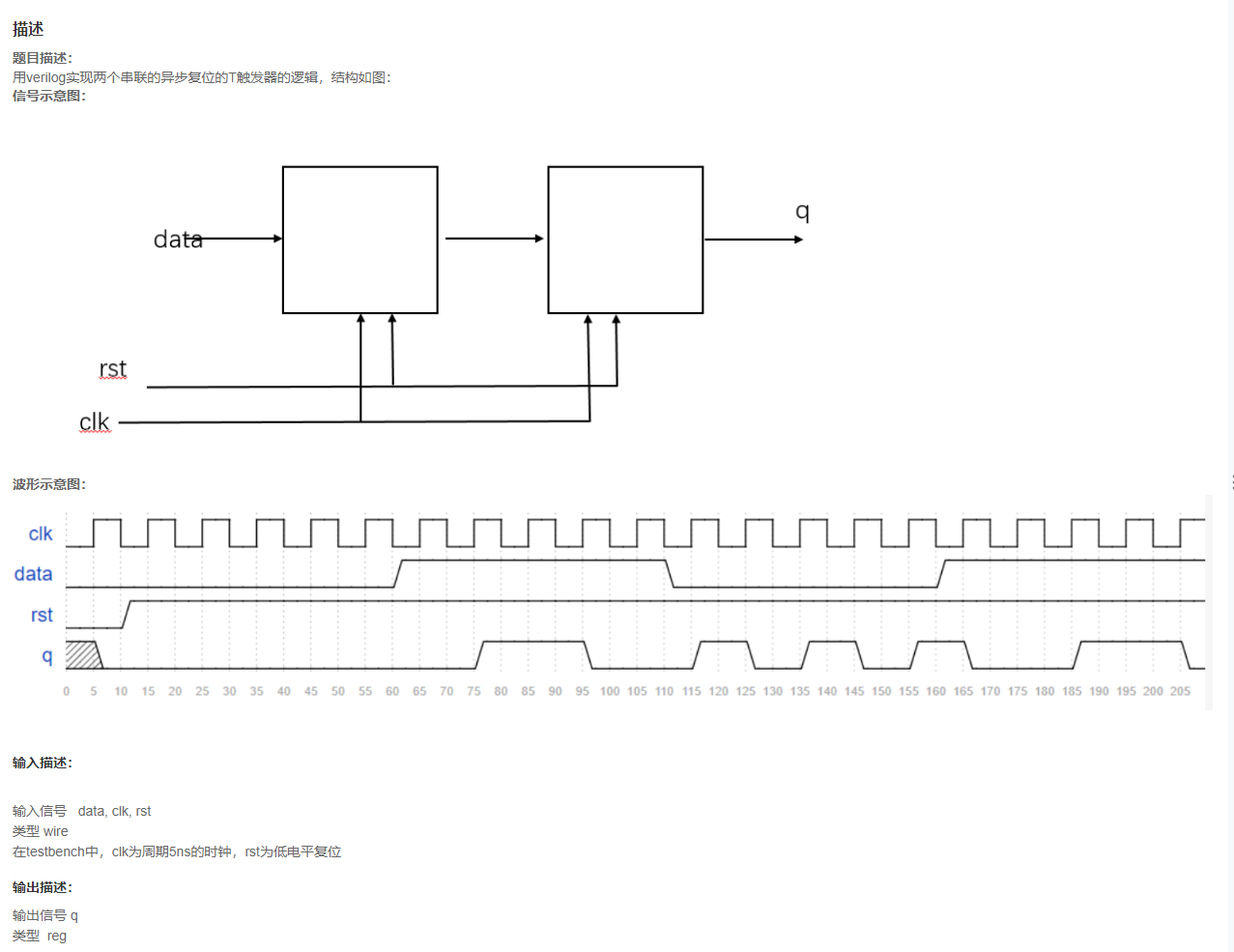

- 异步复位需要一个时钟和复位的边沿信号来触发;

- 复位信号是高电平或低电平有效?需要观察波形来决定;

- 如果要检测这个电平,就需要通过边沿进入电平触发来检测异步复位;

- T触发器和D触发器的基本理解;

- 异步复位是如何实现的:

在always块的敏感事件列表中,如果去掉复位信号,那么检测到复位信号的时候就不再会进行触发,只有在if语句中检测到复位信号才会触发复位。

- 如果复位信号是低电平复位,那么应当在标准的复位信号应当是rst_n,n表示negedge。 ::: 如果要改成同步复位,那么去掉敏感时间列表中的复位信号即可。