7.2.1 scoreboard开关特性控制

之前在scoreboard中添加了loadcounter_enable来控制scoreboard中do_loadcounter_check的开关特性。

同时在配置阶段我们在config中配置了控制scoreboard开关特性的变量scb_enable。

:::info

修改scoreboard来控制其开关特性

:::

`ifndef APB_WATCHDOG_SCOREBOARD_SV`define APB_WATCHDOG_SCOREBOARD_SVclass apb_watchdog_scoreboard extends apb_watchdog_subscriber;...virtual task do_loadcounter_check();bit loadcounter_enable = do_loadcounter_en(CHECK_COUNTEREN);forever begin@(posedge vif.wdg_clk iff loadcounter_enable);cur_load = rgm.WDOGLOAD.LOADVAL.get();cur_count = cur_load;do begin@(posedge vif.wdg_clk);cur_count--;end while(cur_count != 0);wdg_reg_intr_assert_e.trigger();repeat(2) @(negedge vif.wdg_clk);// From logic timing after count reach zeroif(vif.wdog_int != 1'b1) begincfg.scb_check_error++;`uvm_error("COUNTDOWN_CHECK", "Wdog interrupt signal should be asserted!")endcfg.scb_check_count++;endendtaskvirtual function bit do_loadcounter_en(check_type_e typ);case(typ)CHECK_COUNTEREN: return cfg.scb_enable && cfg.do_counter_check_en && wdg_inten;default: return 0;endcaseendfunctionendclass`endif // APB_WATCHDOG_SCOREBOARD_SV

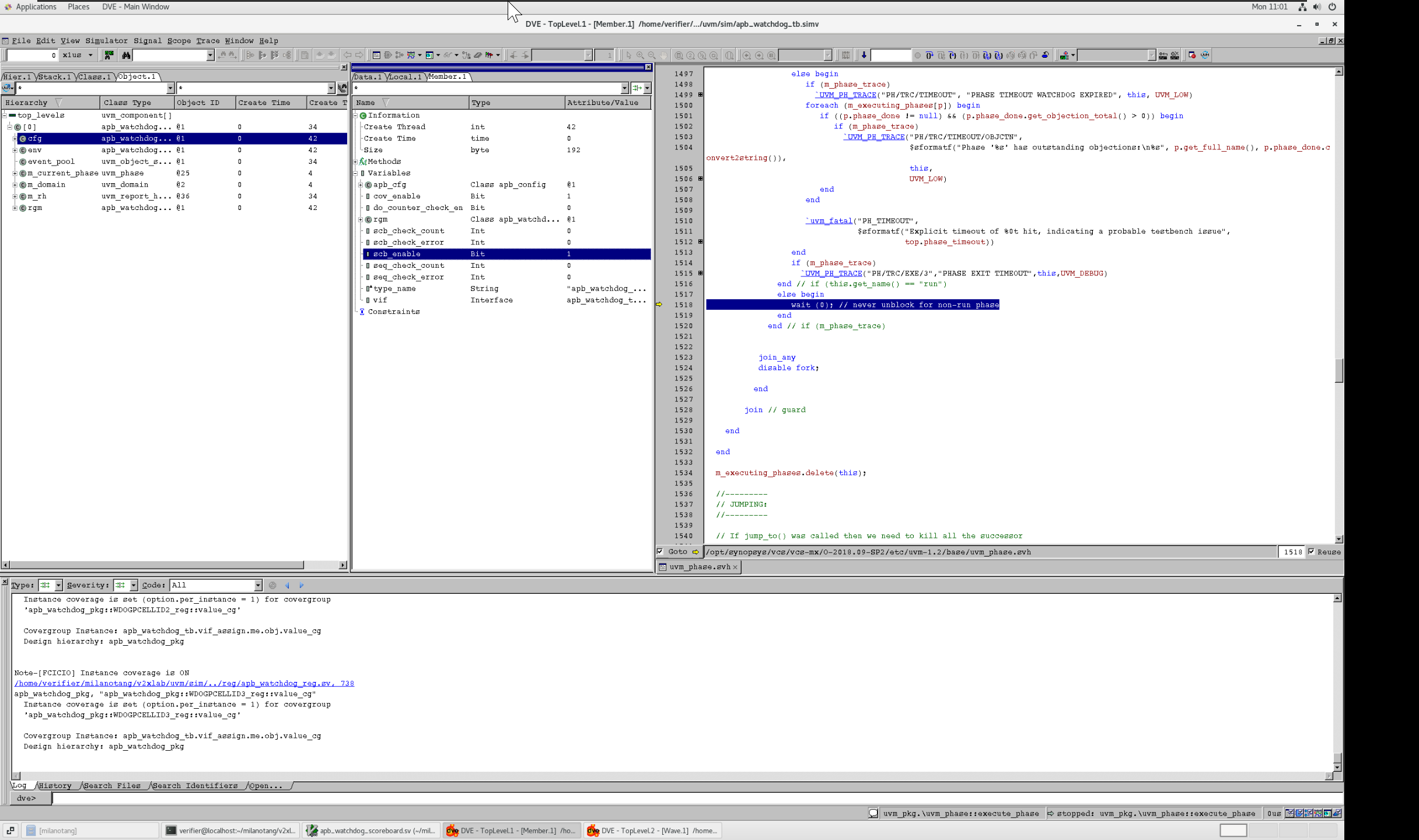

build_phase中的enable在前期是一个快照的作用,到了后期就没有什么影响了; cfg.scb_enable是整个scoreboard的开关,couter_check_en是循环计数功能的开关,wdg_inten是使能int的功能开关。

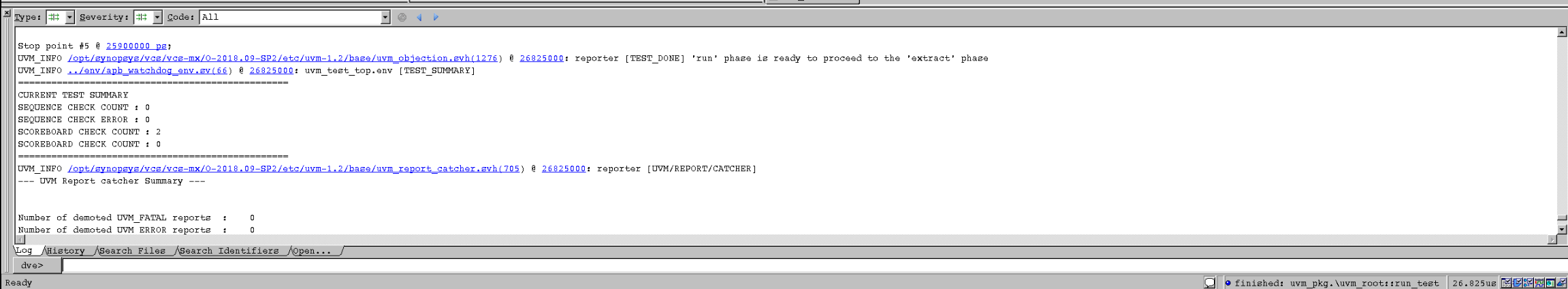

在cfg中配置了scb_enable以后就可以在仿真的时候对enable的值进行修改,进而进一步对scoreboard的开关特性进行调整

在uvm_objects里可以查找到与config有关的动态变量,通过修改其中enable的值可以关闭scoreboard的开关特性,进而可以让波形正常跑出。

:::danger

【思考】

代测功能:counter计数到0以后,INT信号拉高并reload,如果之后将INT_CLR,counter从0开始计数,这时的状态应该是回退到从FF开始计数的状态并且等待下一次reset拉高,而不是回退到一开始的reprogram的阶段。

代测功能:INT拉高以后,在counter记到0之前,做了一次INTCLR以后会退到状态机的哪一步?

:::

7.2.2 scoreboard的reset功能检查

:::info

- 在scoreboard中添加reset的使能信号;

- 添加int_check和res_check两个信号;

- 完成对于加入reset以后整个状态机的描述。

:::

- 如果reset做过了检查,那么WDOGRES信号拉高,就没有必要再做其他检查;

- 如果reset信号没有被使能,那么就一直检查INT信号;

- 如果reset信号已经被使能且完成了一次INT信号的检查,那么就进入reset信号的检查部分,这与状态机也是相符的。

【调试及结果】