:::danger 【知识点】

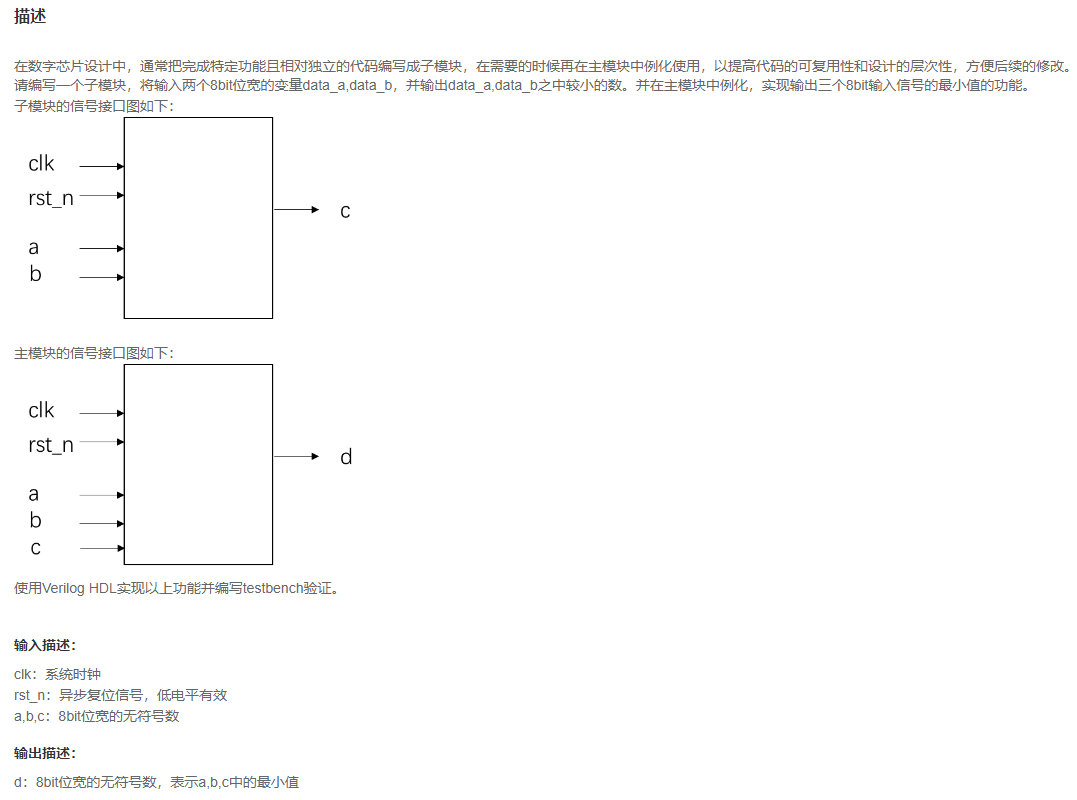

module main_mod( input clk, input rst_n, input [7:0]a, input [7:0]b, input [7:0]c,

output [7:0]d );

wire [7:0] tmp1; child_mod U0( .clk (clk), .rst_n (rst_n), .a (a), .b (b), .c (tmp1) );

wire [7:0] tmp2; child_mod U1( .clk (clk), .rst_n (rst_n), .a (a), .b (c), .c (tmp2) );

child_mod U3( .clk (clk), .rst_n (rst_n), .a (tmp1), .b (tmp2), .c (d) );

endmodule

module child_mod( input clk, input rst_n, input [7:0]a, input [7:0]b,

output [7:0]c );

reg [7:0] c_reg; always @(posedge clk or negedge rst_n) begin if(!rst_n) begin c_reg <= 8’b0; end else begin if(a < b) begin c_reg <= a; end else begin c_reg <= b; end end end assign c = c_reg;

endmodule

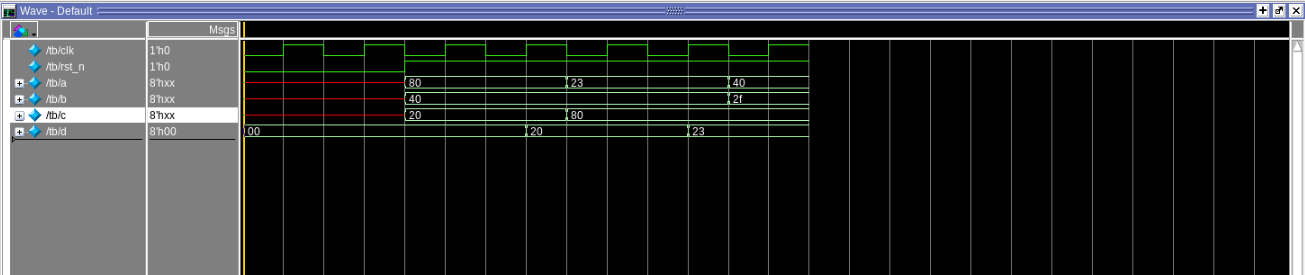

:::info【注】1. 父类模块中例化子类模块的方法:模块名称child_mod 例化后的新名称U0(<br />.clk原模块引脚名 (现在传入引脚的名字) 以此完成映射关系<br />);2. 映射的时候,原模块的引脚名和在现模块中的变量必须是同一类型。都是wire类型才能够完成映射。:::<a name="AfdGq"></a># 1.9.2 Testbench验证```verilog`timescale 1ns/1nsmodule tb;bit clk;bit rst_n;reg [7:0] a;reg [7:0] b;reg [7:0] c;reg [7:0] d;main_mod U0(.clk (clk),.rst_n (rst_n),.a (a),.b (b),.c (c),.d (d));initial begin : gen_clk;forever #5 clk <= !clk;endinitial beginclk = 0;rst_n = 0;d = 8'b0;#20;rst_n = 1;a = 8'b1000_0000;b = 8'b0100_0000;c = 8'b0010_0000;#20;a = 8'b0010_0110;b = 8'b0100_0000;c = 8'b1100_0000;#20;a = 8'b0100_0000;b = 8'b0010_1111;c = 8'b1000_0000;#10;$finish();endendmodule

:::info tb验证过程中遇到的问题:

- 波形采样不到输出信号,debug发现是rst信号拉低以后没有拉高;

- initial过程块中需要给定输出、时钟信号、复位信号的初始状态。

:::