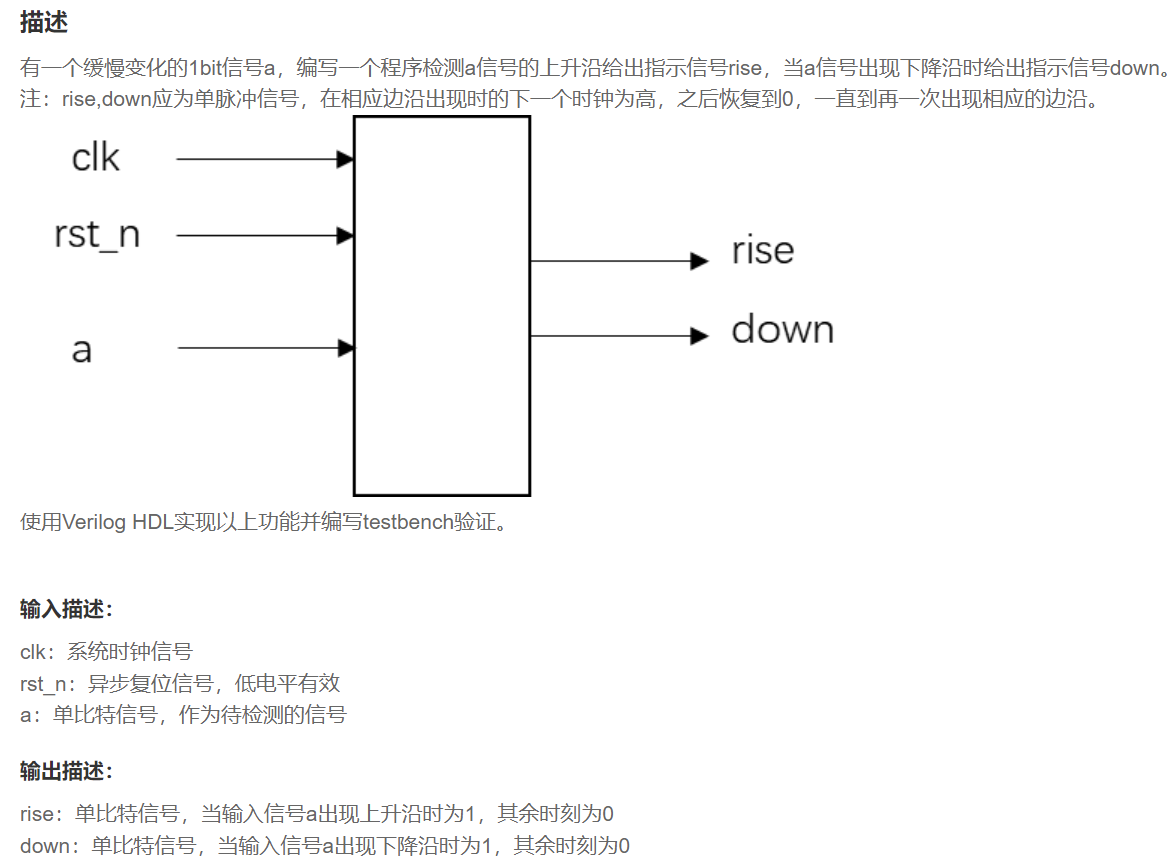

`timescale 1ns/1nsmodule edge_detect(input clk,input rst_n,input a,output reg rise,output reg down);reg a_r1;always @(posedge clk or negedge rst_n) beginif(!rst_n) beginrise <= 1'b0;down <= 1'b0;endelse begina_r1 <= a;if(!a_r1 & a) beginrise <= 1'b1;endelse if(a_r1 & !a) begindown <= 1'b1;endelse beginrise <= 1'b0;down <= 1'b0;endendendendmodule