:::danger 【知识点】

- 注意有符号数的写法:在声明之前需要添加signed;

- 有符号数在运算的时候可以使用连接运算符将符号位连接上去再运算;

- 有符号数和有符号数的运算结果仍然是有符号数。

:::

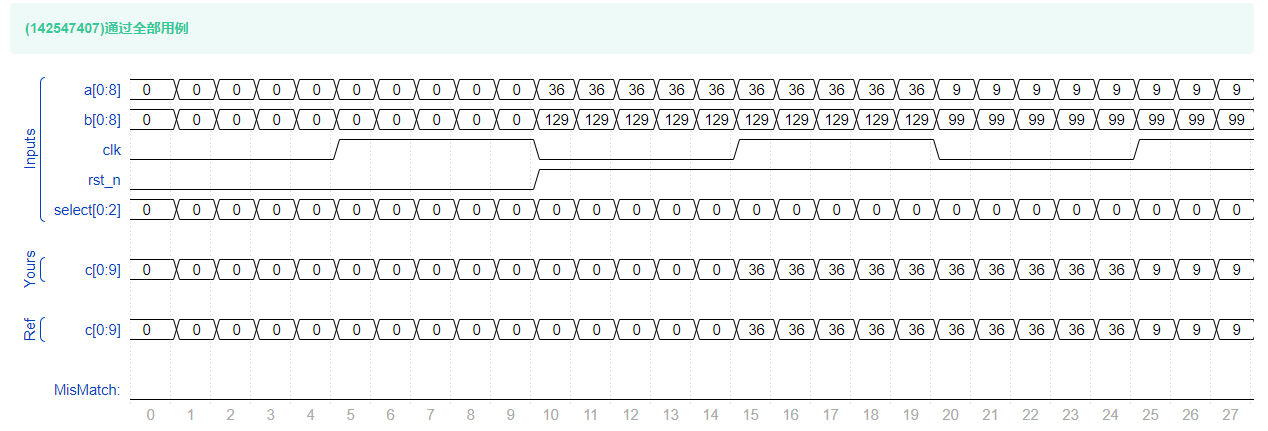

``verilogtimescale 1ns/1ns module data_select( input clk, input rst_n, input signed [7:0] a, input signed [7:0] b, input [1:0]select, output reg signed [8:0] c ); //*code**// always @(posedge clk or negedge rst_n) begin if(!rst_n) begin c <= 9’b0; end else begin case(select)

endcase end end //*code**// endmodule2'b00 : c <= a;2'b01 : c <= b;2'b10 : c <= a + b;2'b11 : c <= a - b;default : c <= 0;

// Method2 `timescale 1ns/1ns module data_select( input clk, input rst_n, input signed [7:0] a, input signed [7:0] b, input [1:0]select, output reg signed [8:0] c ); //*code**// always @(posedge clk or negedge rst_n) begin if(!rst_n) begin c <= 9’b0; end else begin case(select) 2’b00 : c <= a; 2’b01 : c <= b; 2’b10 : c <= {a[7],a} + {b[7],b}; 2’b11 : c <= {a[7],a} - {b[7],b}; default : c <= 0; endcase end end //*code**// endmodule

```