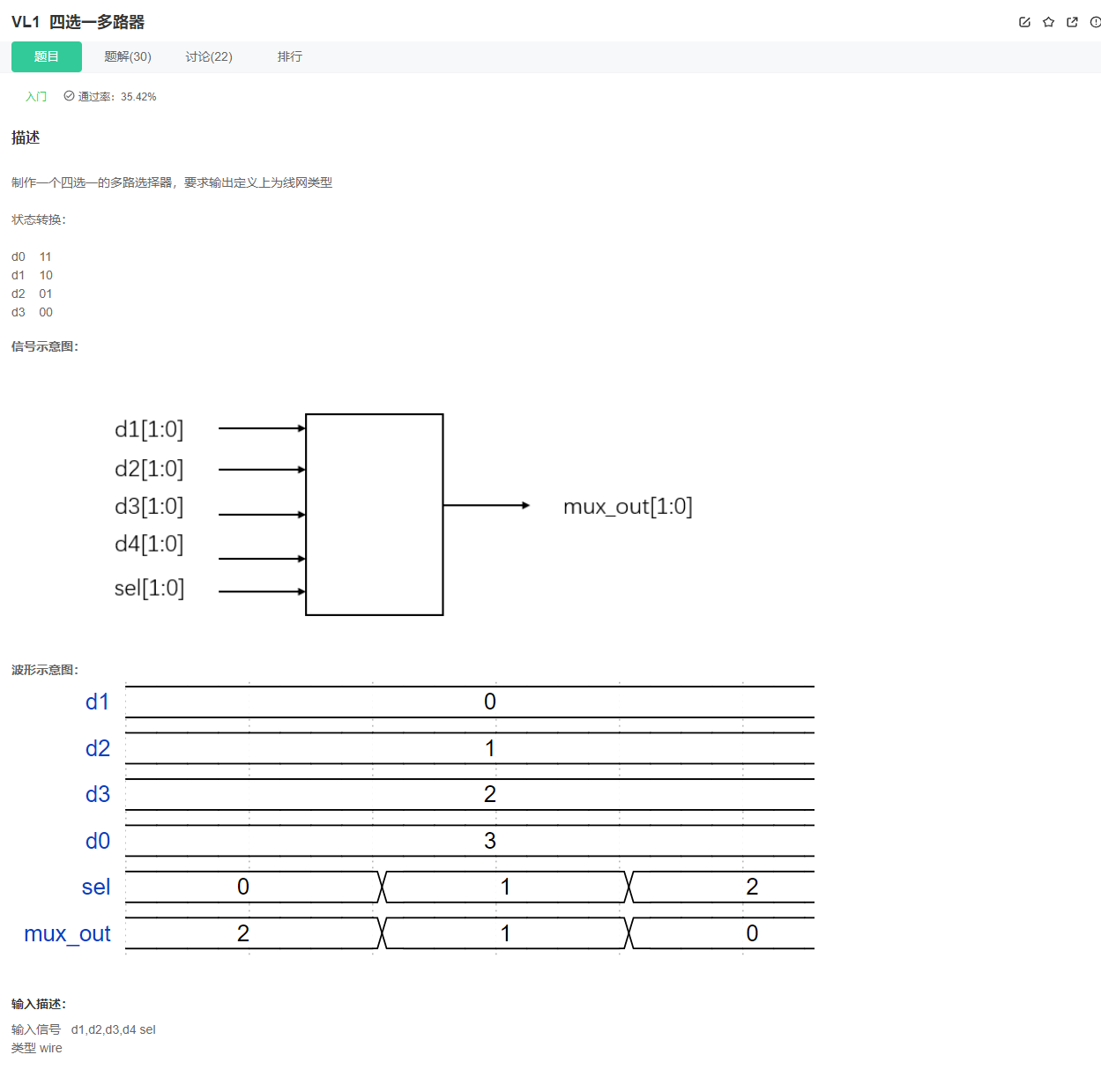

`timescale 1ns/1nsmodule mux4_1(input [1:0]d1,d2,d3,d0,input [1:0]sel,output[1:0]mux_out);//*************code***********//reg [1:0] mux_out_reg;//always@(sel, d0, d1, d2, d3) beginalways@(*) begincase(sel)2'b00 : mux_out_reg = d3;2'b01 : mux_out_reg = d2;2'b10 : mux_out_reg = d1;default : mux_out_reg = d0;endcaseendassign mux_out = mux_out_reg;//*************code***********//endmodule

【注】

- case语句必须always块中,由于没有时钟,所以always块中的敏感变量就是*,也就是说always块中的所有变量都会触发always块的执行;

- begin…end中被赋值的变量必须使用reg类型;

- 使用三木运算符就不需要用到begin…end,因而也不需要声明reg类型的中间变量,直接使用assign赋值即可

`timescale 1ns/1nsmodule mux4_1(input [1:0]d1,d2,d3,d0,input [1:0]sel,output[1:0]mux_out);//*************code***********//reg [1:0] mux_out_reg;always@(*) beginif(sel == 2'b00)mux_out_reg = d3;else if(sel == 2'b01)mux_out_reg = d2;else if(sel == 2'b10)mux_out_reg = d1;else if(sel == 2'b11)mux_out_reg = d0;endassign mux_out = mux_out_reg;//*************code***********//endmodule

`timescale 1ns/1nsmodule mux4_1(input [1:0]d1,d2,d3,d0,input [1:0]sel,output[1:0]mux_out);//*************code***********//assign mux_out = (sel == 2'b00)?d3:(sel == 2'b01)?d2:(sel == 2'b10)?d1:d0;//*************code***********//endmodule