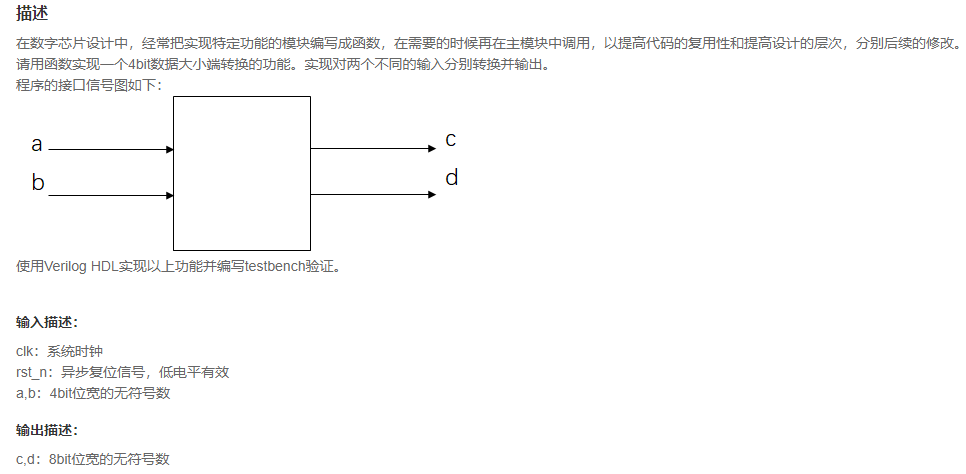

输入数据的大小端转换也就是输入数据的高低位转换

`timescale 1ns/1nsmodule function_mod(input clk,input rst_n,input [3:0] a,input [3:0] b,output [3:0] c,output [3:0] d);assign c = convert(a);assign d = convert(b);reg [3:0] c_reg;reg [3:0] d_reg;always @(negedge clk or negedge rst_n) beginif(!rst_n) beginc_reg <= 0;d_reg <= 0;endelse beginc_reg <= convert(a);d_reg <= convert(b);endendassign c = c_reg;assign d = d_reg;//-- function [3:0] convert;//-- input [3:0] data;//-- begin//-- genvar i;//-- generate//-- for(i = 0; i < 4; i = i+1)//-- begin : gen_i//-- assign convert[i] = data[3-i];//-- end//-- endgenerate//-- end//-- endfunctionfunction [3:0] convert;input [3:0] data;beginconvert[0] = data[3];convert[1] = data[2];convert[2] = data[1];convert[3] = data[0];endendfunctionendmodule

题目中没有提到是组合逻辑电路还是时序逻辑电路,所以两种实现方法都可以,需要注意的就是在使用时序逻辑电路的时候,在时钟信号的下降沿开始就有数据输出,所以敏感时间列表中的clk信号是下降沿触发。