学习目标

- 了解SPI协议

- 熟悉SPI相关的名词

- 熟悉SPI通讯过程

-

学习内容

SPI概念

SPI(Serial Peripheral Interface)是一种串行外设接口协议,用于在微控制器(MCU)或微处理器之间进行通信。SPI协议通常用于连接主设备(通常是微控制器)与外部从设备(如传感器、存储器芯片、显示器等)之间,以传输数据和控制信息。SPI通信具有以下主要特点:

串行通信: SPI使用多个引脚进行通信,包括时钟线(SCLK)、主输出从输入线(MOSI)、主输入从输出线(MISO)和片选线(CS/SS)。通信是串行的,每个数据位都按位传输。

- 全双工通信: SPI支持全双工通信,这意味着主设备可以同时发送数据到从设备并接收从设备返回的数据。这使得SPI非常适合需要高速双向通信的应用。

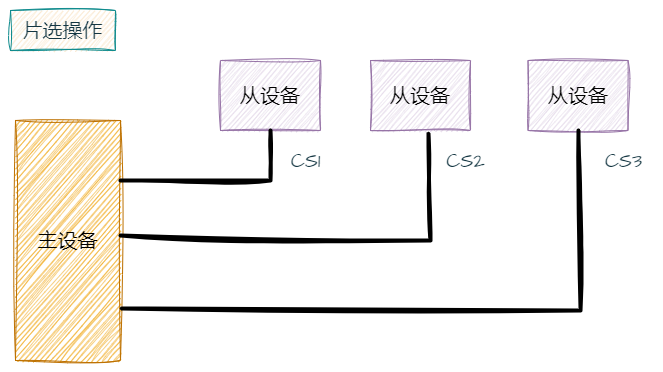

- 主从架构: SPI通信通常涉及一个主设备和一个或多个从设备。主设备控制通信流程,选择要与之通信的从设备,然后发送和接收数据。从设备按照主设备的命令响应。

- 时钟同步: SPI通信是时钟同步的,主设备生成时钟信号来同步数据的传输。时钟信号的极性(CPOL)和相位(CPHA)可以配置,以确定数据在时钟的上升沿或下降沿进行传输。

- 多工作模式: SPI支持多种工作模式,通常有四种模式,根据CPOL和CPHA的不同组合而变化。这些模式允许SPI适应不同的硬件配置和通信需求。

- 快速传输速度: SPI通信可以在高速应用中运行,具体速度取决于硬件和软件的支持,通常可以达到几兆赫兹或更高的速度。

SPI通信在嵌入式系统、传感器应用、存储器接口、显示屏控制和许多其他领域广泛使用。由于其高速、全双工和简单的硬件连接,SPI通信在许多嵌入式项目中都是一种常见的通信协议。不同的MCU和外部设备可能有不同的SPI实现细节,因此需要仔细查阅硬件文档以正确配置和使用SPI通信。

通讯方式

SPI可以称之为总线。总线是主设备和从设备间进行通讯的。

SPI通讯过程中包含了多条线:

- 时钟线(SCLK - Serial Clock):时钟线用于同步数据传输,它由主设备生成,控制数据的传输速率。所有SPI设备都共享同一个SCLK线。

- 主输出从输入线(MOSI - Master Out Slave In):MOSI线用于从主设备向从设备传输数据。主设备将要发送的数据通过这条线发送给从设备。

- 主输入从输出线(MISO - Master In Slave Out):MISO线用于从从设备向主设备传输数据。从设备将其响应的数据通过这条线发送给主设备。

- 片选线(CS/SS - Chip Select/Slave Select):片选线用于选择与主设备通信的特定从设备。当主设备希望与某个从设备通信时,它会使该从设备的片选线为低电平,以指示通信目标。当片选线为高电平时,从设备处于非活动状态。

这四条线是SPI通信中的基本线路,它们允许主设备与一个或多个从设备之间进行全双工通信。根据具体的SPI配置和需求,有时还可以使用其他辅助线,如主设备的输出使能线或从设备的中断线,以实现更复杂的通信和控制功能。

由于认知或者是其他原因,在业界,这四条线名字非常多,例如:

- SCLK (Serial Clock) - 时钟线:

- SCK (Serial Clock)

- CLK (Clock)

- SCL (Serial Clock Line)

- SCKL (Serial Clock Line)

- SCLCK (Serial Clock)CK (Clock)

- MOSI (Master Out Slave In) - 主输出从输入线:

- SDO (Serial Data Out)

- SIMO (Serial Input, Master Output)

- MOS (Master Out, Slave In)

- TXD (Transmit Data)

- DOUT (Data Out)

- MISO (Master In Slave Out) - 主输入从输出线:

- SDI (Serial Data In)

- SOMI (Serial Output, Master Input)

- MISO (Master In, Slave Out)

- RXD (Receive Data)

- DIN (Data In)

- CS/SS (Chip Select/Slave Select) - 片选线:

- CS (Chip Select)

- CE (Chip Enable)

- SS (Slave Select)

- SSEL (Slave Select)

- CSB (Chip Select, Active Low)

- nCS (Negative Chip Select)

- NSS(Negative Slave select)

这些别名可能会在不同的文档、数据手册和硬件设计中出现。要确保正确配置SPI通信,你需要查阅所使用的硬件平台或芯片的文档,以了解它们使用的确切名称。通常,这些别名在硬件文档中都有详细的说明,以帮助你正确地连接和配置SPI设备。

这个主设备是可以和多个从设备进行通讯,但是,只能有一个从设备在线。控制从设备在线的方式是,主设备为每一个从设备准备一条片选线,谁如果在线,他的片选线就拉低,其他的拉高。

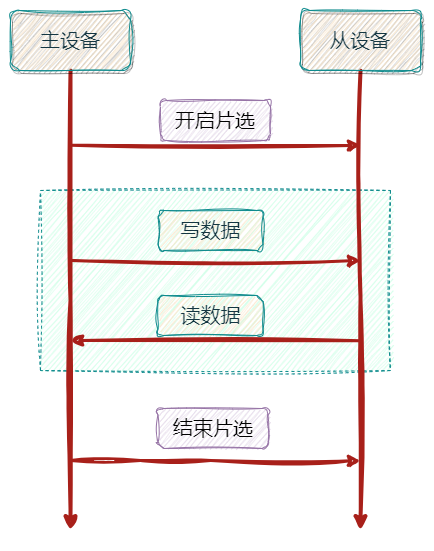

通讯流程

- 开启和结束片选,就是对片暄线进行高低电平输出。

- 读写数据,在片选完成后,可以无限制的读和写。

通讯规则

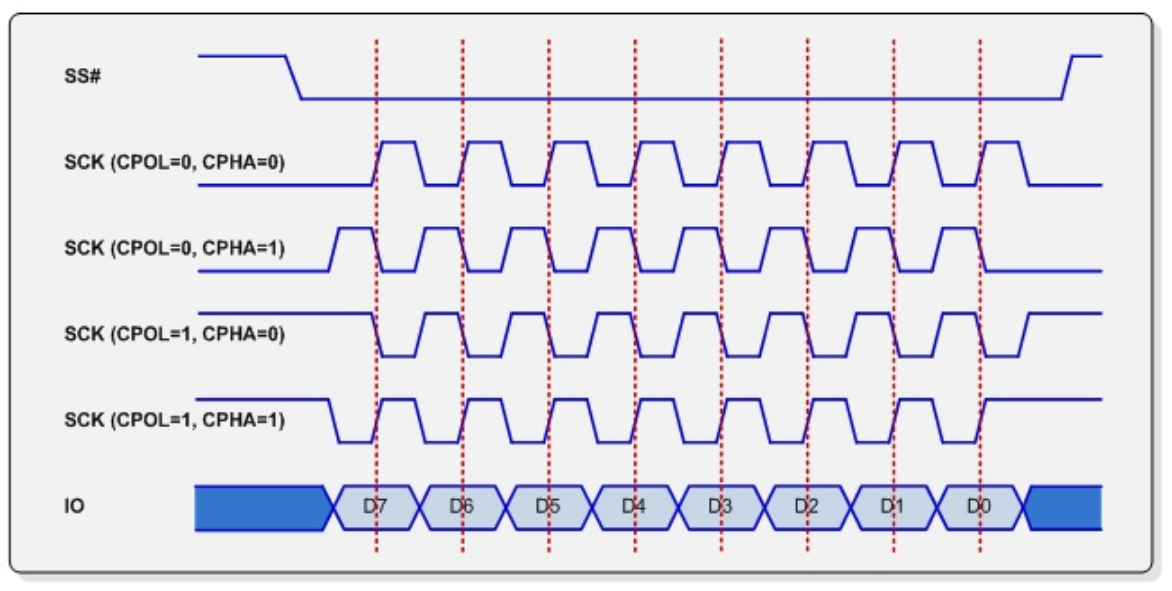

时钟极性CPOL

CPOL(Clock Polarity)是SPI(Serial Peripheral Interface)通信协议的一个重要参数,它用于确定时钟信号(CLK)在空闲状态时的电平以及数据的改变和采样时机

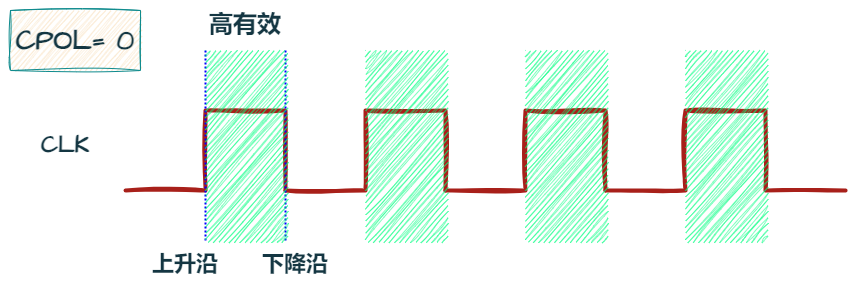

CPOL = 0(时钟极性为0)

在这种模式下,时钟信号在空闲状态时保持低电平(0)。激活状态时保持高电平(1)

数据改变发生在CLK的上升沿之后发生。具体来说,当CLK从低电平(0)变为高电平(1)后,数据被改变或采样。

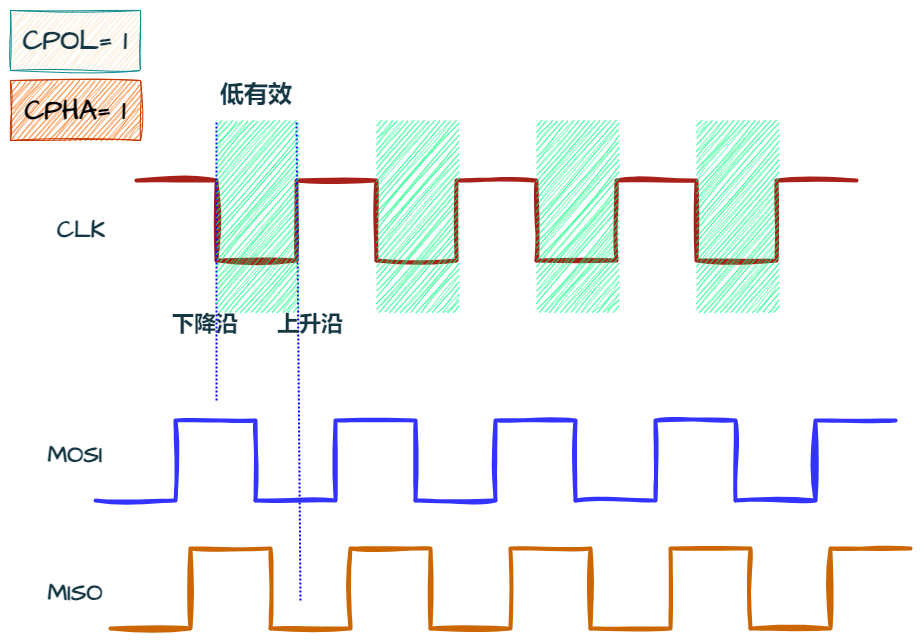

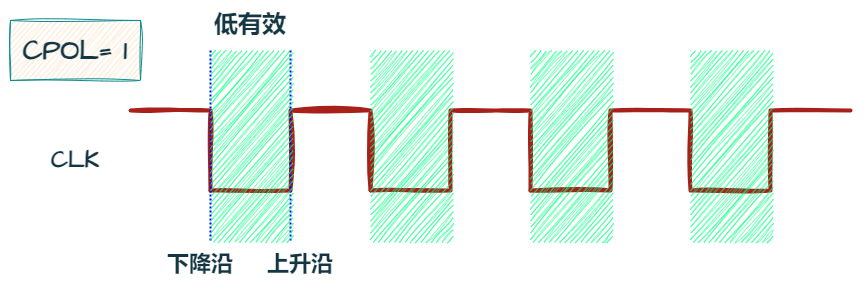

CPOL = 1(时钟极性为1)

在这种模式下,时钟信号在空闲状态时保持高电平(1)。激活状态时保持低电平(0)

数据传输发生在SCLK的下降沿之后发生。具体来说,当SCLK从高电平(1)变为低电平(0)后,数据被改变或采样。

相位CPHA

CPHA(Clock Phase)是SPI(Serial Peripheral Interface)通信协议的另一个关键参数,它用于确定数据何时传输和采样相对于时钟信号(SCLK)的相位。CPHA有两种可能的取值:0和1。

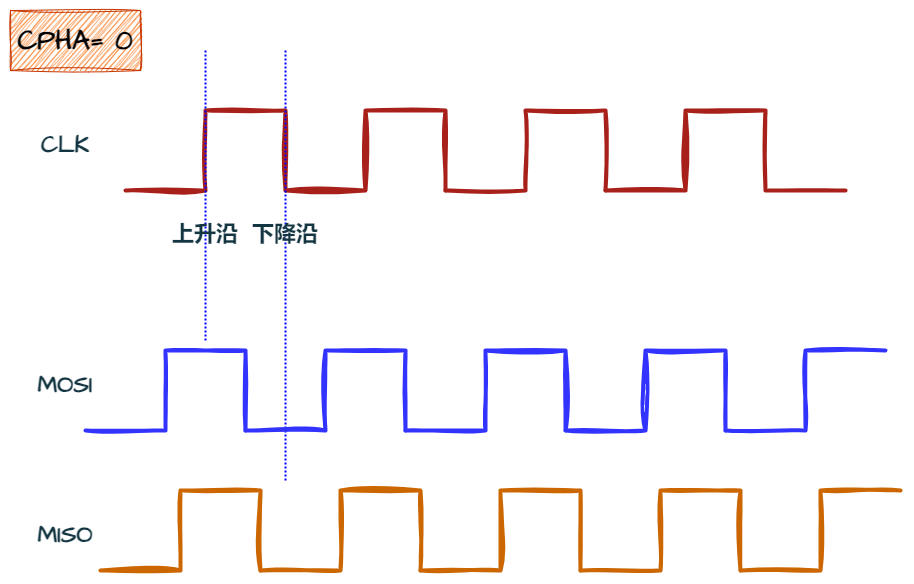

CPHA = 0(时钟相位为0)

在这种模式下,在时钟信号第一个边沿采样数据,在第二个边沿改变数据(上升沿或下降沿取决于CPOL)

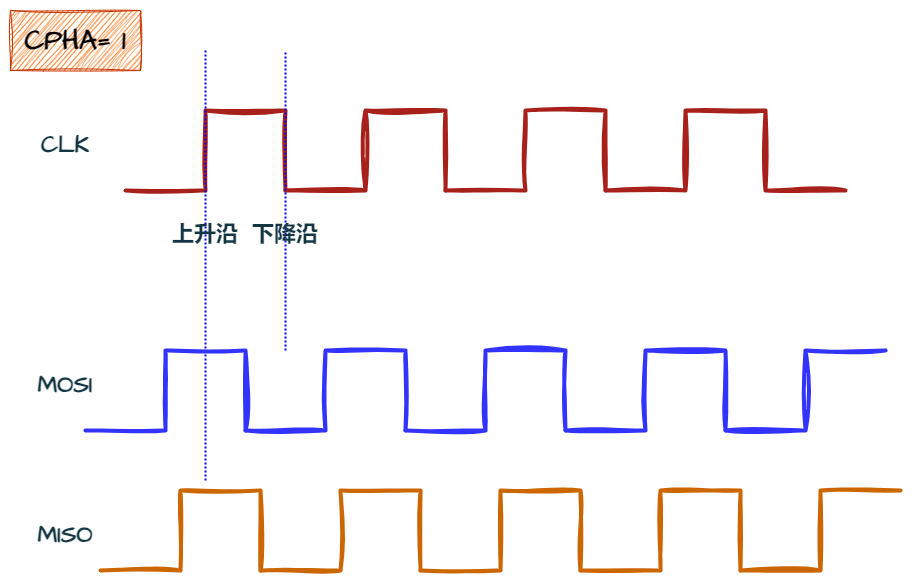

CPHA = 1(时钟相位为1)

在这种模式下,在时钟信号第一个边沿改变数据,在第二个边沿采样数据(上升沿或下降沿取决于CPOL)

传输与采样模式

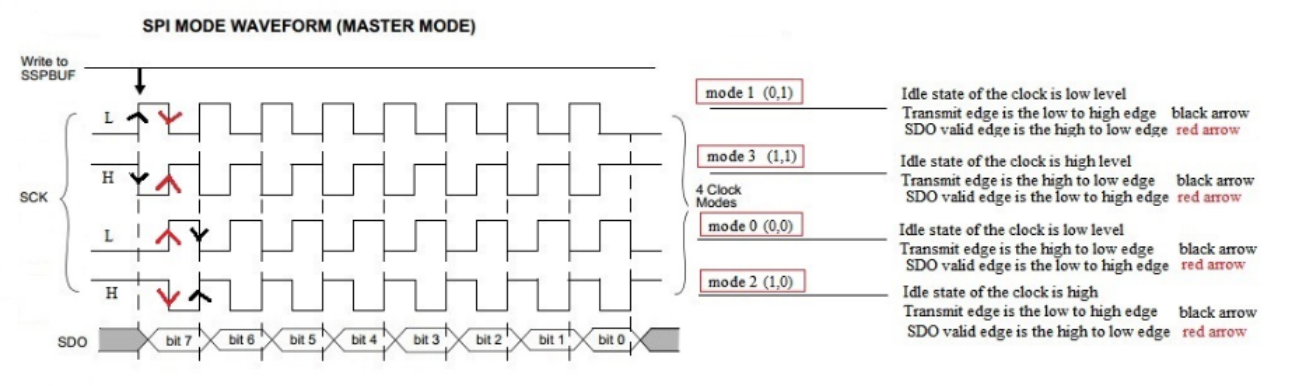

由时钟极性和相位两两搭配,可以组成4种模式,主要表达的是何时进行传输,何时进行采样。

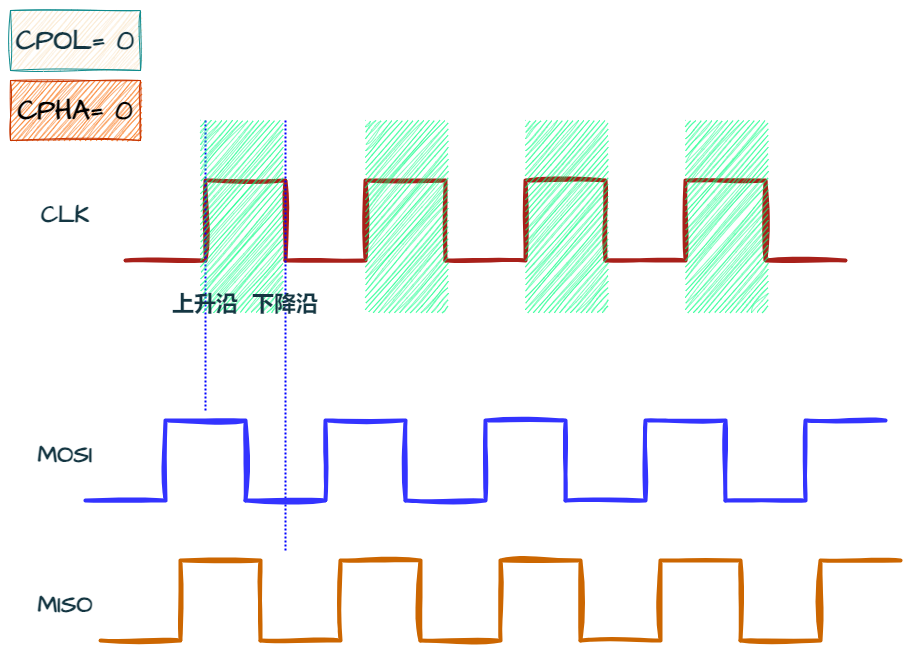

SPI模式0(CPOL = 0, CPHA = 0)

- SCLK在空闲状态为低电平。

- 数据在SCLK的上升沿传输,然后在下降沿采样。

- 这是最常见的SPI模式,通常用于许多SPI设备。

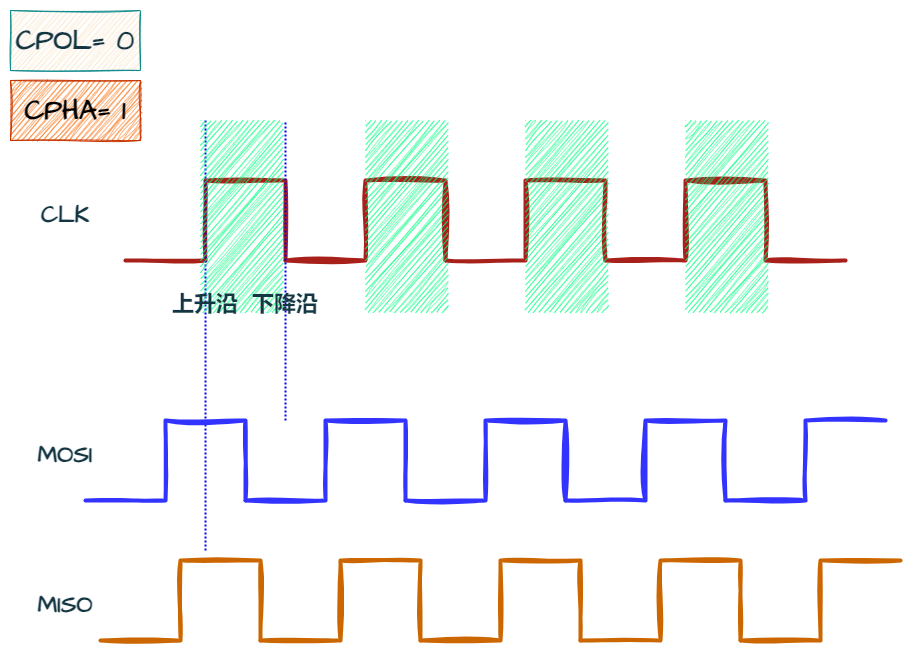

SPI模式1(CPOL = 0, CPHA = 1)

- SCLK在空闲状态为低电平。

- 数据在SCLK的下降沿传输,然后在上升沿采样。

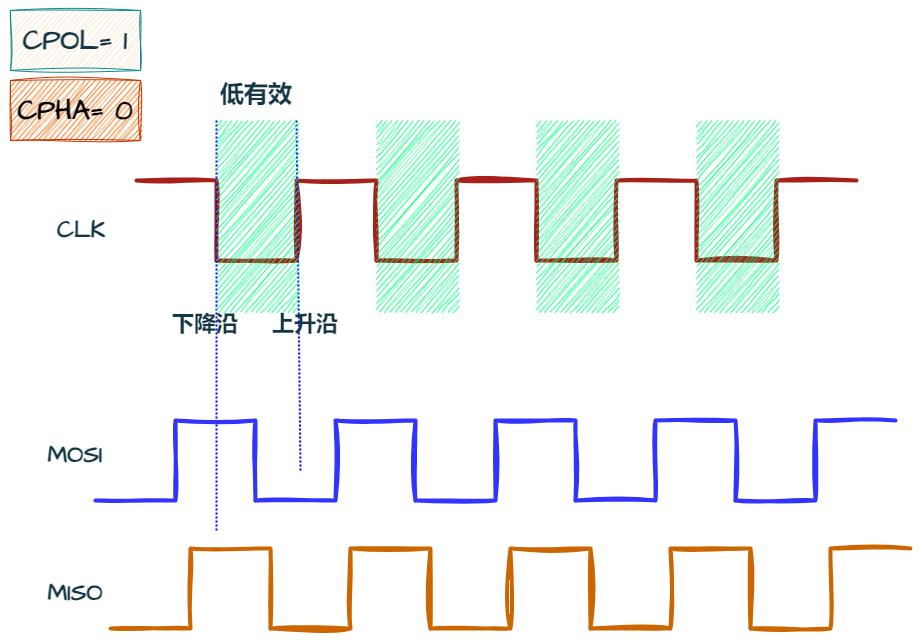

SPI模式2(CPOL = 1, CPHA = 0)

- SCLK在空闲状态为高电平。

- 数据在SCLK的上升沿传输,然后在下降沿采样。

SPI模式3(CPOL = 1, CPHA = 1)

- SCLK在空闲状态为高电平。

- 数据在SCLK的下降沿传输,然后在上升沿采样。

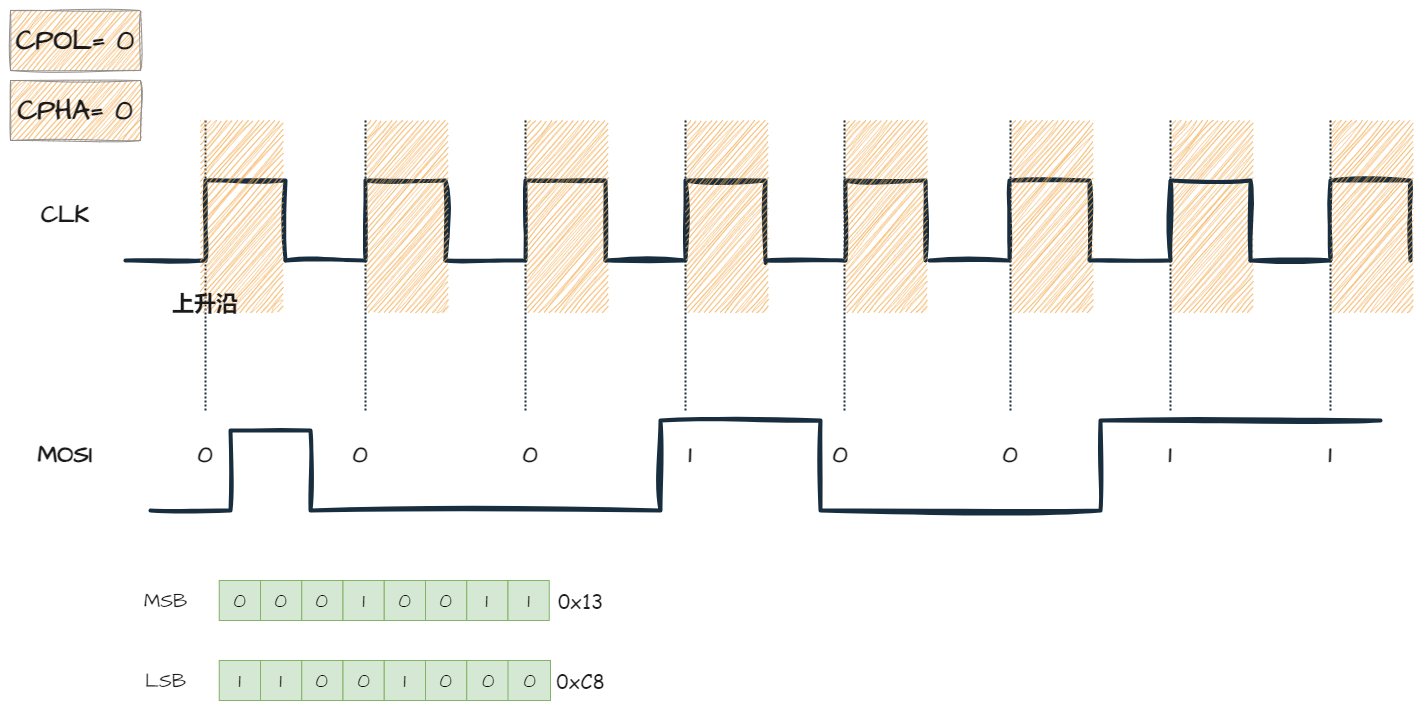

大小端

在SPI(Serial Peripheral Interface)通信中,MSB(Most Significant Bit)和LSB(Least Significant Bit)是指数据字节的高位(最高有效位)和低位(最低有效位)。它们用于描述数据位的传输顺序,即哪个数据位首先被发送或接收。

- MSB First: 在这种模式下,SPI通信从数据字节的最高有效位(MSB)开始传输,依次传输到最低有效位(LSB)。这是SPI通信的默认模式,也是最常见的模式。大多数SPI设备都使用此模式。

- LSB First: 在这种模式下,SPI通信从数据字节的最低有效位(LSB)开始传输,依次传输到最高有效位(MSB)。这种模式较少见,通常在特定应用或特定SPI设备中使用。

通常,SPI设备的数据手册或规格书会明确指定它们使用的位传输顺序,以便正确配置主设备(通常是微控制器或微处理器)的SPI控制器。确保主设备的位传输顺序与所连接的SPI设备的要求相匹配非常重要,否则通信可能会导致错误或数据丢失。大多数SPI控制器都允许配置MSB或LSB传输顺序以适应不同的设备需求。