https://www.bilibili.com/video/BV1bs411c71N?p=2&share_source=copy_web

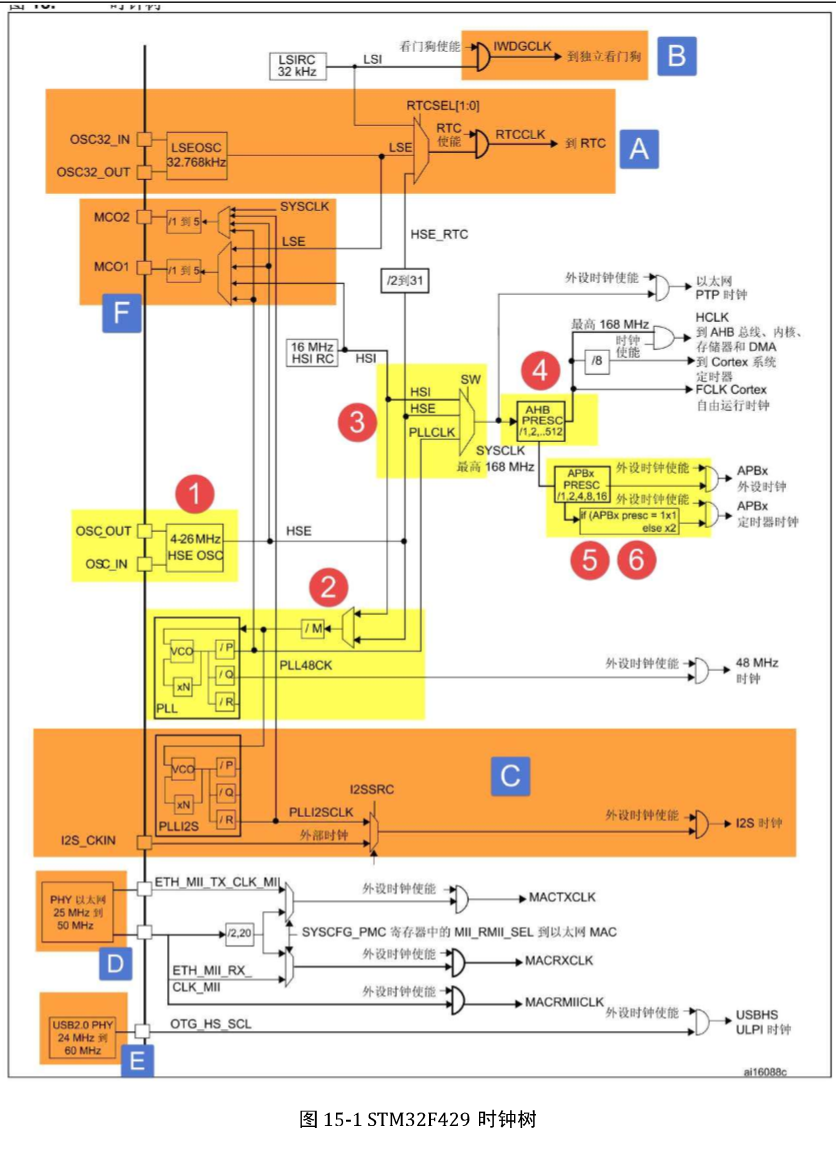

时钟树主系统时钟

HSE 外部时钟

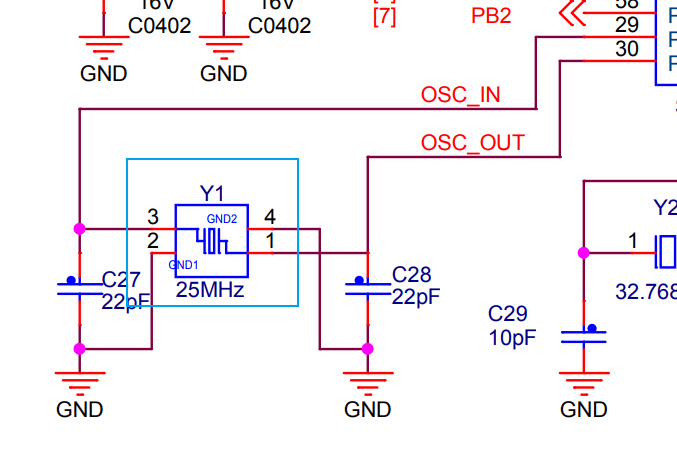

HSE:High Speed External Clock signal,即高速的外部时钟,可以由有源晶振(1-50M)或者无源晶振(4-26M)提供。

当使用有源晶振时,时钟从OSC_IN 引脚进入,OSC_OUT 引脚悬空,当选用无源晶振时,时钟从OSC_IN 和 OSC_OUT 进入,并且要配谐振电容。

控制:RCC_CR 时钟控制寄存器的位16:HSEON控制

HSI:High Speed Internal Clock signal,即高速的内部时钟。

来源:芯片内部,大小为16M,当HSE故障时,系统时钟会自动切换到HSI,直到HSE启动成功。

控制: RCC_CR 时钟控制寄存器的位0:HSION控制

V2开发板使用 25M 的无源晶振。如果我们使用HSE 或者HSE 经过PLL 倍频之后的时钟作为系统时钟SYSCLK, 当HSE 故障时候,不仅HSE 会被关闭,PLL 也会被关闭,此时高速的内部时钟时钟信号 HSI 会作为备用的系统时钟,直到HSE 恢复正常,HSI=16M。

PLL锁相环时钟

锁相环时钟:PLLCLK

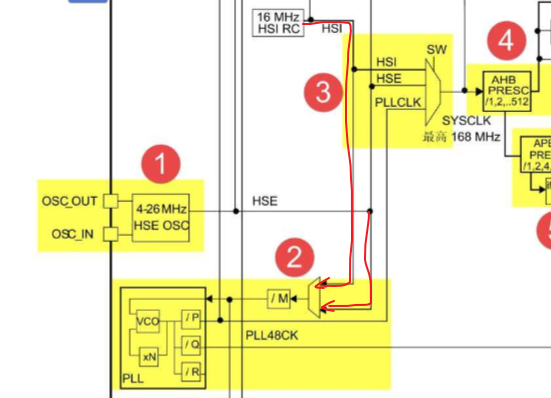

来源:HSI、HSE,由PLLSRC位配置。

HSE或者HSI先经过一个分频因子M进行分频,然后再经过一个倍频因子N,然后再经过一个分频因子P,最后成为锁相环时钟

PLLCLK = (HSE/M) N / P = 25/25 360 / 2 = 180M

控制: RCC_PLLCFGR :RCC PLL 配置寄存器