Verilog HDL学习

Verilog HDL和VHDL的比较

硬件描述语言(Hardware Description Language,HDL)通过描述硬件的实现方法,来产生与之对应的真实的硬件电路,最终实现所设计的预期功能。设计方式与软件不同,因此也就意味着其描述的各个功能之间,可以像硬件一样实现真正的并行执行,这也是硬件描述语言和软件的不同。之所以不直接叫硬件语言却叫硬件描述语言的原因是:这是通过一种语言来“描述”我们设计的硬件所要实现的功能,而不是直接对硬件进行设计。硬件描述语言描述完设计的功能后,还需要通过“综合”这一过程才能最终生成所设计功能的硬件电路。

Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

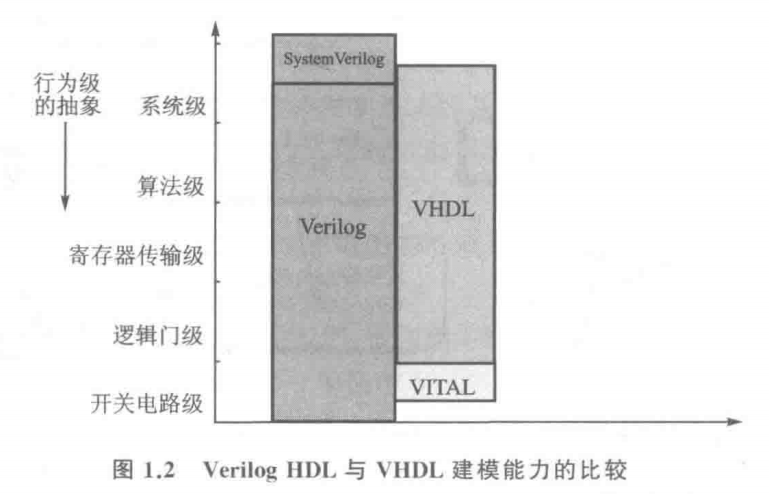

目前常用的硬件描述语言主要有两种,一种是Verilog HDL(以下简称Verilog),另一种是 VHDL。VHDL 其英文全名为VHSIC Hardware Description Language,而VHSIC则是Very High Speed Integerated Circuit的缩写词,意为甚高速集成电路,故VHDL其准确的中文译名为甚高速集成电路的硬件描述语言。

Verilog模型可以是实际电路的不同级别的抽象。这些抽象的级别和它们对应的模型类型共有以下五种:

- 系统级(system):用高级语言结构实现设计模块的外部性能的模型。

- 算法级(algorithm):用高级语言结构实现设计算法的模型。

- RTL级(Register Transfer Level):描述数据在寄存器之间流动和如何处理这些数据的模型。

- 门级(gate-level):描述逻辑门以及逻辑门之间的连接的模型。

- 开关级(switch-level):描述器件中三极管和储存节点以及它们之间连接的模型。

目前常用的硬件描述语言主要有两种,一种是Verilog HDL(以下简称Verilog),另一种是 VHDL。VHDL 其英文全名为 VHSIC Hardware Description Language,而 VHSIC 则是 Very High Speed Integerated Circuit的缩写词,意为甚高速集成电路,故VHDL其准确的中文译名为甚高速集成电路的硬件描述语言。

| 共同点 | 不同点 |

|---|---|

- 能形式化地抽象表示电路的行为和结构; - 支持逻辑设计中层次与范围的描述; - 可借用高级语言的精巧结构来简化电路行为的描述; - 具有电路仿真与验证机制以保证设计的正确性; - 支持电路描述由高层到低层的综合转换; - 硬件描述与实现工艺无关(有关工艺参数可通过语言提供的属性包括进去); - 便于文档管理;易于理解和设计重用。 |

- Verilog HDL拥有更广泛的设计群体,成熟的资源也远比VHDL丰富。 - VHDL 与 Verilog 相比,有以下优势:语法比 Verilog 严谨,通过 EDA 工具自动语法检查,易排除许多设计中的疏忽。有很好的行为级描述能力和一定的系统级描述能力,而 Verilog 建模时,行为与系统级抽象及相关描述能力不及 VHDL。 - VHDL 与 Verilog 相比,有以下不足之处:VHDL 代码较冗长,在相同逻辑功能描述时,Verilog 的代码比 VHDL 少许多。VHDL 对数据类型匹配要求过于严格,初学时会感到不是很方便,编程耗时也较多;而 Verilog 支持自动类型转换,初学者容易入门。VHDL 对版图级、管子级这些较为底层的描述级别几乎不支持,无法直接作集成电路底层建模。 |

Verilog HDL和C语言的比较

Verilog 在很多语法上都和 C 语言极其相似,甚至有些语法是通用的,这也是 Verilog 语言容易上手的一个很重要的原因。Verilog 语言本身就是从 C 语言继承并发展而来的,但是它主要用于描述硬件,和 C 语言这种软件语言思想完全不同。C语言所描述的代码功能在执行时都是一行一行顺序执行的,而 Verilog 语言在设计完成后执行时则是并行执行的,C语言所描述的代码功能并 不会真实的映射成最后的硬件,只是对内存的操作和进行数据的搬移 ,而用Verilog语言所描述的代码功能则会真真正正的生成所对应的硬件电路 , 所以这也是 Verilog 语言被称为“硬件描述语言”的原因。

Verilog HDL基础语法

所有的Verilog代码都以module(模块)的方式存在,一个简单的逻辑可以由一个module组成,复杂的逻辑可以包含多个modules,每个module有独立的功能,并可通过输入、输出端口被其它module调用(实例化)。通过module的方式可以将一些比较独立、可以复用的功能进行模块化,代码阅读起来也比较直观。

Verilog语法是有很多的,而且分为可综合(综合后可以生成对应的硬件电路)的语法和不可综合(综合后不可以生成对应的硬件电路)的语法,可综合的代码是非常少的,大多数的代码是不可综合的。

标识符

标识符用于定义常数、变量、信号、端口、子模块或参数名称。Verilog语言是区分大小写的。标识符可以是字母、数字、$(美元符号)和下划线的任意组合,只要第一个字符是字母或者下划线即可。

逻辑值

常量

变量

Verilog 语言中主要的两种变量类型:

- 线网型:表示电路间的物理连接;

- 寄存器型:Verilog 中一个抽象的数据存储单元。

线网型和寄存器类型具体又包含很多种变量,线网型变量最常用的变量就是wire,而寄存器型最常用的变量是reg。wire 可以看成直接的连接,在可综合的逻辑中会被映射成一根真实的物理连线;而 reg 具有对某一个时间点状态进行保持的功能,如果在可综合的时序逻辑中表达,会被映射成一个真实的的物理寄存器,而在 Verilog 仿真器中,寄存器类型 的变量通常要占据一个仿真内存空间。

因此在设计逻辑的时候要明确定义每个信号是 wire 还是 reg 属性。凡是在 always 或 initial 语句中被赋值的变量(赋值号左边的变量),不论表达的是组合逻辑还是时序逻辑, 都一定是 reg 型变量;凡是在 assign 语句中被赋值的变量,一定是 wire 型变量。

参数

参数是一种常量,通常出现在module 内部,常被用于定义状态机的状态、数据位宽和计数器计数个数大小等

赋值语句

赋值语句的赋值方式有两种,分别为“<=”(非阻塞赋值)和“=”(阻塞赋值)。

以 赋 值 操 作 符 “ <=” 来 标 识 的 赋 值 操 作 称 为 “ 非 阻 塞 型 过 程 赋 值 ( Nonblocking Assignment)”。非阻塞型过程赋值语句的特点如下:

- 在 begin-end 串行语句块中,一条非阻塞过程语句的执行不会阻塞下一语句的执行,也 就是说在本条非阻塞型过程赋值语句对应的赋值操作执行完之前,下一条语句也可以开始执行;

- 仿真过程在遇到非阻塞型过程赋值语句后首先计算其右端赋值表达式的值,然后等到 仿真时间结束时再将该计算结果赋值变量。也就是说,这种情况下的赋值操作是在同一仿真时刻上的其他普通操作结束后才得以执行。

以 赋 值 操 作 符 “ = ” 来 标 识 的 赋 值 操 作 称 为 “ 阻 塞 型 过 程 赋 值 (Blocking Assignment)”。阻塞型过程赋值语句的特点如下:

- 在begin-end 串行语句块中的各条阻塞型过程赋值语句将以它们在顺序块后排列次序依次得到执行;

- 阻塞型过程赋值语句的执行过程是:首先计算右端赋值表达式的值,然后立即将计算 结果赋值给“=”左端的被赋值变量。

阻塞型过程赋值语句的这两个特点表明:仿真进程在遇到阻塞型过程赋值语句时将计算表达式的值并立即将其结果赋给等式左边的被赋值变量;在串行语句块中,下一条语句的执行会被本条阻塞型过程赋值语句所阻塞,只有在当前这条阻塞型过程赋值语句所对应的赋值操作执行完后下一条语句才能开始执行。