IIC总线概述

lIC 总线 (Inter IC Bus) 由PHILIPS 公司推出,是近年来微电子通信控制领域广泛采用的种新型总线标准,它是同步通信的一种特殊形式,具有接口线少、控制简单、器件封装形式小、通信速率较高等优点。在主从通信中,可以有多个 l2C 总线器件同时接到 l2C 总线上,所有与 l2C 兼容的器件都具有标准的接口,通过地址来识别通信对象,使它们可以经由 l2C总线互相直接通信。

l2C 总线由数据线 SDA 和时钟线 SCL 两条线构成通信线路,既可发送数据,也可接收数据。在CPU 与被控 IC 之间、 IC与IC 之间都可进行双向传送,最高传送速率为 400kbps,各种被控器件均并联在总线上,但每个器件都有唯一的地址。在信息传输过程中, l2C 总线上并联的每一个器件既是被控器(或主控器),又是发送器(或接收器),这取决于它所要完成的功能。CPU 发出的控制信号分为地址码和数据码两部分:地址码用来选址,即接通需要控制的电路;数据码是通信的内容。

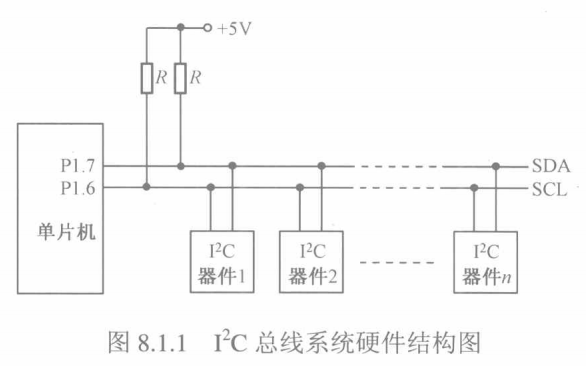

IIC总线硬件结构

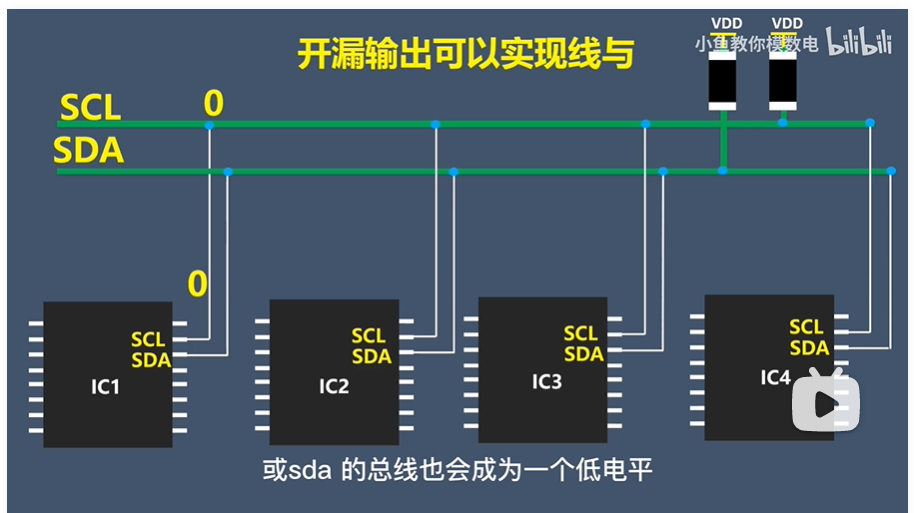

SCL 是时钟信号,从主设备发出。SDA 是数据信号,是一个双向的。总线在空闲状态下均保持高电平,连到总线上的任一器件输出的低电平,都将使总线的信号变低,即各器件SDA 和 SCL 都是线“与”关系。

IIC信号为什么要加上拉电阻

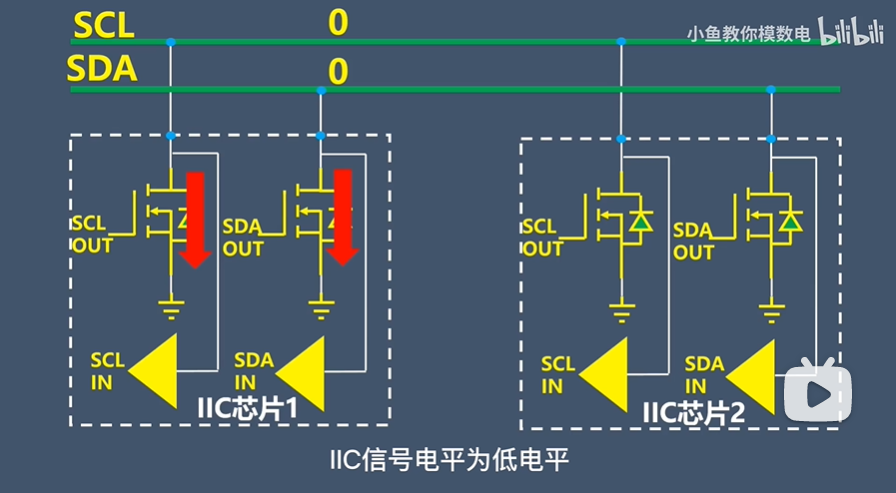

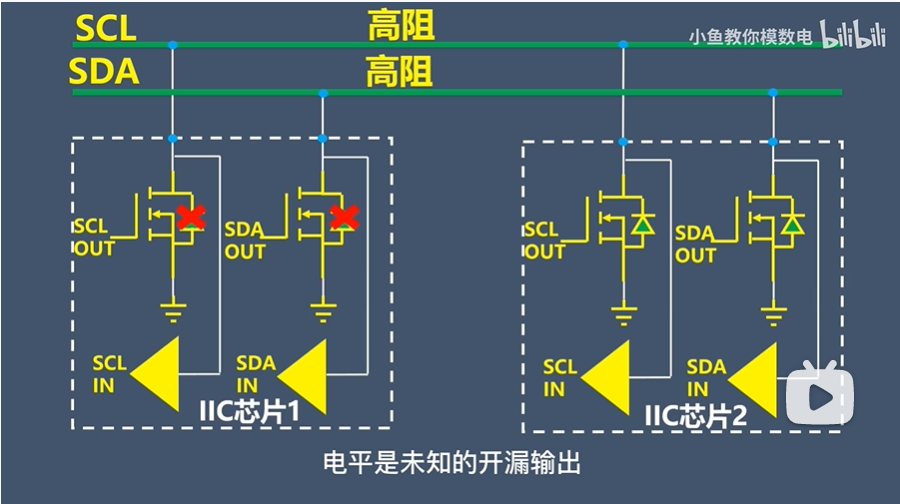

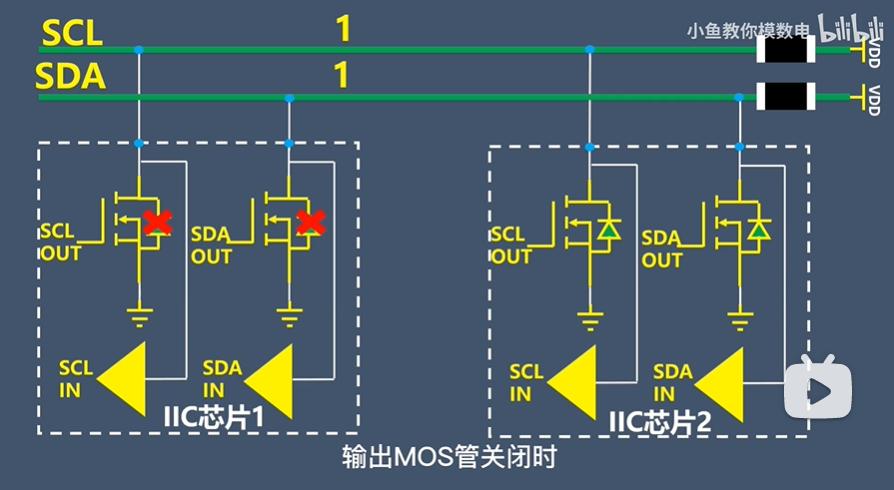

SCL 和 SDA 信号线均需接上拉电阻,主要原因就是SCL和SDA引脚是开漏输出的,就是只有一个NMOS管,不像推挽输出有两个MOS管。

当芯片的 SDA 和 SCL 引脚输出MOS管导通,IIC信号电平为低电平:

当芯片的 SDA 和 SCL 引脚输出MOS管关闭,如果没有上拉电阻,IIC信号线处于一个高阻状态,电平是未知的:

开漏输出是没有高电平的输出能力的,所以加上上拉电阻以后,输出MOS管关闭时,IIC信号线上的电平就是一个确切的高电平:

当多个IIC设备通过IIC总线连接在一起,这就要求IIC设备间是可以实现线与的。而芯片的IIC引脚是开漏输出的话,就能很好的实现线与。只要有一个IIC设备的引脚是低电平,对应的SCL或SDA总线也会成为低电平。

IIC上拉电阻阻值

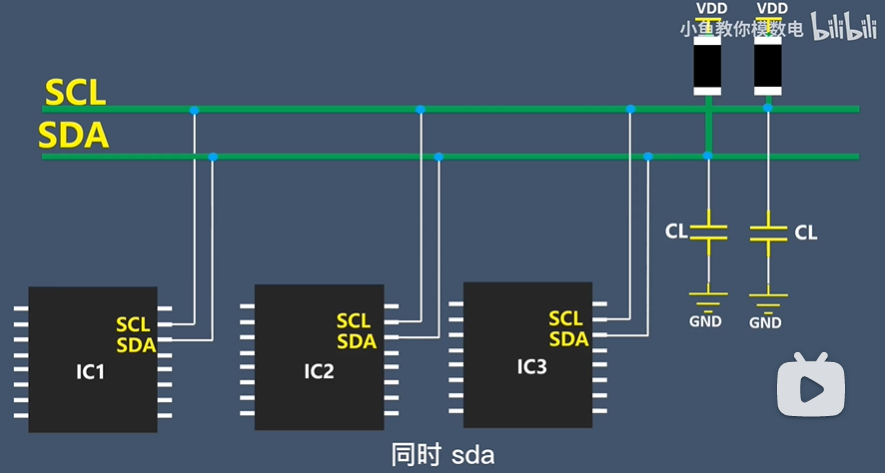

IIC信号的上拉电阻阻值不能太大,SCL和SDA引脚都存在寄生电容

同时SDA和SCL信号的走线也会存在寄生电容,整个IIC总线相当于接了一个负载电容CL。

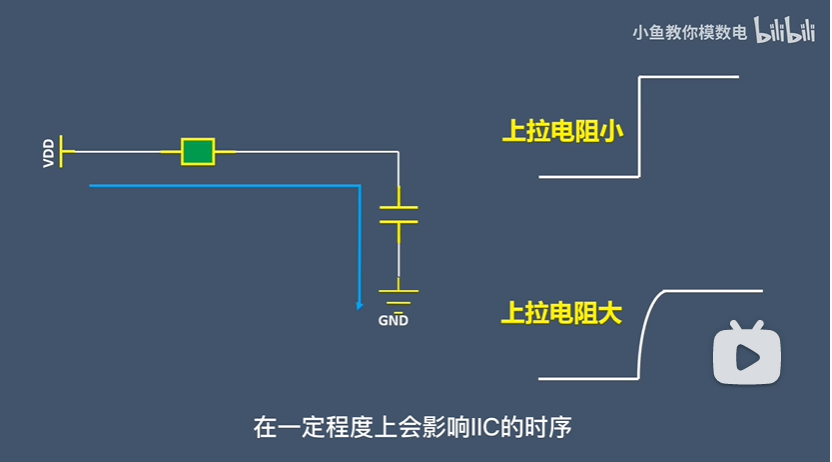

上拉电阻过大,IIC总线高电平的驱动能力会比较差。总线电平从0到1变化时,等效为RC充电电路,上拉电阻越大,波形上升越短,在一定程度上会影响IIC的时序,可能会出现误码。

IIC SDA和SCL信号的上升时间和总线电容在不同模式下有不同的要求:

IIC信号上升时间可以根据如下公式计算:

其中就是IIC总线的等效负载电容。

IIC信号上拉电阻也不能太小,如果太小了,当IIC引脚输出低电平时,灌进芯片IIC引脚的电流就会变大,可能会使IIC信号线的低电平变大。同时IO口电流过大还会烧毁芯片。我们一般要求IIC引脚在低电平时,流过芯片IIC引脚的电流小于3mA。

电源电压决定上拉电阻的最小值,总线负载电容决定上拉电阻的最大值。IIC信号上拉电阻取值常用的是4.7kΩ,一般小于10kΩ,大于1kΩ。如果IIC总线比较长,从设备比较多,可以适当降低电阻阻值。

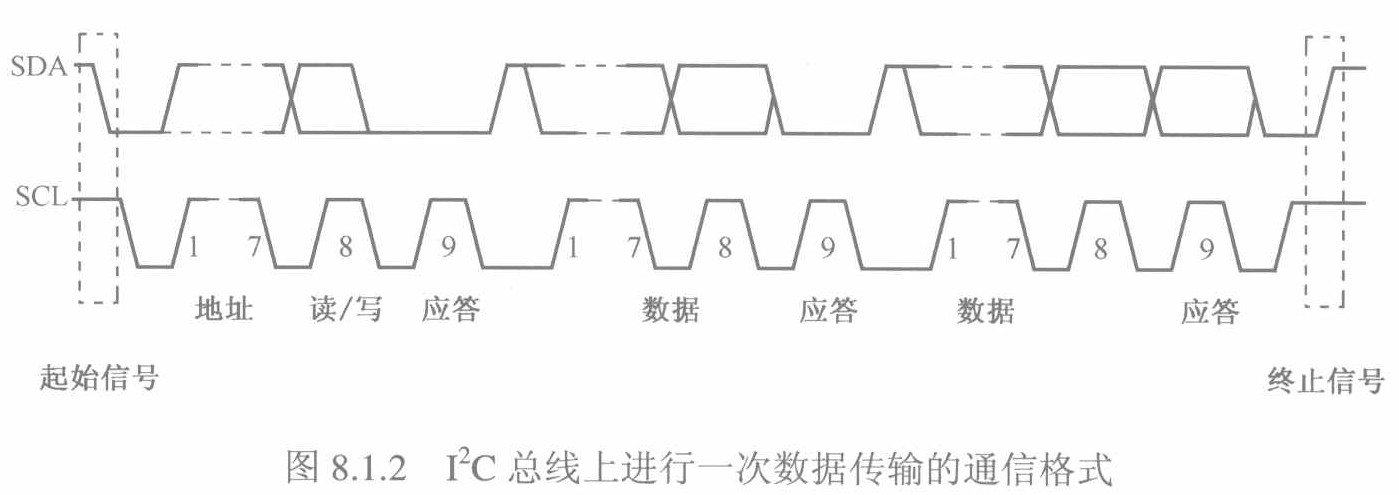

IIC总线通信格式

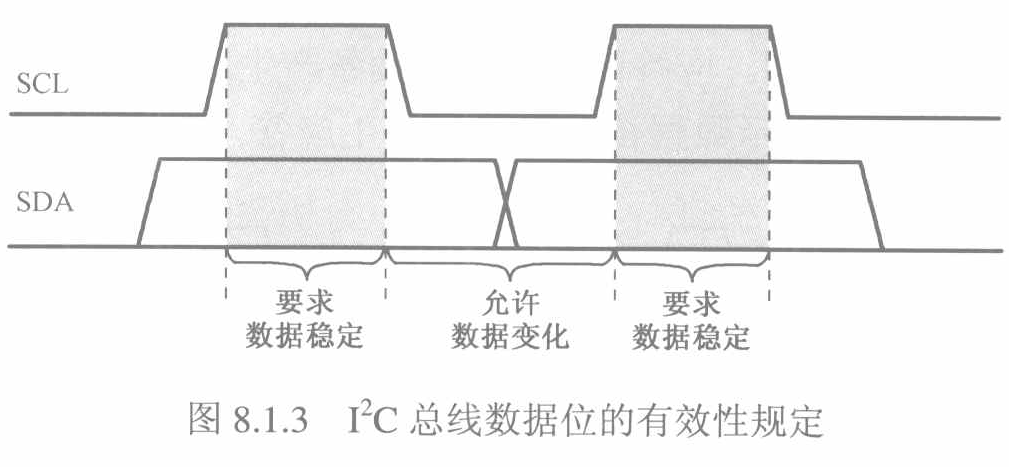

数据位的有效性规定

I2C 总线进行数据传送时,时钟信号为高电平期间,数据线上的数据必须保持稳定,只有在时钟信号为低电平期间,数据线上的高电平或低电平状态才允许变化。

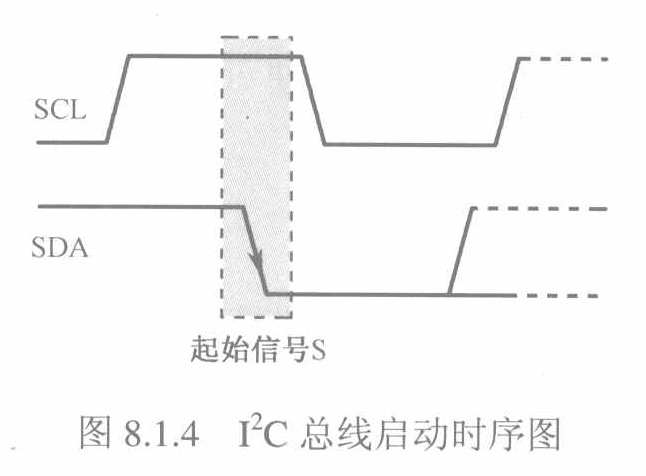

发送启动信号

在利用 l2C 总线进行一次数据传输时,首先由主机发出启动信号,启动 l2C 总线。SCL 为高电平期间, SDA 出现下降沿则为启动信号。此时,具有 I2C 总线接口的从器件会检测到该信号。

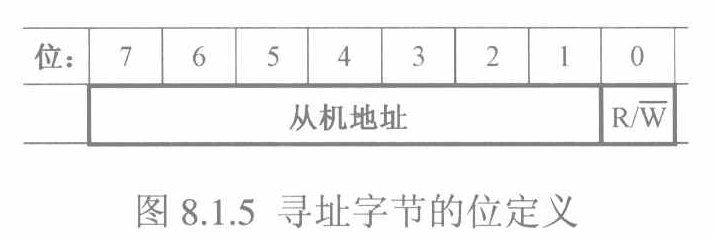

发送寻址信号

主机发送启动信号后,再发出寻址信号。器件地址有 7 位和 10 位两种。

寻址信号由一个字节构成,高 7 位为地址位,最低位为方向位,用以表明主机与从器件的数据传送方向。方向位为 0, 表明主机接下来对从器件进行写操作;方向位为 1,表明主机接下来对从器件进行读操作。

主机发送地址时,总线上的每个从机都将这 7 位地址码与自己的地址进行比较,如果相同,则认为自己正被主机寻址,根据最后一位将自已确定为发送器或接收器。

从机的地址由固定部分和可编程部分组成。

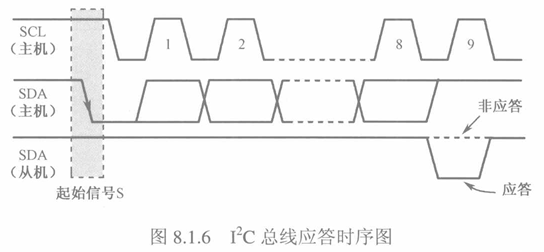

应答信号

I2C 总线协议规定,每传送一个字节数据(含地址及命令字)后,都要有一个应答信号,以确定数据传送是否被对方收到。应答信号由接收设备产生,在 SCL 信号为高电平期间,接收设备将 SDA 拉为低电平,表示数据传输正确,产生应答。

数据传输

主机发送寻址信号并得到从器件应答后,便可进行数据传输,每次一个字节,但每次传输都应在得到应答信号后再进行下一字节传送。

非应答信号

当主机为接收设备时,主机对最后一个字节不应答,以向发送设备表示数据传送结束。

停止信号

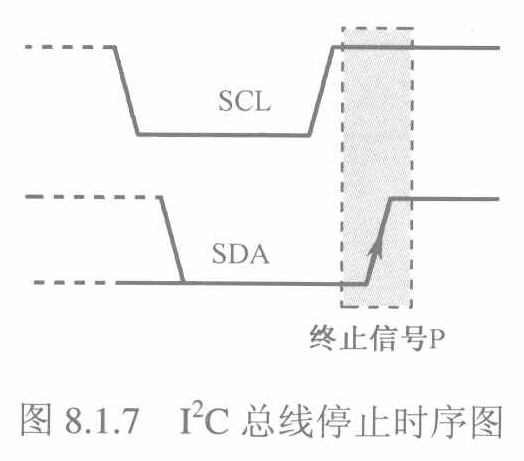

在全部数据传送完毕后,主机发送停止信号,即在 SCL 为高电平期间, SDA 上产生一上升沿信号。

单片机I2C总线通信

目前市场上很多单片机都已经具有硬件 I2C 总线控制单元,这类单片机在工作时,总线状态由硬件监测,无须用户介入,操作非常方便。但是还有许多单片机并不具有 l2C 总线接口,如 51 单片机,不过我们可以在单片机应用系统中通过软件模拟 I2C 总线的工作时序,在使用时,只需正确调用各个函数就能方便地扩展 I2C 总线接口器件。

为了保证数据传送的可靠性,标准I2C总线的数据传送有严格的时序要求。I2C总线的起始信号、终止信号、应答或发送“0”、非应答或发送“1”的模拟时序如图所示: