从沙子到单晶硅

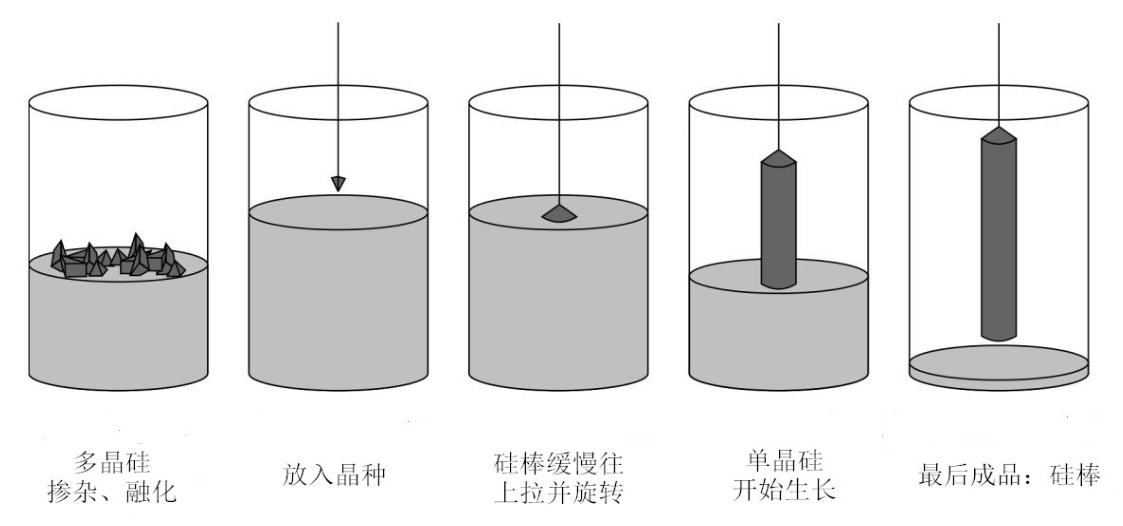

如何从沙子中提取单晶硅呢?沙子的主要成分是二氧化硅,这就涉及一系列化学反应了,其中最主要的过程就是使用碳经过化学反应将二氧化硅还原成硅。经过还原反应生成的硅叫粗硅,粗硅里面包含很多杂质,如铁、碳元素,还达不到制造芯片需要的纯度(需要99.999999999%以上)标准,需要进一步提纯。提纯也需要一系列化学反应,如通过盐酸氯化、蒸馏等步骤。提取的硅纯度越高,质量也就越高。经过一系列化学反应、提纯后生成的硅是多晶硅。将生成的多晶硅放入高温反应炉中融化,通过拉晶做出单晶硅棒。

为了增强硅的导电性能,一般会在多晶硅中掺杂一些硼元素或磷元素,待多晶硅融化后,在溶液中加入硅晶体晶种,同时通过拉杆不停旋转上拉,就可以拉出圆柱形的单晶硅棒。

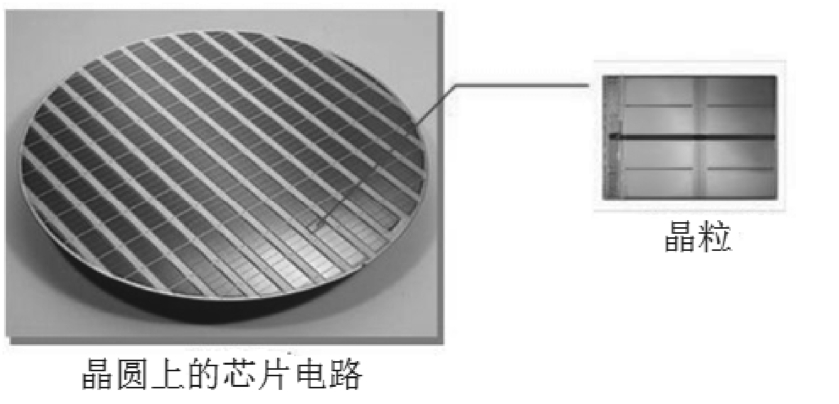

接下来,将这些单晶硅棒像切黄瓜一样,切成一片一片的,每一片我们称为晶圆(wafer)。晶圆是设计集成电路的载体,我们设计的模拟电路或数字电路,最终都要在晶圆上实现。晶圆上的芯片电路尺寸随着半导体工艺的发展也变得越来越小,目前已经达到了纳米级,越来越精密的半导体工艺除了要求单晶硅的纯度极高,晶圆的表面也必须光滑平整,切好的晶圆还需要进一步打磨抛光。晶圆表面需要光滑平整到什么程度呢?打个比方,假如需要从北京到上海铺设一段铁轨,对铁轨的要求就是两者之间的高度差不超过1mm。一粒灰尘落在晶圆上,就好像一块大石头落在马路上一样,会对芯片的良品率产生很大的影响,所以大家会看到芯片的生产车间对空气的洁净度要求非常高,员工必须穿着防尘服才能进入。

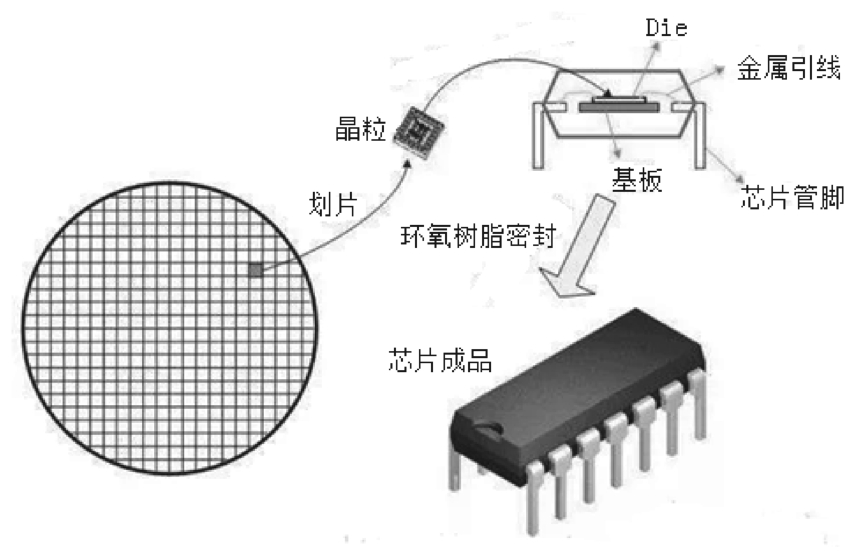

在每一个晶圆上,都可以实现成千上万个芯片电路,晶圆上的每一个小格子都是一个芯片电路的物理实现,我们称之为晶粒(Die)。

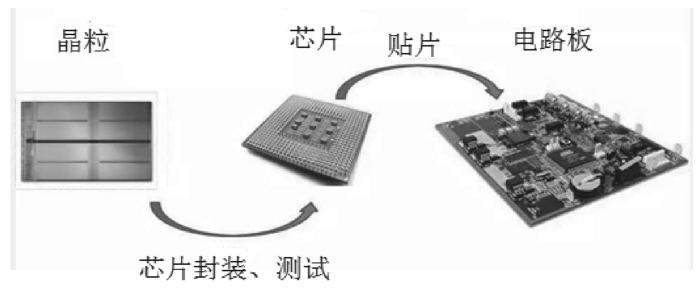

接下来还要对晶圆上的这些芯片电路进行切割、封装、引出管脚,然后就变成了市场上常见的芯片产品,最后才能焊接到我们的开发板上,做成整机产品。

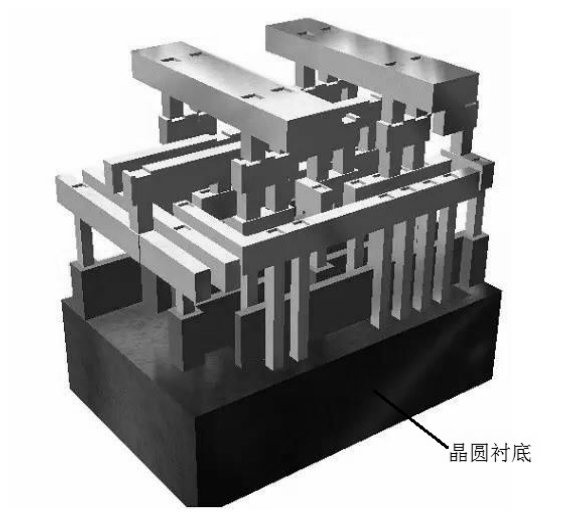

在一个晶圆上是如何实现电路的呢?将晶圆拿到显微镜下观察,你会发现,在晶圆的表面上全是纵横交错的3D电路,犹如一座巨大的迷宫。

要想弄明白在晶圆上是如何实现我们设计的电路的,就需要先了解一下电子电路和半导体工艺的知识。电路一般由大量的三极管、二极管、CMOS管、电阻、电容、电感、导线等组成,我们搞懂了一个CMOS元器件在晶圆上是如何实现的,基本上也就搞懂了整个电路在晶圆硅片上是如何实现的。这些电子元器件的实现原理,其实就是PN结的实现原理。PN结是构成二极管、三极管、CMOS管等半导体元器件的基础。

从PN结到芯片电路

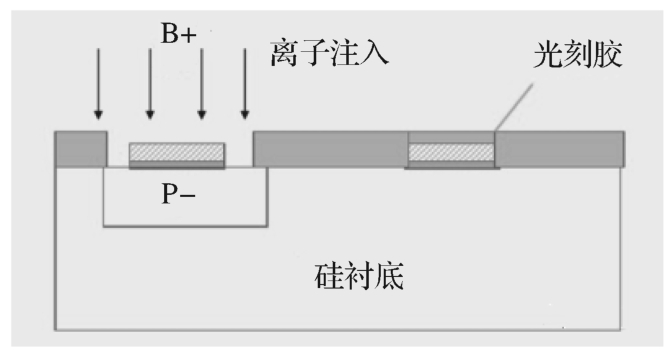

PN结的实现会涉及半导体工艺的方方面面,包括氧化、光刻、显影、刻蚀、扩散、离子注入、薄膜沉淀、金属化等主要流程。为了简化流程,方便理解,我们就讲讲两个核心的步骤:离子注入和光刻。离子注入其实就是掺杂,就是往单质硅中掺入三价元素硼和五价元素磷,进而生成由PN结构成的各种元器件和电路。而光刻则是在晶圆上给离子注入开凿各种掺杂的窗口。

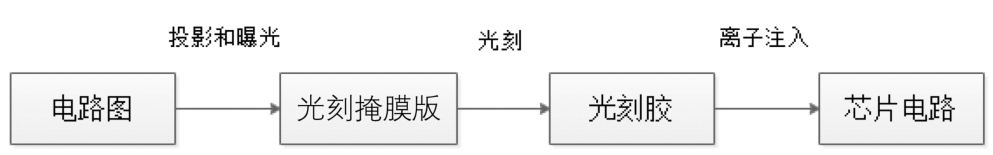

在晶圆上进行离子注入掺杂之前,首先要根据电路版图制作一个个掺杂窗口,如图所示,这一步需要光刻胶来协助完成:在硅衬底上涂上一层光刻胶,通过紫外线照射掩膜版,将电路图形投影到光刻胶上,生成一个个掺杂窗口,并将不需要掺杂的区域保护起来。

那如何产生这个掺杂窗口呢?原理很简单,就和我们使用感光胶片去洗照片一样,还需要一个叫作光刻掩膜版的东西。光刻掩膜版原理和我们照相用的胶片差不多,由透明基板和遮光膜组成,通过投影和曝光,我们可以将芯片的电路版图保存在掩膜版上。然后通过光刻机的紫外线照射,利用光刻胶的感光溶解特性,被电路图形遮挡的阴影部分的光刻胶保存下来,而被光照射的部分的光刻胶就会溶解,成为一个个掺杂窗口。最后通过离子注入,掺杂三价元素和五价元素,就会在晶圆的硅衬底上生成主要由PN结构成的各种CMOS管、晶体管电路。

随着集成电路规模越来越大,在一个几英寸的晶圆硅衬底上,要实现千万门级、甚至上亿门级的电路,需要几十亿个晶体管,电路的实现难度也变得越来越大。尤其是纳米级的电路,如现在流行的14nm、7nm、5nm工艺制程,要将千万门级的晶体管电路都刻在一个指甲盖大小的硅衬底上,这就要求电路中的每个元器件尺寸都要非常小,同时要求“感光胶片”要非常精密,对电路图形的分辨率要非常高。这时候光刻机就闪亮登场了,光刻机主要用来将你设计的电路图映射到晶圆上,通过光照将你设计的电路图形投影到光刻胶上,光刻胶中被电路遮挡的部分被保留,溶解的部分就是掺杂的窗口。晶体管越多,电路越复杂,工艺制程越先进,对光刻机的要求越高,因为需要非常精密地把复杂的电路图形投影到晶圆的硅衬底上。

芯片封装

:::info

相关阅读:芯片封装技术

:::

单纯的芯片电路无法直接焊接到硬件电路板上,如图所示,还需要经过切割、封装、引出管脚、芯片测试等后续流程,测试通过后经过包装,才会变成市场上我们看到的芯片的样子。

芯片的封装主要就是给芯片电路加一个外壳,引出管脚。芯片的封装不仅可以起到密封、保护芯片的作用,还可以通过管脚,直接将芯片焊接到电路板上。芯片的封装技术经过几十年的发展,越来越先进,芯片的面积也越来越小。

随着市场上智能手表、运动手环等智能硬件的流行,对芯片的封装尺寸也有了更严苛的要求,层叠封装(Package-on-Package,PoP)技术此时就应运而生了。PoP可以将多个芯片元器件分层堆叠、互连,封装在一个芯片内,从而让整个芯片更薄、体积更小。现在很多智能手机,为了薄化电路板,一般会将LPDDR内存芯片和eMMC存储芯片封装在一起,或者将应用处理器和基带芯片封装在一起。如苹果的iWatch,直接将应用处理器、LPDDR4X DRAM和eMMC Flash存储芯片封装在一个芯片内,大大减少了整个芯片和电路板的尺寸,然后和发动机、电池板等器件像汉堡一样三层封装在一起,可以将整个电子产品做得更加轻薄、小巧。