高级控制定时器时基单元包含

| 数量 | 寄存器名称 | 位数 | 说明 |

|---|---|---|---|

| 1 | 自动重载计数器 ARR | 16 位 | |

| 1 | 计数器CNT | 16 位 | 可向上/下计数 |

| 1 | 可编程预分频器 PSC | 16位 | 预分频器时钟源有多种可选,有内部的时钟、外部时钟。 |

| 1 | 重复计数器 RCR | 8位 | 这样最高可实现 40 位的可编程定时 |

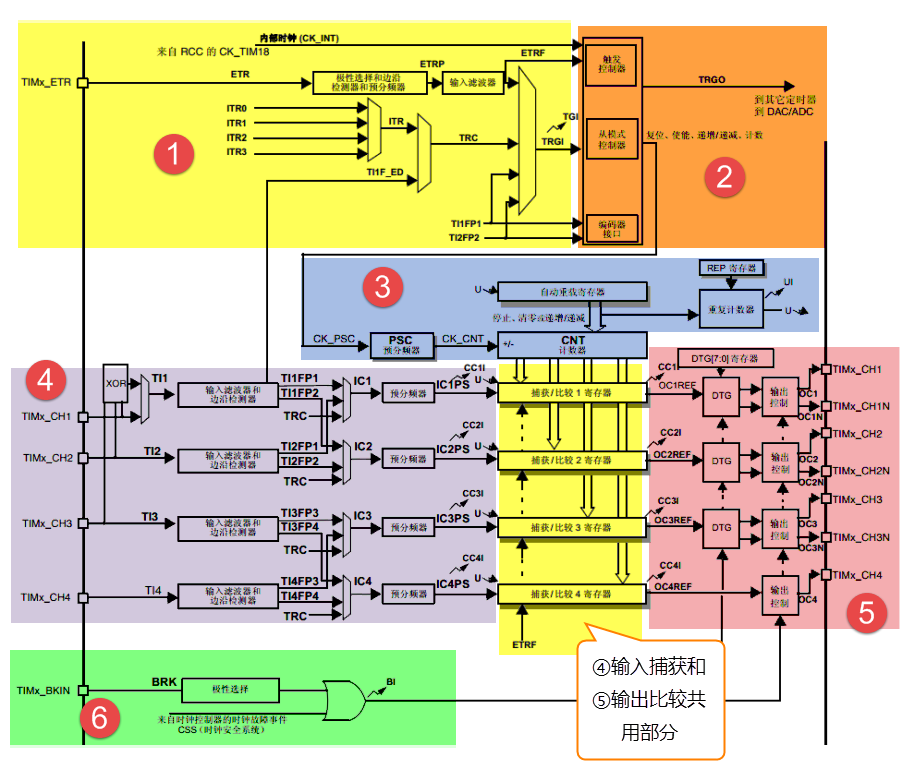

功能框图

①时钟源

高级控制定时器有四个时钟源可选:

内部时钟源 CK_INT

外部时钟模式 1:外部输入引脚 TIx(x=1,2,3,4)

外部时钟模式 2:外部触发输入 ETR

内部触发输入

②控制器

高级控制定时器控制器部分包括触发控制器、从模式控制器以及编码器接口。

| 触发控制器 | 用来针对片内外设输出触发信号,比如为其它定时器提供时钟和触发 DAC/ADC 转换。 |

|---|---|

| 编码器接口 | 专门针对编码器计数而设计。 |

| 从模式控制器 | 可以控制计数器复位、启动、递增/递减、计数。 |

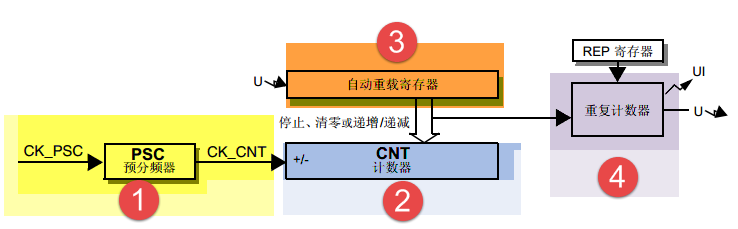

③时基单元

预分频器 PSC

预分频器 PSC,有一个输入时钟 CK_PSC 和一个输出时钟 CK_CNT。

输入时钟CK_PSC 就是上面时钟源的输出,

输出 CK_CNT 则用来驱动计数器 CNT 计数。

通过设置预分频器 PSC 的值可以得到不同的 CK_CNT,可以实现 1 至 65536 分频。

实际计算为:

fCK_CNT=fCK_PSC / (PSC[15:0]+1)

计数器 CNT

高级控制定时器的计数器有三种计数模式,分别为递增计数模式、递减计数模式和递增/递减(中心对齐)计数模式。

| 递增计数模式下 | 计数器从 0 开始计数,每来一个 CK_CNT 脉冲计数器就增加 1,直到计数器的值与自动重载寄存器 ARR 值相等,然后计数器又从 0 开始计数并生成计数器上溢事件,计数器总是如此循环计数。 如果禁用重复计数器,在计数器生成上溢事件就马上生成更新事件(UEV); 如果使能重复计数器,每生成一次上溢事件重复计数器内容就减 1,直到重复计数器内容为 0 时才会生成更新事件。 |

|---|---|

| 递减计数模式下 | 计数器从自动重载寄存器 ARR 值开始计数,每来一个 CK_CNT 脉冲计数器就减 1,直到计数器值为 0,然后计数器又从自动重载寄存器 ARR 值开始递减计数并生成计数器下溢事件,计数器总是如此循环计数。 |

如果禁用重复计数器,在计数器生成下溢事件就马上生成更新事件;

如果使能重复计数器,每生成一次下溢事件重复计数器内容就减 1,直到重复计数器内容为 0 时才会生成更新事件。 |

| 中心对齐模式下 | 计数器从 0 开始递增计数,直到计数值等于(ARR-1)值生成计数器上溢事件

然后从 ARR 值开始递减计数直到 1 生成计数器下溢事件。

然后又从 0 开始计数,如此循环。每次发生计数器上溢和下溢事件都会生成更新事件。

|

自动重载寄存器 ARR

自动重载寄存器 ARR 用来存放与计数器 CNT 比较的值,如果两个值相等就递减重复计数器。

可以通过 TIMx_CR1 寄存器的 ARPE 位控制自动重载影子寄存器功能,

| 如果ARPE 位为1 | 自动重载影子寄存器有效,只有在事件更新时才把 TIMx_ARR 值赋给影子寄存器。 |

|---|---|

| 如果 ARPE 位为 0 | 则修改 TIMx_ARR 值马上有效。 |

重复计数器 RCR

高级控制定时器在硬件结构上多出了重复计数器,在定时器发生上溢或下溢事件是递减重复计数器的值,只有当重复计数器为 0 时才会生成更新事件。

在发生 N+1 个上溢或下溢事件(N 为 RCR 的值)时产生更新事件。

④输入捕获

⑤输出比较

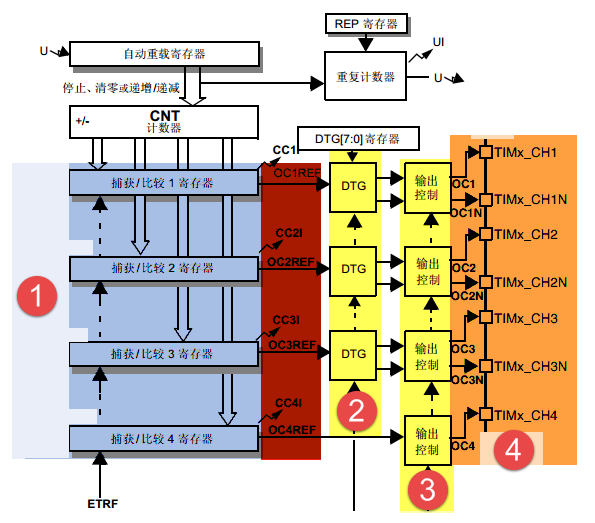

①比较寄存器

当计数器 CNT 的值跟比较寄存器 CCR 的值相等的时候,输出参考信号 OCxREF 的信号的极性就会改变,

OCxREF=1(高电平)称之为有效电平,

OCxREF=0(低电平)称之为无效电平,

并且会产生比较中断 CCxI,

相应的标志位 CCxIF(SR 寄存器中)会置位。然后 OCxREF 再经过一系列的控制之后就成为真正的输出信号 OCx/OCxN。

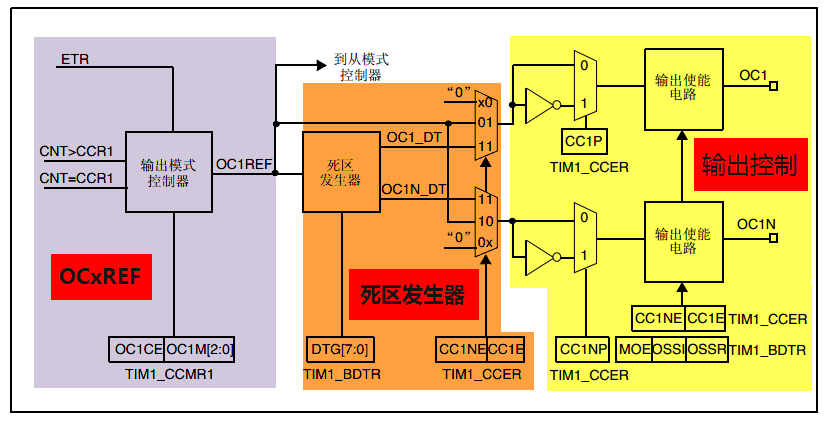

②死区发生器

在生成的参考波形 OCxREF 的基础上,可以插入死区时间,

用于生成两路互补的输出信号 OCx 和 OCxN,死区时间的大小具体由 BDTR 寄存器的位 DTG[7:0]配置。

死区时间的大小必须根据与输出信号相连接的器件及其特性来调整。

③输出控制

在输出比较的输出控制中,参考信号 OCxREF 在经过死区发生器之后会产生两路带死区的互补信号 OCx_DT 和 OCxN_DT

(通道 1~3 才有互补信号,通道 4 没有,其余跟通道1~3 一样),这两路带死区的互补信号然后就进入输出控制电路,如果没有加入死区控制,

那么进入输出控制电路的信号就直接是 OCxREF。

进入输出控制电路的信号会被分成两路,一路是原始信号,一路是被反向的信号,具体的由寄存器 CCER 的位 CCxP 和 CCxNP 控制。

经过极性选择的信号是否由 OCx 引脚输出到外部引脚 CHx/CHxN 则由寄存器 CCER 的位 CxE/CxNE 配置。

如果加入了断路(刹车)功能,则断路和死区寄存器 BDTR 的 MOE、OSSI 和 OSSR这三个位会共同影响输出的信号。

⑥断路功能

应用

输出比较应用

PWM 输出模式

PWM 输出就是对外输出脉宽(即占空比)可调的方波信号

:::info

信号频率由自动重装寄存器 ARR 的值决定

占空比由比较寄存器 CCR 的值决定。

:::

| 模式 | 计数器CNT计算方式 | 说明 |

|---|---|---|

| PWM1 | 递增 | CNT< CCR,通道CH为有效,否则为无效 |

| 递减 | CNT>CCR,通道CH为无效,否则为有效 | |

| PWM2 | 递增 | CNT<CCR,通道 CH 为无效,否则为有效 |

| 递减 | CNT>CCR,通道 CH 为有效,否则为无效 |

标准库

TIM_TimeBaseInitTypeDef

时基结构体

typedef struct {uint16_t TIM_Prescaler; // 预分频器uint16_t TIM_CounterMode; // 计数模式uint32_t TIM_Period; // 定时器周期uint16_t TIM_ClockDivision; // 时钟分频uint8_t TIM_RepetitionCounter; // 重复计算器} TIM_TimeBaseInitTypeDef;

TIM_OCInitTypeDef

输出比较结构体

typedef struct {uint16_t TIM_OCMode; // 比较输出模式uint16_t TIM_OutputState; // 比较输出使能uint16_t TIM_OutputNState; // 比较互补输出使能uint32_t TIM_Pulse; // 脉冲宽度uint16_t TIM_OCPolarity; // 输出极性uint16_t TIM_OCNPolarity; // 互补输出极性uint16_t TIM_OCIdleState; // 空闲状态下比较输出状态uint16_t TIM_OCNIdleState; // 空闲状态下比较互补输出状态} TIM_OCInitTypeDef;

TIM_ICInitTypeDef

输出捕获结构体

typedef struct {uint16_t TIM_Channel; // 输入通道选择uint16_t TIM_ICPolarity; // 输入捕获触发选择uint16_t TIM_ICSelection; // 输入捕获选择uint16_t TIM_ICPrescaler; // 输入捕获预分频器uint16_t TIM_ICFilter; // 输入捕获滤波器} TIM_ICInitTypeDef;

TIM_BDTRInitTypeDef

断路和死区结构体

typedef struct {uint16_t TIM_OSSRState; // 运行模式下的关闭状态选择uint16_t TIM_OSSIState; // 空闲模式下的关闭状态选择uint16_t TIM_LOCKLevel; // 锁定配置uint16_t TIM_DeadTime; // 死区时间uint16_t TIM_Break; // 断路输入使能控制uint16_t TIM_BreakPolarity; // 断路输入极性uint16_t TIM_AutomaticOutput; // 自动输出使能} TIM_BDTRInitTypeDef;