基本概念

什么是DMA?

- 为实现数据高速在外设寄存器与存储器之间或者存储器与存储器之间传输提供了高效的方法。

- DMA 传输实现高速数据移动过程无需任何 CPU 操作控制。

- DMA 控制器是独立于 Cortex-M4 内核的

功能框图

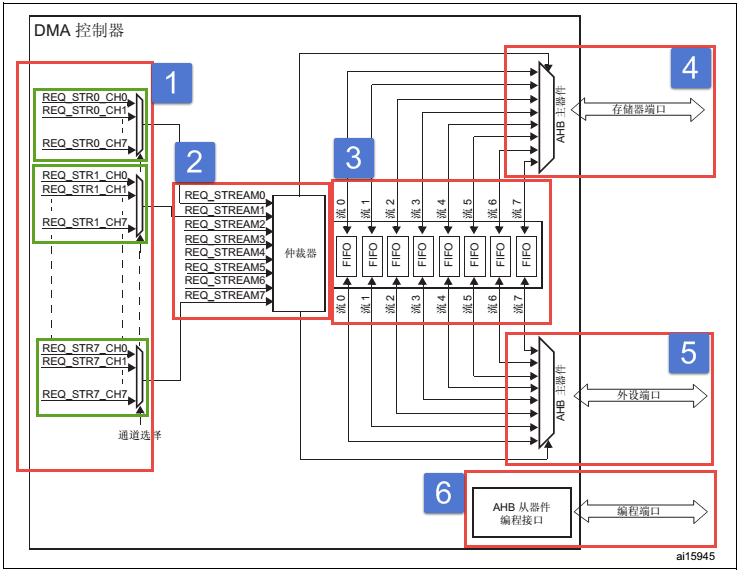

①外设通道选择

STM32F4xx 系列资源丰富,具有两个 DMA 控制器,同时外设繁多,为实现正常传输,DMA 需要通道选择控制。

每个 DMA 控制器具有 8 个数据流,每个数据流对应 8 个外设请求。(总共可以处理64个请求)

在实现 DMA 传输之前,DMA 控制器会通过 DMA 数据流 x 配置寄存器 DMA_SxCR(x为 0~7,对应 8 个 DMA 数据流)

的 CHSEL[2:0]位选择对应的通道作为该数据流的目标外设。

DMA1 请求映射

| 外设请求 | 数据流0 | 数据流1 | 数据流2 | 数据流3 | 数据流4 | 数据流5 | 数据流6 | 数据流 7 |

|---|---|---|---|---|---|---|---|---|

| 通道0 | SPI3 RX | SPI3 RX | SPI2 RX | SPI2 TX | SPI3_ TX | SPI3 TX | ||

| 通道1 | I2C1 RX | TIM7 UP | TIM7 UP | I2C1 RX | I2C1 TX | I2C1TX | ||

| 通道2 | TIM4 CH1 | I2S3_ EXT RX | TIM4 CH2 | I2S2EXT TX | I2S3 EXT TX | TIM4 UP | TIM4 C H3 |

| 通道3 | I2S3 EXT RX | TIM2 UP TIM2 CH 3 |

2C3 RX | I2S2 EXT RX | I2C3TX | TIM2 CH1 | TIM2 CH 2 TIM2 CH 4 | |

|---|---|---|---|---|---|---|---|---|

| 通道4 | UART5 R X | USART3_ RX | UART4R X | USART3T X | UART4 T X | USART2_ RX | USART2 TX | UART5 TX |

| 通道5 | UART8_ T X | UART7_ T X | TIM3 CH4 TIM3 UP | UART7 R X | TIM3 CH1 TIM3 TRI G | TIM3 CH2 | UART8 _R X | TIM3_ C H3 |

| 通道6 | TIM5 CH3 TIM5_ UP | TIM5_ CH 4 TIM5 TRI G | TIM5 CH1 | TIM5 CH4 TIM5 TRI G | TIM5 CH2 | TIM5 UP | ||

| 通道7 | TIM6 UP | I2C2RX | 2C2RX | USART3 TX | DAC1 | DAC2 | I2C2TX |

DMA2 请求映射

| 外设 请求 | 数据流0 | 数据流1 | 数据流2 | 数据流 3 | 数据流4 | 数据流5 | 数据流6 | 数据流7 |

|---|---|---|---|---|---|---|---|---|

| 通道0 | ADC1 | TIM8 CHI TIM8 CH2 TIM8 CH3 | ADC1 | TIM1 CH1 TIMI CH2 TIM1 I CH3 | ||||

| 通道1 | DCMI | ADC2 | ADC2 | SPI6TX | SPI6 RX | DCMI | ||

| 通道2 | ADC3 | ADC3 | SPI5 TX | SPI5TX | CRYP OU T | CRYP IN | HASH_ N | |

| 通道3 | SPI1_ RX | SPI1. RX | SPI1_ TX | SPI1_ TX | ||||

| 通道4 | SPI4 RX | SPI4TX | USART1_ _R X | SDIO | USARTI RX | SDIO | USART1 TX | |

| 通道5 | USART6 RX | USART6 R X | SPI14 R X | SPI4 _TX | USART6_ TX | USART6 TX | ||

| 通道6 | TIM1 TRIG | TIMl CH 1 | TIM1 CH2 | TIM1 ! C H1 | TM1_ CH 4 TIMI CO M TIM1 TR IG | TIMI UP | TIM1 CH3 | |

| 通道7 | TIM8 UP | TIM8 CH1 | TIM8_ C H2 | TIM8_ CH 3 | SPI5 RX | SPI5 TX | TIM8_ CH4 TIM8 TRI G TIM8 CO M |

②仲裁器

一个 DMA 控制器对应 8 个数据流,数据流包含要传输数据的源地址、目标地址、数据等等信息。

仲裁器管理数据流方法分为两个阶段:

- 软件阶段

- 配置数据流时可以通过寄存器设定它的优先级别

- 具体配置 DMA_SxCR 寄存器 PL[1:0]位,

- 可以设置为非常高、高、中和低四个级别。

- 硬件阶段

- 如果两个或以上数据流软件设置优先级一样,则他们优先级取决于数据流编号,编号越低越具有优先权

③FIFO

每个数据流都独立拥有四级 32 位 FIFO(先进先出存储器缓冲区)。

传输模式分为:直接模式 间接模式

:::info

❗️ 直接模式:

如果 DMA 配置为存储器到外设传输那 DMA 会见一个数据存放在 FIFO 内,如果外设启动 DMA 传输请求就可以马上将数据传输过去。

:::

:::info

❗️ 间**接模式**:

用于在源数据传输到目标地址之前临时存放这些数据。

可以通过 DMA 数据流xFIFO 控制寄存器 DMA_SxFCR 的 FTH[1:0]位来控制 FIFO 的阈值,

分别为 1/4、1/2、3/4和满。如果数据存储量达到阈值级别时,FIFO 内容将传输到目标中。

:::

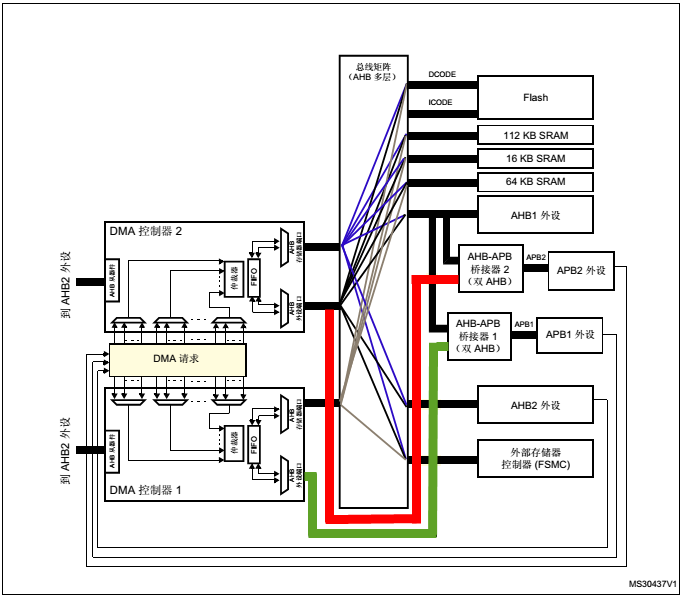

④存储器端口、⑤外设端口

DMA 控制器实现双 AHB 主接口,更好利用总线矩阵和并行传输。

DMA2 存储器和外设端口可以访问相关的内存地址,包括有内部Flash、内部 SRAM、AHB1 外设、AHB2 外设、APB2 外设和外部存储器空间。

DMA1 的存储区端口相比 DMA2 的要减少 AHB2 外设的访问权,

同时 DMA1 外设端口是没有连接至总线矩阵的,只有连接到 APB1 外设,所以 DMA1 不能实现存储器到存储器传输。