一、为什么要有CPU Cache?

Cache(即高速缓冲存储器(Cache Memory)。

随着集成电路工艺的不断发展CPU的频率不断提升,而与此同时由于制造工艺和成本限制,计算机在内存(主要为DRAM)访问速度缺没有质的突破。当然,当前技术并不是做不出来访问频率更高的内存,而是SRAM那样的高速内存相对于普通内存DRAM而言成本过高。因此,当前系统选择一个折中办法,即在CPU和内存之间引入快速而成本较高的SDRAM作为高速缓存(cache),以此作为CPU和内存之间的通道。

一般的计算机程序对存储器的访问行为,存在很大的局部性,主要分为两个方面:

时间局部性与空间局部性。

时间局部性:即程序会在一个比较短的时间窗口内频繁访问同一个内存地址。

空间局部性:即程序会倾向于访问一组数据或者一个数据相邻的数据。

Cache正是利用了程序访存的这两个局部性特点,将程序最常使用的指令与数据放在离CPU流水线最近的地方,以便在需要时最快地获取这部分指令与数据。

二、为什么要有多级 CPU Cache?

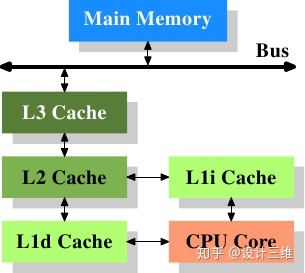

随着科技发展,热点数据的体积越来越大,单纯的增加一级缓存大小的性价比已经很低了。因此,就慢慢出现了在一级缓存(L1 Cache)和内存之间又增加一层访问速度和成本都介于两者之间的二级缓存(L2 Cache)。此外,又由于程序指令和程序数据的行为和热点分布差异很大,因此L1 Cache也被划分成L1i 指令缓存(i for instruction)和L1d 数据缓存(d for data)两种专门用途的缓存。

各级缓存与主内存之间的响应时间

各级缓存对比:

L1 Cache速度最快、容量最小(靠近CPU)

L2 Cache速度与容量都居中

L3 Cache容量最大,但速度相对最慢(靠近主内存)

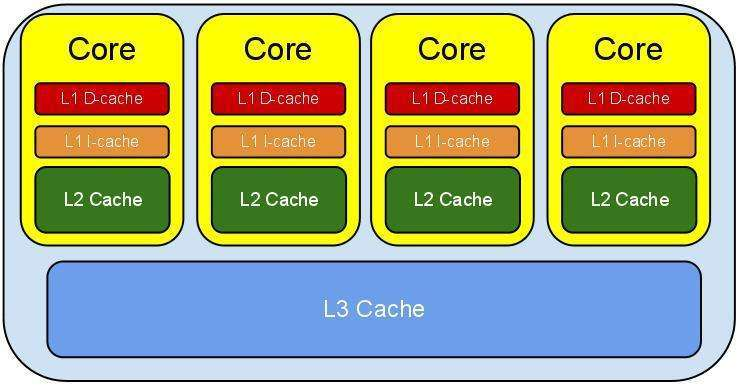

三、CPU Cache架构:

CPU Cache架构

CPU包含多个核心,每个核心又有独自的一级缓存(L1 Cache也被划分成L1i 指令缓存和L1d 数据缓存)和二级缓存,各个核心之间共享三级缓存,并统一通过总线与内存进行交互。

四、CPU Cache Line

Cache Line可以理解为CPU Cache中的最小缓存单位。其大小是以突发读发写周期的大小为基础的。目前主流的CPU Cache的Cache Line大小都是64Bytes。假设我们有一个512B的一级缓存,那么按照64B的Cache Line大小来算,这个一级缓存所能存放的Cache Line个数为512/64 = 8个。CPU不是按字节访问内存,而是以64字节为单位的块(chunk)拿取,称为一个cache line。当你读一个特定地址的内存时,整个Cache Line大小的内存将从主存换入缓存,并且这是cpu访问同一个Cache Line内的其它值开销是很小的。