写在前面

接口综合是在C设计中加入RTL端口的过程。

除了将物理端口添加到RTL设计之外,接口合成还包括一个相关的I/O协议,允许通过端口的数据传输与内部逻辑自动和最优地同步。

Lab1

回顾函数返回和块级协议。

函数返回值为sum

与ug871中不同,因为这里的实验中加入了一句#pragma HLS INTERFACE ap_ctrl_none port=return,所以少了ap_ctrl_hs协议接口。

默认的块级I/O协议就是ap_ctrl_hs。

Output signal ap_ready goes high to indicate the design is ready for new inputs on the next clock.

输出信号ap_ready高,以表明设计已准备好在下一个时钟上的新输入。

Output signal ap_done indicates when the design is finished and that the value on output port ap_return is valid (the first output value, 60, is the sum of all three inputs).

输出信号ap_done指示设计完成时,输出端口ap_return上的值是有效的。

ug871说不添加块级协议,无法使用RTL CoSimulation。我试了试,本例程可以跑,或许他实现了加法,属于纯组合逻辑设计。

Cosim只支持以下“ap_ctrl_none”设计:

(1)组合设计;

(2)任务间隔为1的流水线设计;

(3)具有阵列流或hls_stream端口的设计。

Lab2

了解默认IO协议,学习选择IO协议。

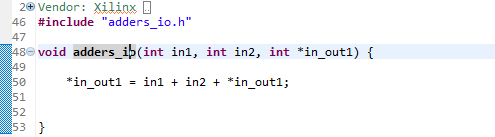

这里使用了指针。这一次,代码没有函数返回,而是通过指针参数*in_out1传递函数的输出。这也为探索双向(输入和输出)端口的接口选项提供了机会。

指针参数既是函数的输入,也是函数的输出。 在RTL设计中,此参数作为单独的输入和输出端口实现。

在Source和Directive中选择Directive,可以把策略写进Directive.tcl,对应%

如果选择Source,则会以#pragma的形式写进源代码,对应#

Lab3

回顾数组端口的实现和划分。

acc[rem]不需要初始化为0吗?或者默认已经进行了初始化。

与例子相比,多了一个temp。避免自己读自己?还是说HLS无法处理这个问题。

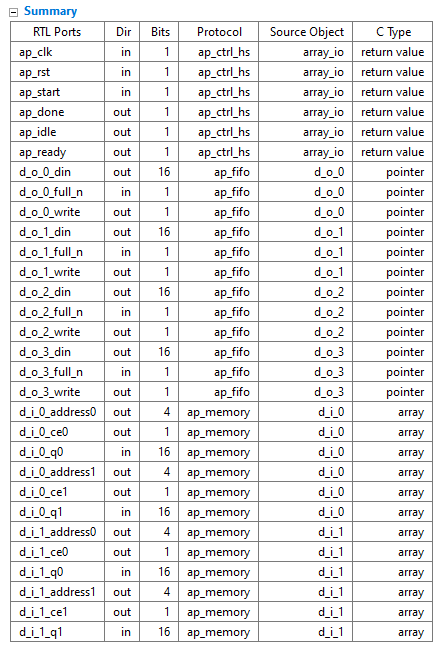

d_i参数已合成到类似的RAM接口,但具有输入数据端口(d_i_q0),并且没有可写端口,因为该接口只读取数据。

注意:如果您指定了双端口RAM,而VivadoHLS只能确定只需要一个端口,则它使用单端口并覆盖双端口规范。 在本设计中,如果要使用多个RTL端口实现数组参数,首先必须做的是打开for-loop,并允许所有内部操作并行进行,否则在多个端口中没有好处:滚动的for-loop确保一次只能读取(或写入)一个数据样本。

RAM_2P_BRAM中的2P代表2个端口,双端口代表可以同时读两个数据。对于HLS,必须用的上,才会被实现。

block代表像发牌一样划分output-ram

该设计具有标准时钟、复位和块级I/O端口。 阵列参数d_o已作为四个单独的FIFO接口实现。 参数d_i已作为两个独立的RAM接口实现,每个接口都使用双端口接口。

如果数组被划分为单个元素,则不能将其分配给块RAM。所以要把RAM_2P_BRAM删掉。

切得越碎,跑得越快。

Lab4

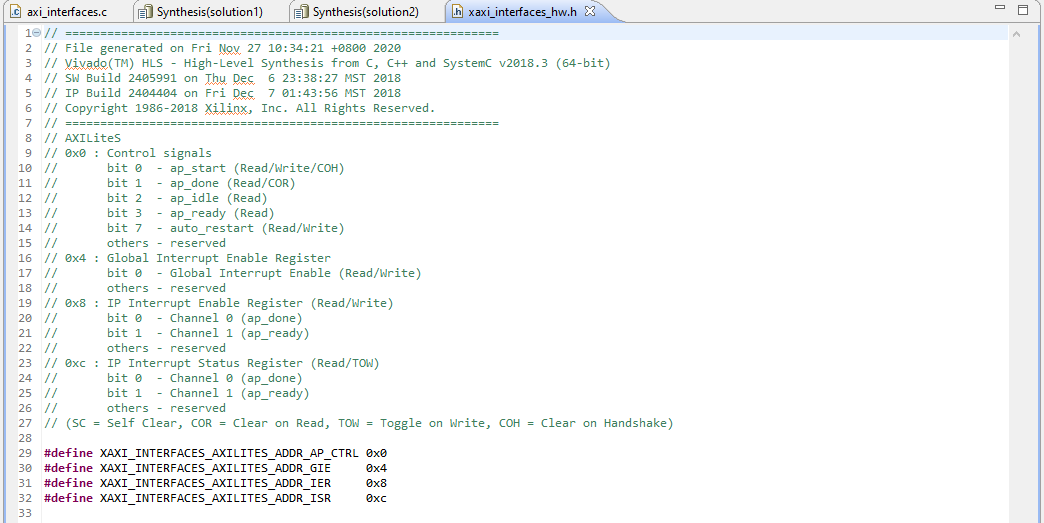

创建一个优化的设计实现,并添加AXI4端口。

指定要实现的数组参数为AXI4-Stream接口。

如果数组被划分为通道,则可以通过并行设计为每个通道流样本。

最后,如果I/O端口被配置为提供和消耗单个信道数据流,则对for循环的部分展开可以确保每个信道的专用硬件处理。

When the top-level of the design is a loop, you can use the pipeline rewind option. This informs Vivado HLS that when implemented in RTL, this loop runs continuously (with no end of function and function re-start cycles).

pipeline rewind代表循环流水线。

处理完后Directive界面长这样。

综合出来的面积比Lab3的solution2、3、4都要小

数组接口的循环分区和部分for循环展开允许在硬件中将此C代码作为八个单独的通道实现。

对循环的加流水级允许每个通道中的逻辑每个时钟处理1个样本。 调整分区和循环展开允许您创建一个设计,该设计是区域和性能的最佳平衡,以满足您的特定需求。

总结

在本教程中:

什么是块级I/O协议以及如何控制它们。

如何指定和应用端口级I/O协议。

如何将数组端口指定为RAM和FIFO接口。

如何将RAM和FIFO接口划分为子端口。 (PARTITION)

如何使用I/O指令和优化指令创建具有AXI4接口的最佳设计。