写在前面

高层次综合的一个常见用途是为CPU创建一个加速器-将在CPU上执行的代码移动到FPGA可编程逻辑中,以提高性能。本教程展示了如何将使用高级合成创建的设计集成到Zynq设备中。

AXI

1、AXI是什么

AXI(Advanced eXtensible Interface)是一种总线协议,该协议的第一个版本AXI3是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分。2010发布的AMBA4.0包含了AXI的第二个版本AXI4。

1)AXI4:主要面向高性能地址映射通信的需求;

2)AXI4-Lite:是一个轻量级的,适用于吞吐量较小的地址映射通信总线;

3)AXI4-Stream:面向高速流数据传输。

2、AXI4协议的优势

1)高效:通过标准化的AXI接口,开发者只需要学习一种IP核的通讯协议即可;

2)易用:针对具体应用提供合适的接口协议。

AXI4:面向地址映射的接口,在单地址传输的情况下最大允许256个时钟周期的数据突发长度;

AXI4-Lite:一个轻量级的地址映射单次传输接口,占用较少的资源;

AXI4-Stream:去掉了地址传输的功能,允许无限制的数据突发传输,无需考虑地址映射。

3)易得:标准化的AXI接口协议资源,不仅可以在xilinx官网上获得,也可以在全球范围内ARM的所有合作伙伴处获得。

大量的IP core支持AXI4协议;

大量的第三方AXI工具可提供多样的系统开发、验证和功能定制。

Lab1

创建和配置一个简单的HLS设计,以便在Zynq设备上与CPU一起工作。本实验室使用的HLS设计很简单,可以让本教程的重点放在解释与CPU的连接以及如何配置由高级综合创建的软件驱动程序来控制设备和管理中断。

pre-production预生产、预处理

flow navigator流程导航器

STEP1

这个的project位置是有要求的。

block design这种设计方式我还是不推崇,个人认为应该通过RTL代码来完成连接。

STEP4

Run Block Automation在这个位置。under the title bar?这个指示并不到位。

Run Block Automation可以自动化任务,比如为ZYNQ PS7的DDR和FIXED_IO建立正确的外部连接。

Run Connection Automation可以直接连出下图,看上去非常方便。

成功后保存Block Design。

按着Ctrl+鼠标滚轮可以对IMPLEMENTED DESIGN的窗口进行放大缩小。

后续步骤设计上板,先不做。

暂停

暂停在STEP6的第6小步,启动ZC702板并测试HelloWorld应用程序。 确保板有所有的连接,以允许您下载FPGA设备上的比特流。 请参阅ZC702开发板附带的文档。

Lab2

Streaming Data Between the Zynq CPU and HLS Accelerator Blocks.

演示了一种常见的高性能连接方案,用于连接硬件加速器块,这些加速器块消耗来自CPU内存的数据和/或以流的方式产生发送给它的数据。实验强调了软件需求,以避免缓存一致性问题。

报错及解决

有报错,怀疑是return的问题,同上次一样。检查后发现不是,下图return err_cnt是没有问题的。

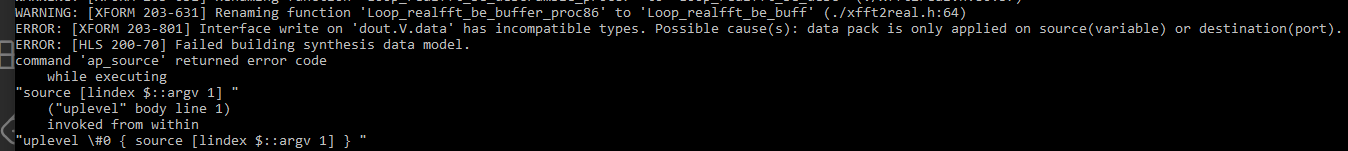

ERROR: [XFORM 203-801] Interface write on ‘dout.V.data’ has incompatible types. Possible cause(s): data pack is only applied on source(variable) or destination(port).

接口写入’dout.V。数据’具有不兼容的类型。可能的原因:数据包仅应用于源(变量)或目标(端口)。

ERROR: [HLS 200-70] Failed building synthesis data model.

报错不出现在生成激励阶段,所以说给的代码是可以通过的。报错出现在硬件模型综合阶段,说明综合和代码无法顺利转换,甚至可能是综合策略的选择的问题。换了17.4版本还是会出现这个报错,说明不是版本问题。

看报错信息是类型不匹配,出现在backend程序上。待我细细DEBUG。

Xilinx论坛上其他人也遇到这个问题。有问题,上论坛。官方在打官腔,论坛楼主给出的解决方案如下:

removing the DATA_PACK pragma resolves the problem: as mentioned in some threads, the HLS seemly auto packed AXI-stream struct/parameters; just curious how it worked in older version demo/tutorial.

删除DATA_PACK pragma解决了这个问题:正如在一些线程中提到的,HLS似乎自动打包了轴流结构/参数;只是好奇它在旧版本的演示/教程中是如何工作的。将下图中的#pragma HLS DATA_PACK variable=dout注释掉。

现在至少不会报错了。至于是不是例程想展示的效果就不知道了。

Add IP需要用到右键。

IP integrator将放置自动完成连接所需的几个新块,包括AXI DMA核心、AXI互连和处理器系统重置块。很多时候都是选用默认设置。

做好之后,内层和外层如图所示

暂停

暂停在STEP6的第6小步,启动ZC702板并测试HelloWorld应用程序。 确保板有所有的连接,以允许您下载FPGA设备上的比特流。 请参阅ZC702开发板附带的文档。

总结

在本教程中,您学习了:

如何使用TCL脚本创建Vivado HLS IP。

如何将HLS设计作为IP导入IP integrator。

如何使用AXI4-Lite接口和AXI4-Stream接口将HLS IP连接到Zynq SoC。

如何在软件中使用AXI4-Lite配置HLS IP。

如何在软件中使用AXI4-Stream控制DMA。