写在前面

高层次综合产生的RTL可以封装为IP,并用于DSP的系统生成器(System Generator)。

本教程演示了如何执行此过程,并演示了如何在DSP的系统生成器中使用该设计。

Lab1

使用Vivado HLS生成一个设计,并将该设计打包用于DSP的系统生成器。

然后将HLS IP包含到系统生成器中进行DSP设计并执行RTL仿真。

HLS综合成功界面见上图。

需要用System generator2020.1,因为其他的无法支持MATLABr2020a。打开的界面是MATLAB,没有独自的GUI。而且MATLAB的版本不能太高,比如System generator2020.1无法支持MATLABr2020b。

使用System generator2020.1打开MATLABr2020a的显示界面。

2020.1版本vivado没有对应器件类型。

和18版本不一样,18版HLS和20版VITIS打开都是xc7k420tffg1156-1

在这里改一下,再跑仿真

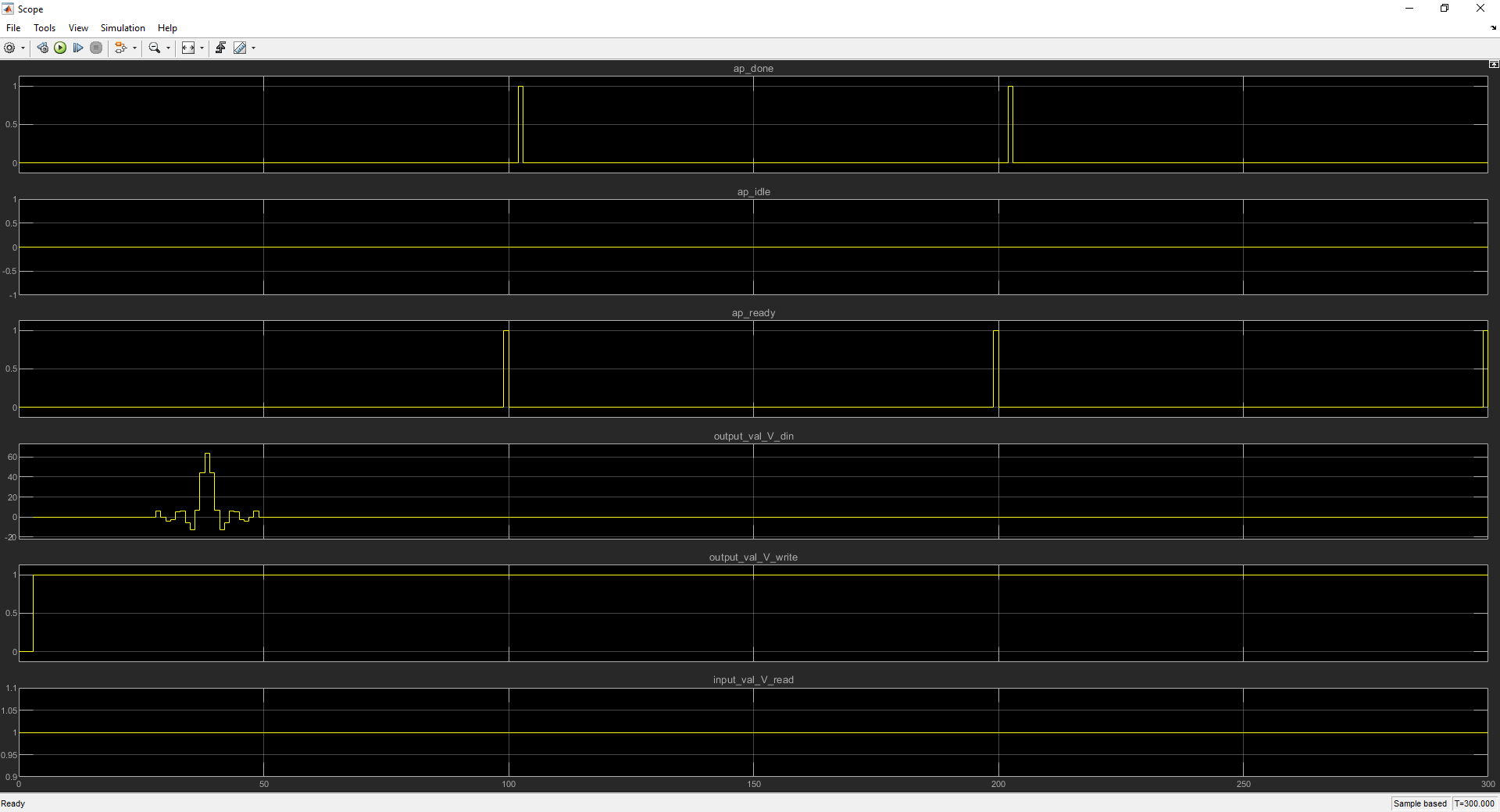

最右边的是scope模块,双击它,波形如下

调整Y轴和X轴范围后,如下

总结

在本教程中,您学习了:

如何使用TCL脚本创建Vivado HLS IP。

如何将HLS设计作为IP导入DSP的系统生成器。