写在前面

高层次综合出来的RTL可以封装成IP,让在更大的设计中使用IP。

老师的问题

Q1什么是front-end,什么是back-end

Q2怎么打开IP Setting

Lab1

为IP目录生成两个HLS块,然后在FFT设计中使用。

使用RTL testbench测试。

front-end前端

back-end后端

这里的前后端是按照数据处理的流程划分的。

前端HLS块将汉明窗口函数应用于1024(N)实数样本,并将偶数/奇数对发送到N/2点XFFT,就像复数一样。

后端HLS块接受位反序数据(bit-reverse ordered),将其按自然顺序排列,并对FFT输出应用O(N)变换来提取N点实数集的频谱数据。 注意,第一输出对将第0和第512(纯实)频谱数据点分别对应到实部和虚部。

这些设计是完全流水线的,用于高吞吐量的流设计;用于连续处理数据,但具有节流能力(如果输入停止,则输出停止)。

使用AXI4-Stream接口连接。

Integrate HLS IP with a Xilinx IP Block

实验涉及合并两个IP模块。

STEP1

编译完后有两个project,分别是fe_vhls_prj和be_vhls_prj

The “front-end” IP archive is located at fe_vhls_prj/IPXACTExport/impl/ip/

The “back-end” IP archive is located at be_vhls_prj/IPXACTExport/impl/ip/

本教程的其余部分展示了如何将VivadoHLS IP块集成到设计中(在IP integrator中)并进行验证

STEP2

STEP3

IP Setting的位置还是没有找到,但是可以从以下方式打开

法一

右键-IP Setting

法二

首先,点击左上方的Setting,图中的齿轮图标

然后,点击左侧的IP,选择Repository

STEP4

在左下方改名

不断连线

忽略报错信息

a.XFFT配置接口没有连接,因为这个设计总是在核心的默认模式下运行。

b.单击OK关闭消息。

STEP5

Verify the Design

选择run all

接下来会显示Vivado的波形仿真界面。

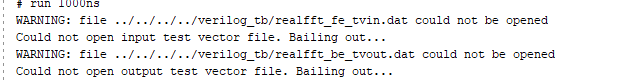

注意,这种打不开之后产生Warning而不是Error。

波形不显示,输入激励打不开。我认为原因是Window中只认绝对路径。

把相对路径改成绝对路径。

而且要小心转义符的问题,把所有“\”改成“/”。总之就是“\”“/”“\”挨个试,总有一个适合你。

下面是正常的仿真结果。

不过,看起来结果不太对,而且代码里还有TODO,损失函数也没有写,是一个未完工的代码。先做到这一步,已经满足本次实验的目的。

补充说明:

正斜杠,又称左斜杠,符号是”/“;反斜杠,也称右斜杠,符号是”\”。

Linux系统

Linux系统中只能使用正斜杠:

在Linux系统中使用反斜杠,路径是不可识别的:

windows系统

1、windows系统中默认使用反斜杠, windows 的第一个字母“W”的第一笔画()去快速的判断使用正斜杠还是反斜杠,”W”的第一笔画是反斜杠,那windows就使用反斜杠

2、同时,在windows系统中,也可以使用正斜杠,访问文件目录

3、但是windows编程中,必须使用转义符来写成如下形式:

F:\Code\Q1Branch

因为在程序代码中,反斜杠是转义字符标志,如果写成“F:\Code\Q1Branch”,那么\C就会被识别为一个字符,同理,\Q也会被识别为 一个字符。

4、在DOS命令中,必须使用反斜杠,使用正斜杠路径是不可识别的

(资料来源于网络)

总结

在本教程中,您学习了:

如何使用TCL脚本创建Vivado HLS IP。

如何使用IP integrator导入创建的设计,并包括Xilinx IP和Vivado IP块。

如何验证IP集成商的设计。