写在前面

RTL验证可以生成波形的trace跟踪文件,用于分析和理解。

RTL验证通常被称为联合仿真或C/RTL联合仿真,因为验证中同时使用C(testbench)和RTL(HLS的RTL输出)。

Lab1

STEP1

有报错。

DUC hardware test PASSED!说明硬件编译通过。

但是Simulation failed: Function ‘main’ returns nonzero value ‘1’.

修改duc_test.c,因为main函数在test文件中。

修改为上面的return,将下面的return注释掉。

修改完如下:

STEP2

Auto会自动选择Verilog。Verilog的仿真用时比较久。

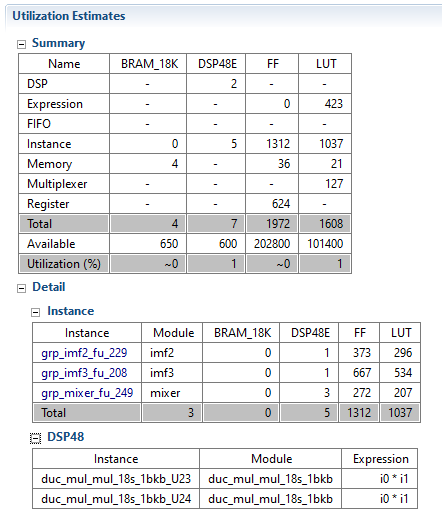

其中Interval比C综合的结果多出1个clock。

RTL simulation分三步:

第一步

C testbench生成输入激励

在此阶段结束时,模拟显示由C测试台生成的任何消息。 在这个阶段,C函数的输出不在C测试台中使用,但测试台输出的任何消息都可以在控制台上看到。

第二步

RTL测试生成,开始RTL仿真。

第三步

RTL仿真的结果传入C testbench比对。

STEP3

修改C Test Bench

证明这东西return 1的时候会报错

Lab2

STEP1

协同仿真,点击右上角的波形图标,会跳转到Vivado并且打开波形。

Lab3

生成波形的trace跟踪文件,用第三方RTL模拟器进行分析。本实验用的是ModelSim。

STEP1

关键要在下拉菜单选modelsim,否则没有*.wlf波形文件。

联调失败

递归引用

To comment this line put ; symbol just before the line as follows

;others = $MODEL_TECH/../modelsim.ini

做以上修改

上图为使用ModelSim+Verilog仿真

总结

本章讲了

对从C合成的设计进行RTL验证,以及测试台在此过程中的重要性。

使用Vivado设计套件创建和打开波形跟踪文件。

使用第三方HDL模拟器(模型Sim)创建和打开波形跟踪文件,并查看RTL验证创建的跟踪文件。