- 灌电流就是上拉电阻输入的电流

- 准双向口输出类型可用作输出和输入功能而不需重新配置口线输出状态。这是因为当IO口线输出为1时驱动能力很弱,允许外部装置将其拉低。当引脚输出为低时,它的驱动能力很强,可吸收相当大的电流。(准双向口有3个上拉晶体管适应不同的需要)准双向口读外部状态前,要先锁存为 „1‟,才可读到外部正确的状态。

- 灌电流能力强,拉电流能力弱

- 读IO口状态的原则是非高即低,只能准确识别外部的低电平信号,无法区分悬空和真正的高电平

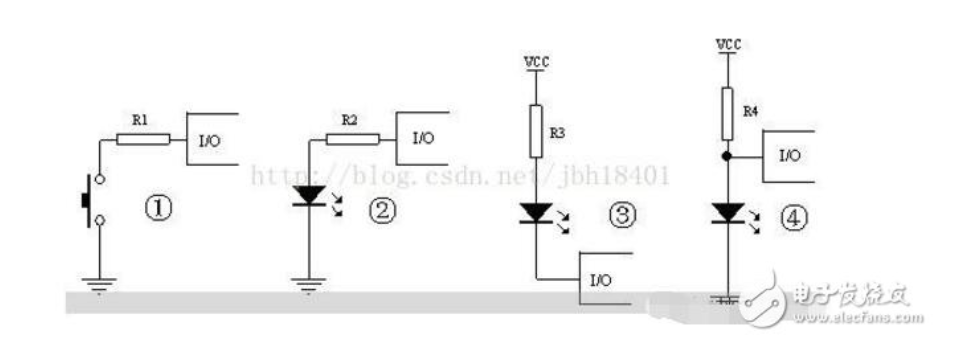

准双向口用作输入时,可对地接按键,如图1,当然也可以去掉R1直接接按键,当按键闭合时,端口被拉至低电平,当按键松开时,端口被内部“极弱上拉”晶体管拉至高电平。

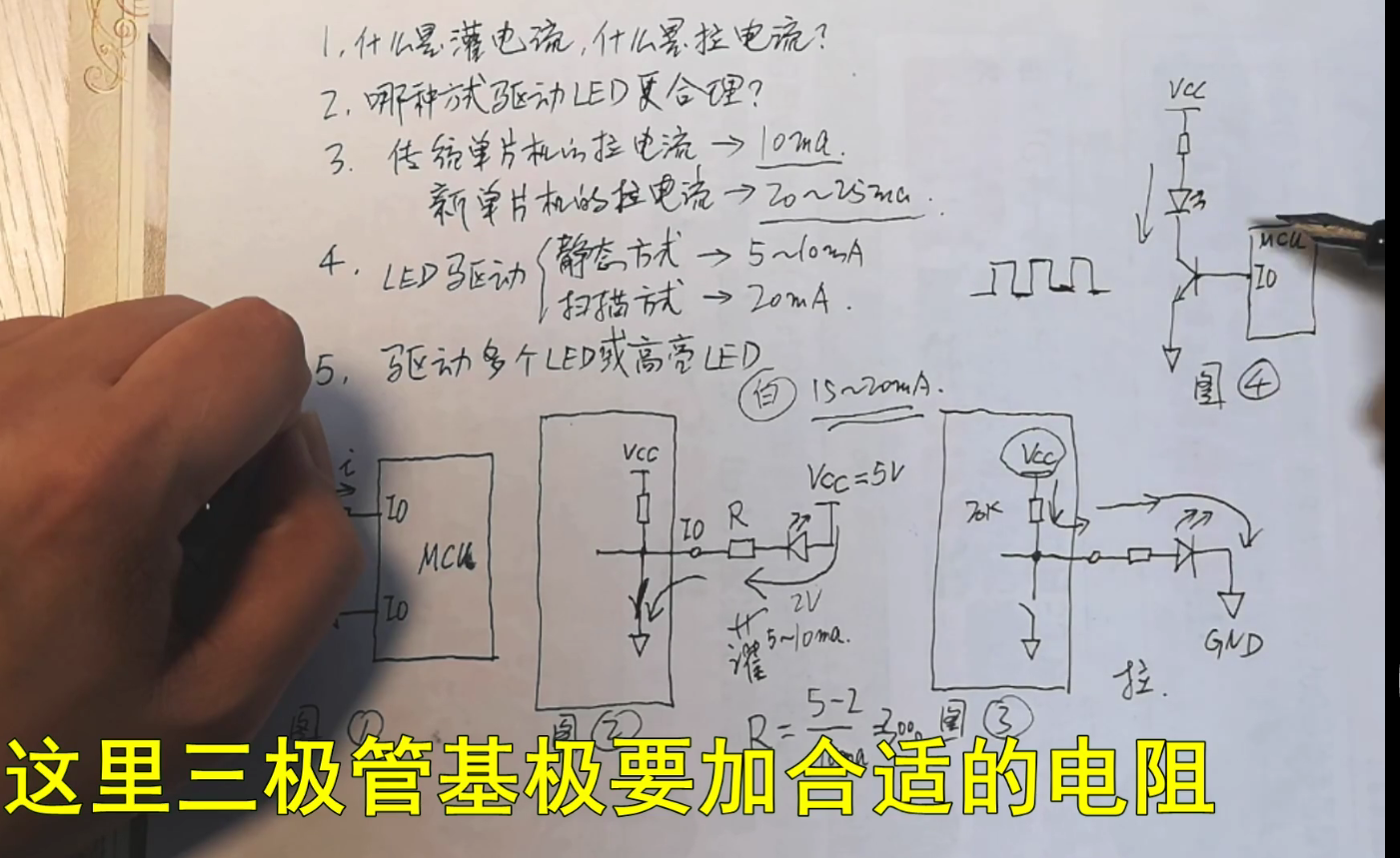

- 当端口作为输出时,不应对地外接LED如图2控制,这样端口的驱动能力很弱(拉电流能力弱),LED只能发很微弱的光,如果要驱动LED,要采用图3的方法,这样准双向口在输出为低时,可吸收20mA的电流(灌电流能力强),故能驱动LED。图4的方法也可以,不过LED不发光时,端口要吸收很大电流。

- 个人理解:端口输出电流很弱, 但如果由外部提供电流时端口可以吸收外部的电流,使得电路的电流相对较大

问:单片机除P0口外,其他输出都是5V吧?那么用来驱动数码管为什么还需要加三极管驱动?比方说加100欧的电阻,那么电流就高达5V/100欧=50mA,而数码管才20mA?再者三极管怎么都没标明电流放大倍数? 答:这个类似于电源的内阻。输出电流越大,消耗在内部的电压压降就越大。输出电压=5V-内部压降。 51单片机的上拉管典型阻值20k,若外部开路,在内部的压降=0,输出就是5V,如果IO接个5k电阻到GND,那么外部电阻的电压=5V÷(5+20)&TImes;5=1V,而外部5K电阻上的电流才1V/5k=200uA。 所以你接100欧的电阻,IO的输出电压更本就很小了,根本达不到5V÷100欧=50mA的水平, 一般来说高电平输出能力也就100-200uA,低电平输出能力8mA-10mA (AT89C2051等IO已强化,可吸入20mA电流)。这么小的电流驱动数码管,你就自己看吧,所以才加三极管驱动。数码管20mA的电流一般是偏大的,静态显示时,一般选5-15mA即可。动态显示可适当加大至20mA左右,不然亮度偏低。 一般三级管的静态放大值取100就可以估算。比如驱动一个5V(额定电压)线圈继电器。线圈内阻是120欧,估算驱动电流有5V/120欧=40mA,单片机一般只能输出10mA,驱动不了。那么靠三极管驱动,基极驱动电流=40mA/100=400uA》200uA, 若使用PNP型三极管,则使用低电平驱动,基极电阻=(5-0.7)V÷0.4mA=10k, 若使用NPN型三极管,则使用高电平驱动,如上面所说,输出能力最多200uA,达不到400uA,要使用上拉电阻产生至少200uA电流,上拉电阻=(5-0.7)V/0.2mA=21.5k这些计算值都是临界值,要保险点就在这个值的基础上稍微选小一点就好。

https://www.bilibili.com/video/av837582130/

- 浮空输入的时候,你想输入大电流都难。浮空输入,内阻比较大,你得很高的电压,这样可能会超过芯片上限

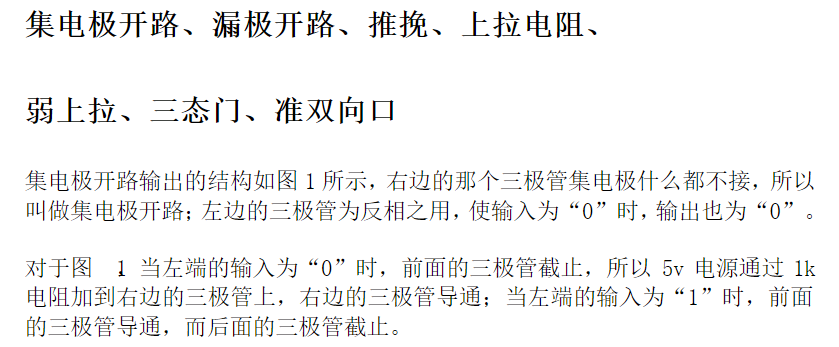

推挽输出

- 可以输出高,低电平,连接数字器件; 推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止。高低电平由IC的电源决定。

- 推挽电路是两个参数相同的三极管或MOSFET,以推挽方式存在于电路中,各负责正负半周的波形放大任务,电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小、效率高。输出既可以向负载灌电流,也可以从负载抽取电流。推拉式输出级既提高电路的负载能力,又提高开关速度。

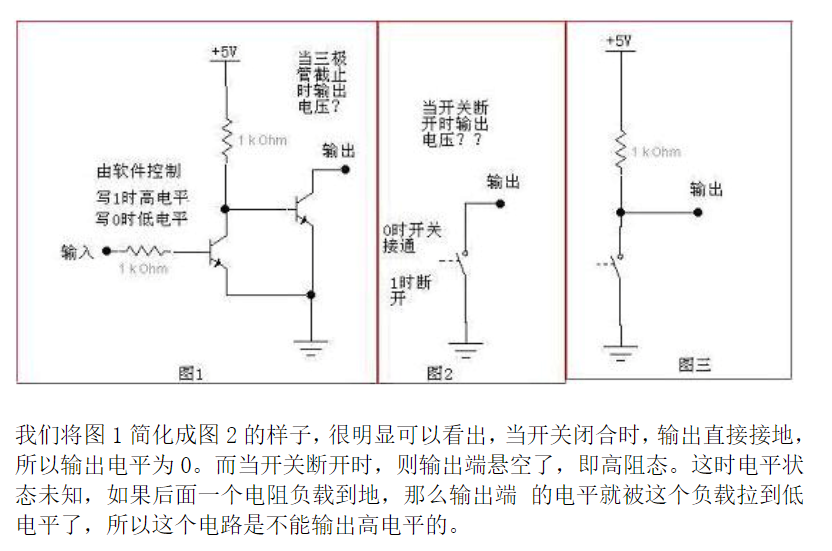

开漏输出

- 输出端相当于三极管的集电极,要得到高电平状态需要上拉电阻才行。适合于做电流型的驱动,其吸收电流的能力相对强(一般20mA以内)

开漏形式的电路有以下几个特点:

1、利用外部电路的驱动能力,减少IC内部的驱动。当IC内部MOSFET导通时,驱动电流是从外部的VCC流经上拉电阻、MOSFET到GND。IC内部仅需很小的栅极驱动电流。

2、一般来说,开漏是用来连接不同电平的器件,匹配电平用的,因为开漏引脚不连接外部的上拉电阻时,只能输出低电平,如果需要同时具备输出高电平的功能,则需要接上拉电阻,很好的一个优点是通过改变上拉电源的电压,便可以改变传输电平。比如加上上拉电阻就可以提供TTL/CMOS电平输出等。(上拉电阻的阻值决定了逻辑电平转换的速度。阻值越大,速度越低功耗越小,所以负载电阻的选择要兼顾功耗和速度。)

3、开漏输出提供了灵活的输出方式,但是也有其弱点,就是带来上升沿的延时。因为上升沿是通过外接上拉无源电阻对负载充电,所以当电阻选择小时延时就小,但功耗大;反之延时大功耗小。所以如果对延时有要求,则建议用下降沿输出。

4、可以将多个开漏输出连接到一条线上。通过一只上拉电阻,在不增加任何器件的情况下,形成“与逻辑”关系,即“线与”。可以简单的理解为:在所有引脚连在一起时,外接一上拉电阻,如果有一个引脚输出为逻辑0,相当于接地,与之并联的回路“相当于被一根导线短路”,所以外电路逻辑电平便为0,只有都为高电平时,与的结果才为逻辑1。

处理器IO口的电流一般小于10mA,假设为5mA,选择三极管的参数很重要,若题主选择的是最大电流为600mA,而放大倍数β为10的三极管,以为电机只需500mA电流,可以满足要求,这种想法是错误的。IO口的电流为5mA,大倍数β为10,那么放大后的电流最大为50mA,明显不够。这种情况必须选用放大倍数大于100倍,最大工作电流大于500mA的三极管,而且电路设计时要降额设计。

若电流较大,找不到合适的三极管怎么办?

(1)使用达林顿晶体管,达林顿晶体管的放大倍数一般大于1000倍,大部分情况能够满足要求。

(2)使用多个三极管组成复合管,放大倍数可达β=β1β2β3…,即最高放大倍数可为几个三极管的放大倍数的乘积。

(3)使用三极管驱动大功率MOS管。

IO口常识:https://wenku.baidu.com/view/c24b3436eefdc8d376ee3274.html

[

](https://wenku.baidu.com/view/5ad2f8dfc381e53a580216fc700abb68a882ad17.html)