- ARM芯片是RISC指令集芯片,CPU对内存/外设寄存器都只有读/写两个操作,所有的计算都在CPU内部完成;那么CPU从内存中得到的值保存在CPU内部的哪里呢?

- 无论是M3/M4系列还是A7系列ARM芯片,CPU内部有R0-R15总共16个寄存器(一般称为通用寄存器)

- CPU内部寄存器和外设寄存器是不一样的;内部寄存器是CPU可以直接访问到的(可以由指令直接读/写),不需要对外发出地址;

R13/R14/R15三个寄存器一般用作特殊用途,R13=SP R14=LR R15=PC

R13:别名SP(Stack Pointer),栈指针 R14:别名LR(Link Register),用来保存返回地址 R15:别名PC(Program Counter),程序计数器,

表示当前指令地址,写入新值即可跳转

M3/M4系列CPU内部通用寄存器

- 可以明显看到,M3/M4系列的R13(SP)实际上有两个实体:SP_process、SP_main

- 在汇编中使用sp时,可能使用的是主栈寄存器SP_main,也可能用的是SP_process;在不同的设置下,sp寄存器会对应不同的实体

- 一般使用SP_main,运行RTOS时才会用到SP_process

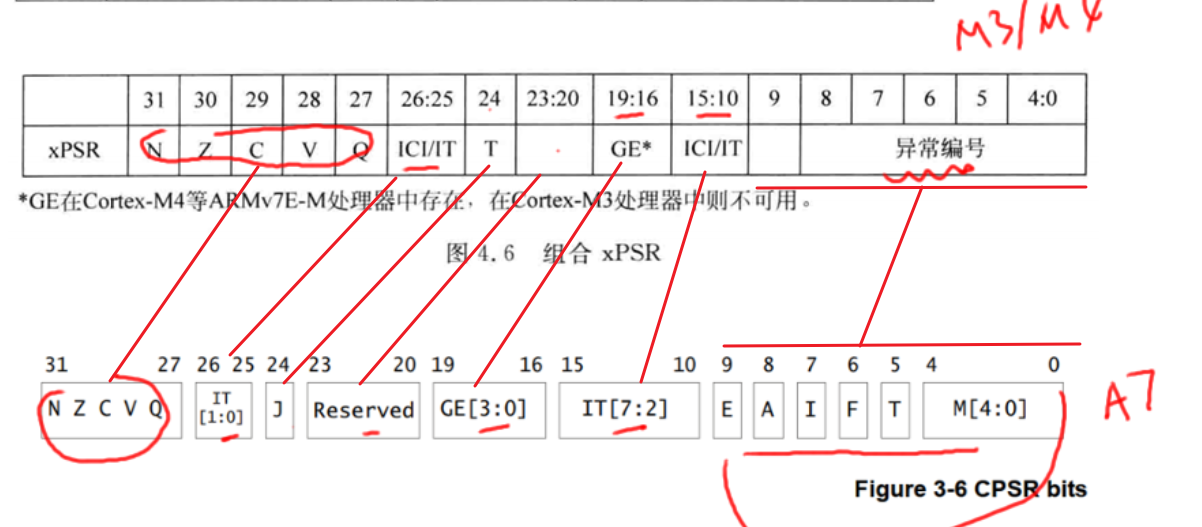

- 对于M3/M4来说,除了R0-R15这16个寄存器外,还有xPSR(program status register)程序状态寄存器;用来保存某些状态值

- 对于cortex-M3/M4来说,xPSR实际上对应3个寄存器:

①APSR:Application PSR,应用PSR

②IPSR:Interrupt PSR,中断PSR

③EPSR:Exectution PSR,执行PSR

- 这三个程序状态寄存器的位bit是错开的

- 因此可以组合得到xPSR(一次可以访问三个状态寄存器)

- 所以M3/M4的程序状态寄存器的访问就有两种方式

可以单独访问: MRS R0, APSR ;读APSR

MRS R0, IPSR ;读IPSR

MSR APSR, R0 ;写APSR

也可以一次性访问:

MRS R0, PSR ; 读组合程序状态

MSR PSR, R0 ; 写组合程序状态 !!!: mrs(move移动 register一般寄存器 status状态寄存器) 把状态寄存器的值移动到一般寄存器中

- 程序状态寄存器各bit的含义

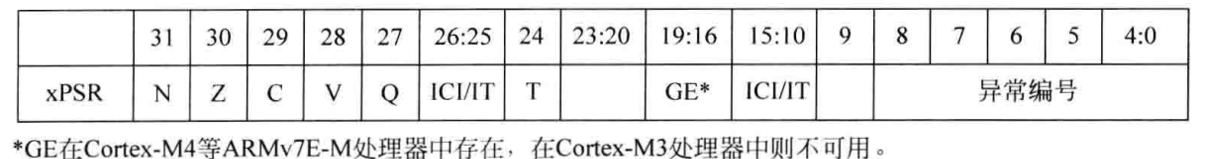

- cortex-A7系列CPU内部通用寄存器

- 对于A7来说,除了R0-R15外,还有CPSR状态寄存器(current program status register)

- 对于A7架构的CPU来说,有多种工作模式:user用户模式/sys系统模式/fiq快中断模式/irq中断模式/abt/svc/und未定义模式/hyp

- 一般把user模式和sys模式外的7中模式统称为异常模式,这些模式下都会有自己的对应的某些寄存器,有自己用的SPSR备份程序状态寄存器

- A7的CPSR和M3/M4的xPSR的位和含义都是类似的,只在异常编号中有差别