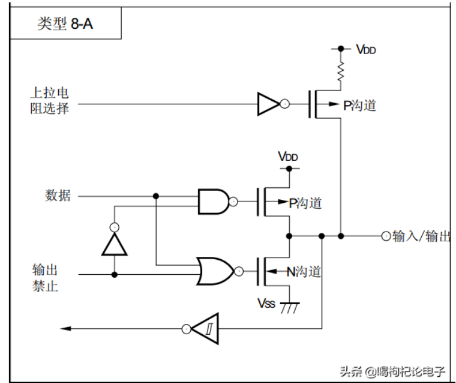

NMOS是栅极高电平(|VGS| > Vt)导通,低电平断开,可用来控制与地之间的导通。 PMOS是栅极低电平(|VGS| > Vt)导通,高电平断开,可用来控制与电源之间的导通。

NMOS因Source端一般接地(低电位),所以要让|VGS| > Vt, 则Gate端一般要接正电压,这样管子才能导通;

PMOS因Source端一般接VDD(高电平),所以要让|VGS|>Vt,则Gate端一般要接负电压(低与VDD的电压),这样管子才能导通。 ———————————————— 版权声明:本文为CSDN博主「Phenixyf」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。 原文链接:https://blog.csdn.net/phenixyf/article/details/45741959

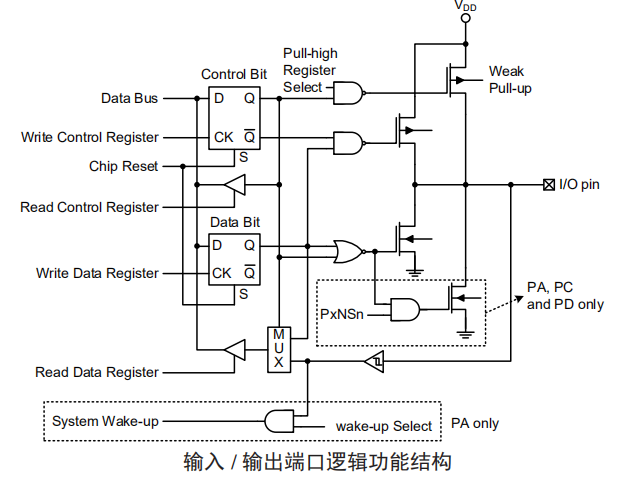

合泰单片机端口逻辑功能结构图

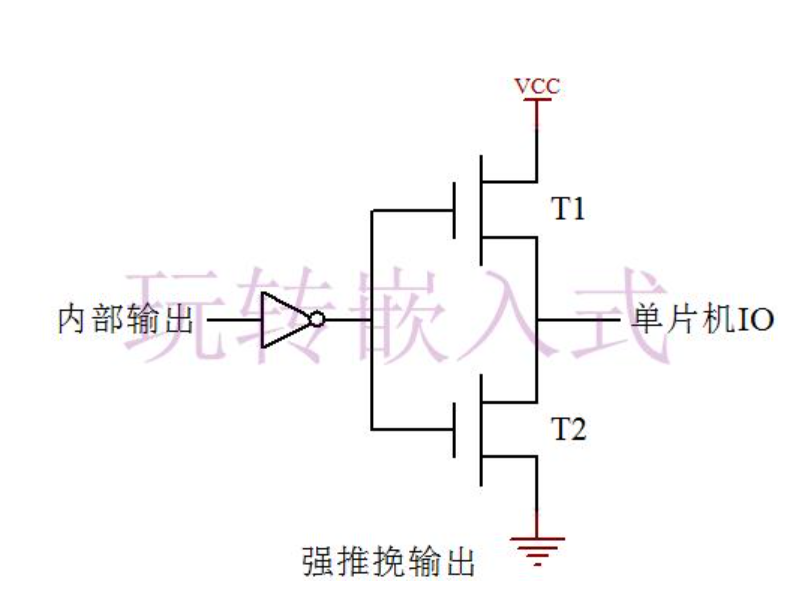

推挽输出时IO口能通过内部上下MOS管开关切换能输出高低电平,高阻态输入时,IO口内部上下MOS管都关闭,IO口工作在高阻态的输入模式下,那么高阻态是个什么样的概念呢?下图是常见的IO的内部框图。

- 如果我们将IO口的输入状态设置为高阻状态,且没有外接上下拉电阻,内部的两个上下MOS管都是断开的,对外部呈现高阻态

- 合泰单片机设置为高阻输入配置分析:

- 高阻输入:

{pac1=1; pa1=1;papu1=0;} - 输出低电平:

{pac1=0; paq=0; papu1=0;}

NMOS管的主回路电流方向为D→S,导通条件为VGS有一定的压差,一般为5~10V(G电位比S电位高);而PMOS管的主回路电流方向为S→D,导通条件为VGS有一定的压差,一般为-5~-10V(S电位比G电位高)

推挽电路是由两个三极管或MOSFET,以推挽方式存在于电路中,电路工作时,两只对称的开关管每次只有一个导通,所以导通损耗小、效率高、既提高电路的负载能力,又提高开关速度。

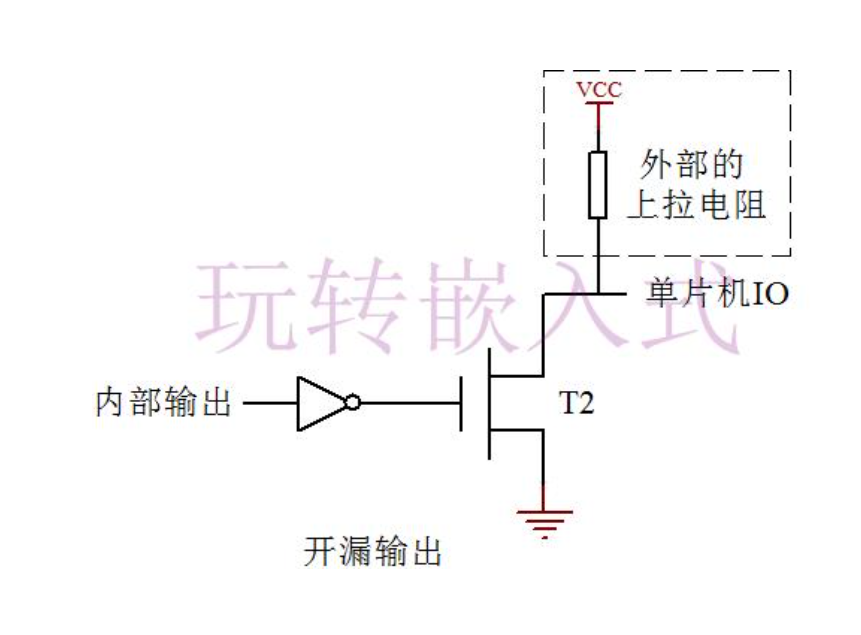

开漏输出只能输出低电平,如果要输出高电平必须通过上拉电阻才能实现。就类似于三极管的集电极输出。

内部输出1时MOS管截止,输出与地断开,这时候IO口其实是没有驱动能力的,需要外部连接上拉电阻才能输出高电平,才能驱动数字器件;

内部输出0时MOS管导通,输出低电平,所以开漏能输出低电平;