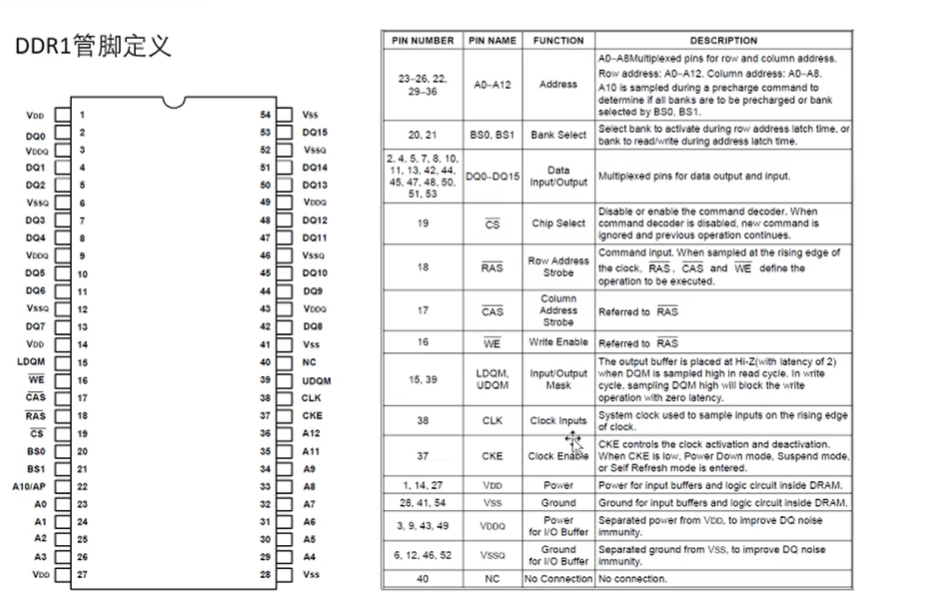

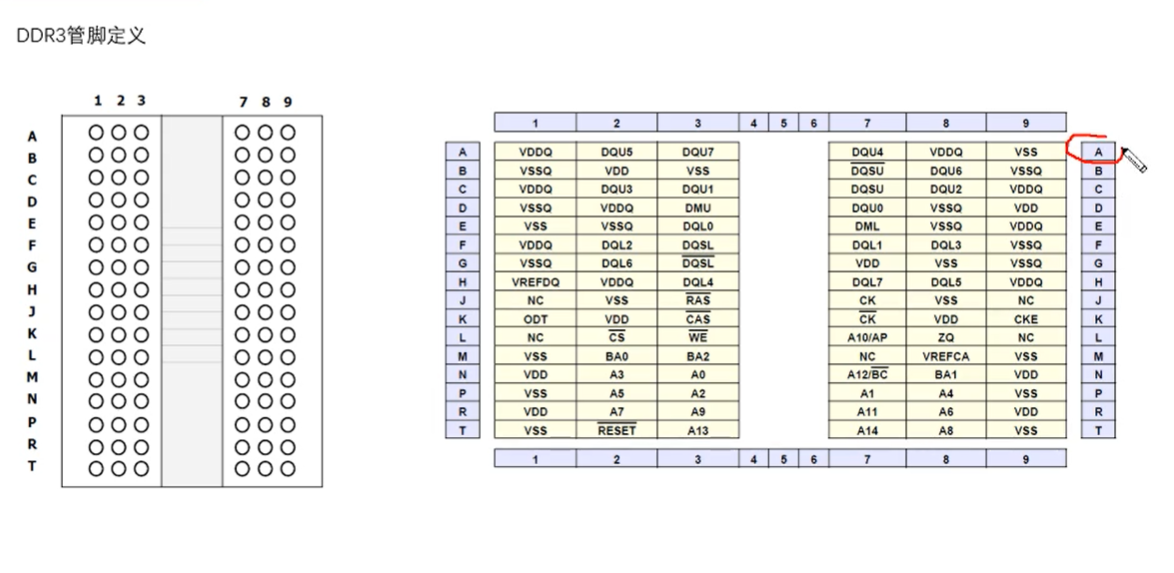

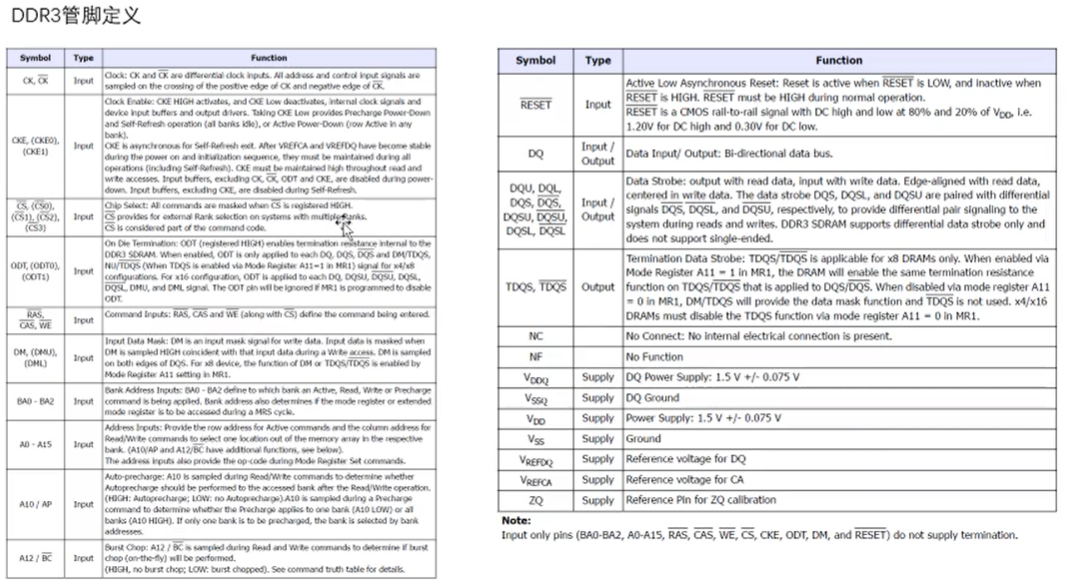

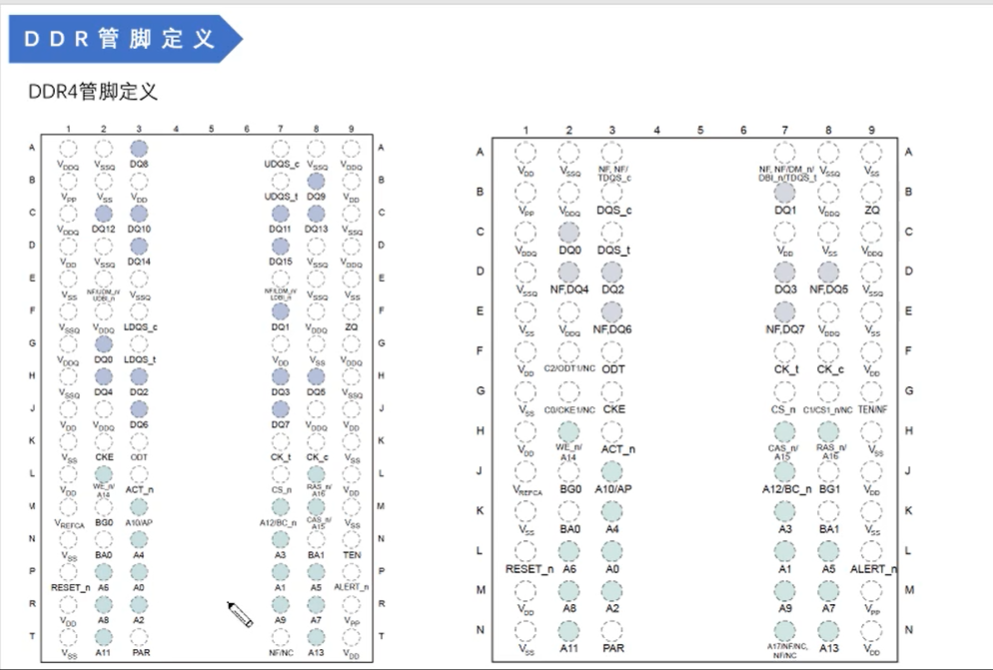

01 DDR1\2\3\4\5管脚定义

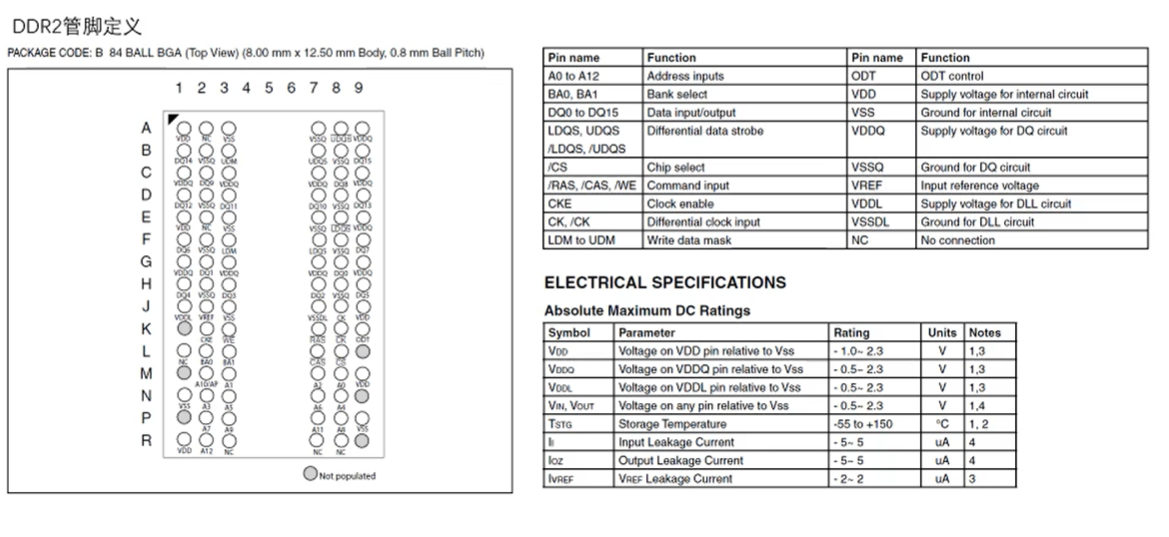

JEDEC标准

DDR1

DDR2

DDR3

DDR4

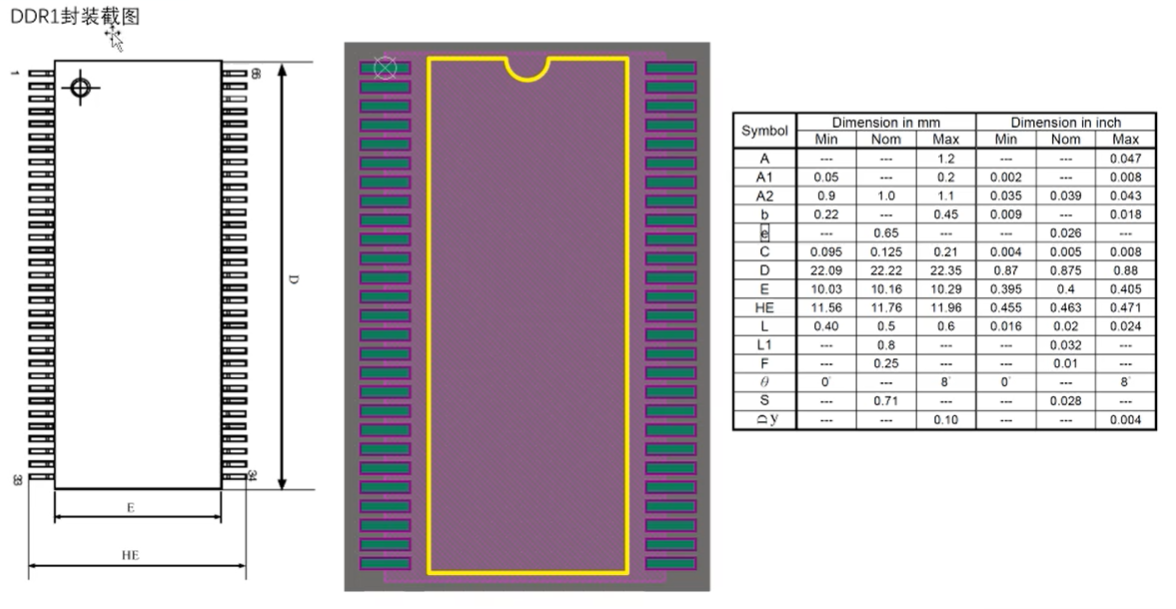

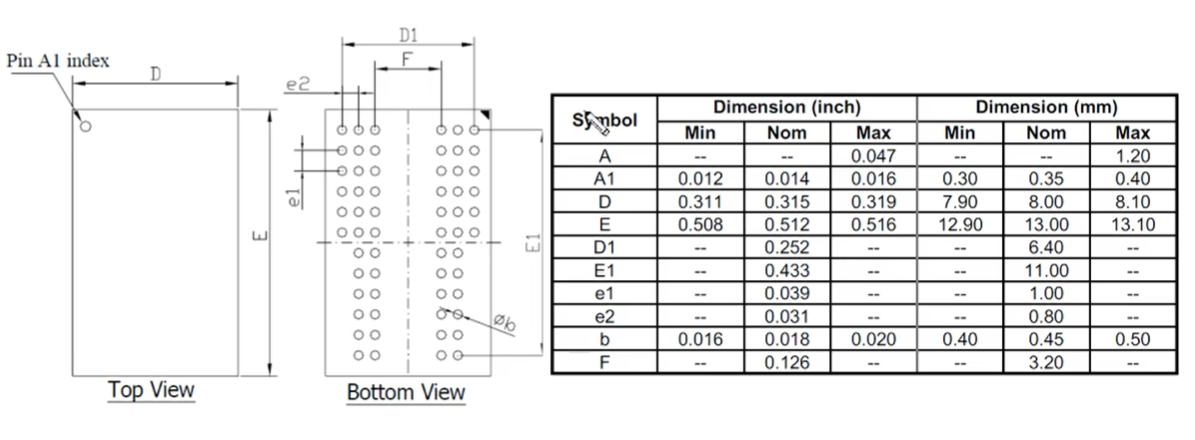

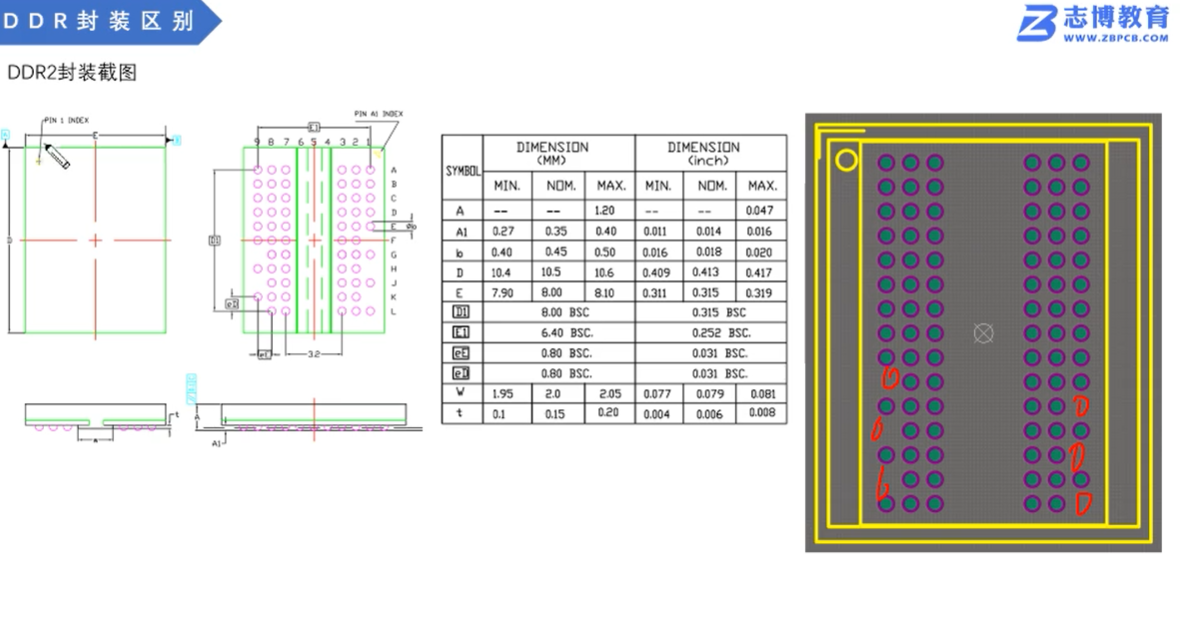

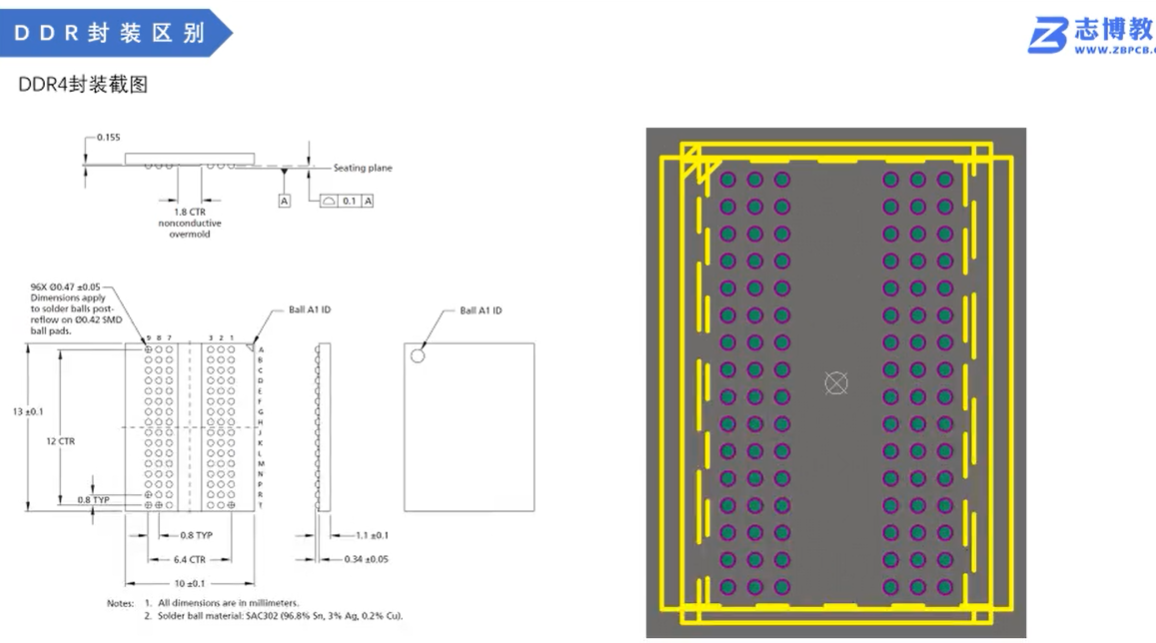

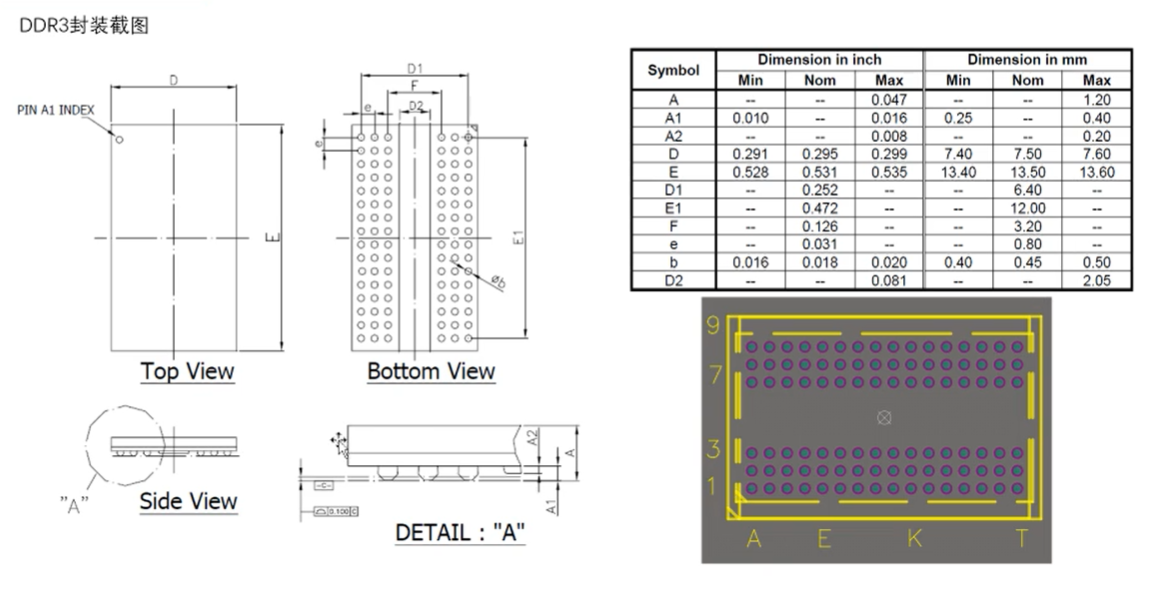

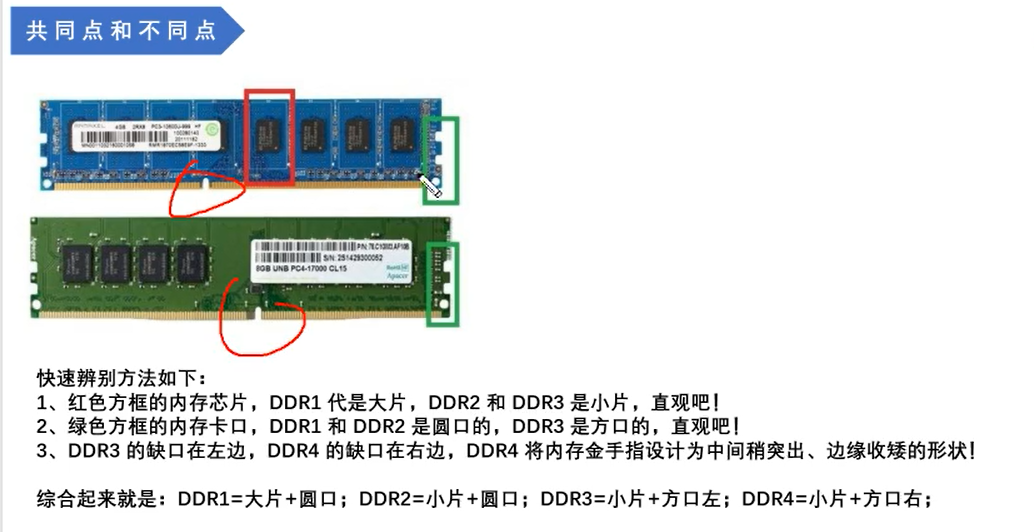

02 DDR1\2\3\4\5封装区别

DDR1

DDR2

DDR3

DDR4

DDR5

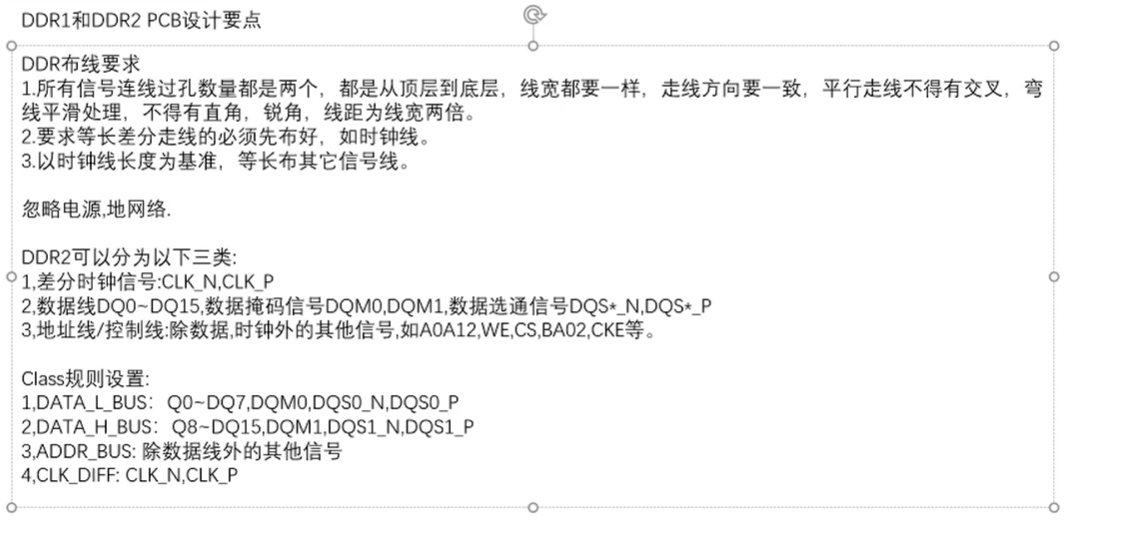

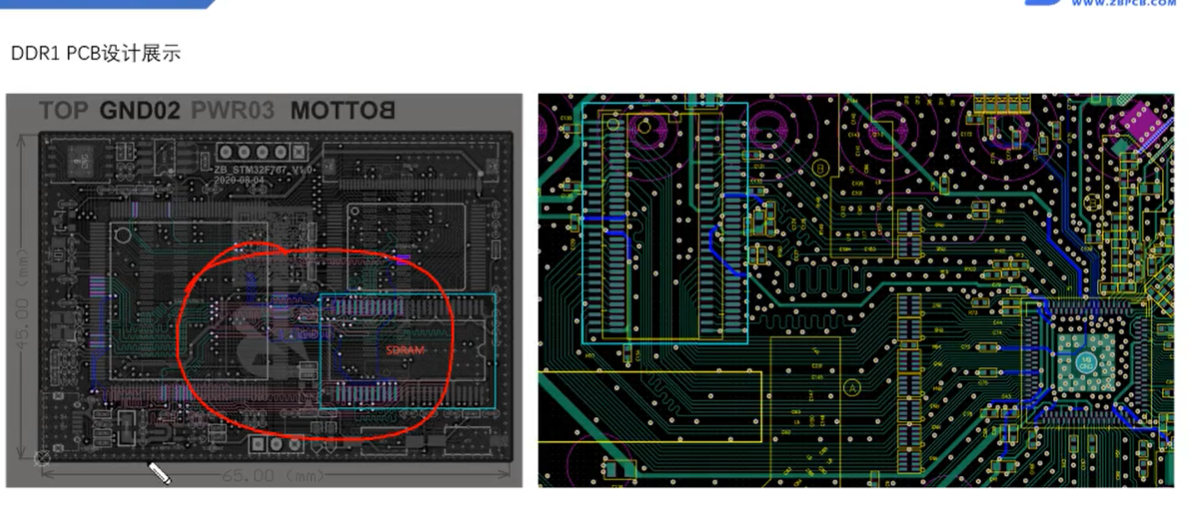

03 DDR高速PCB设计要点讲解1

Class 分类:(D-C)

note:

与时钟线等长要求

数据线: 5-10mil

地址线:10 - 50mil

DDR走线区域不能有其他信号线

电源走线至少10-20mil

拓扑结构:对于地址线

点对点:直连

整组等长

T型:从中间分开

菊花链:串接

先难后易,先走地址线,再数据线

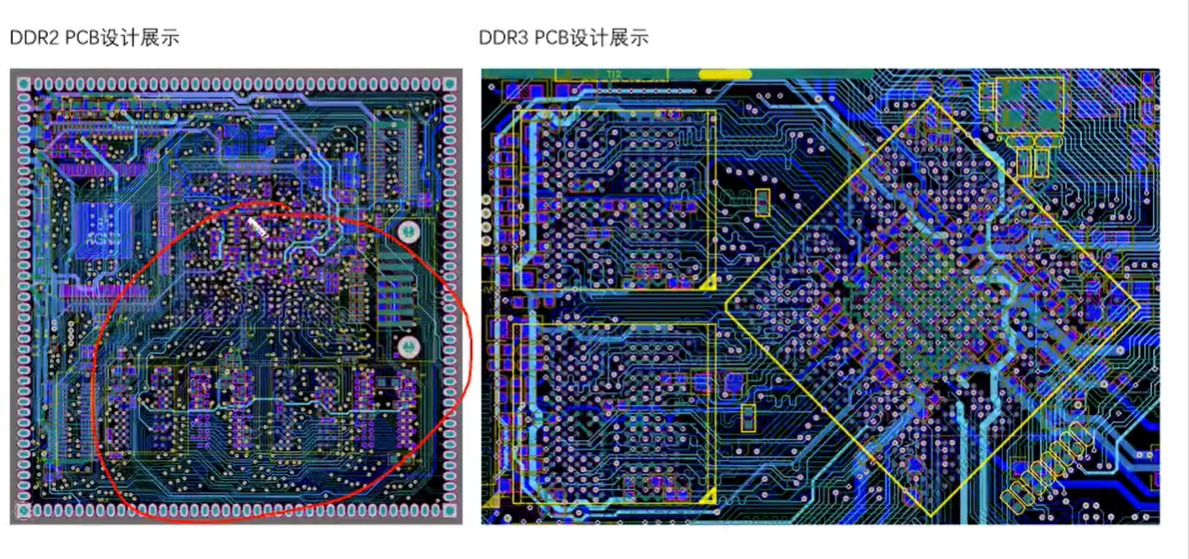

04 DDR高速PCB设计要点讲解2

一般FPGA需要做端接

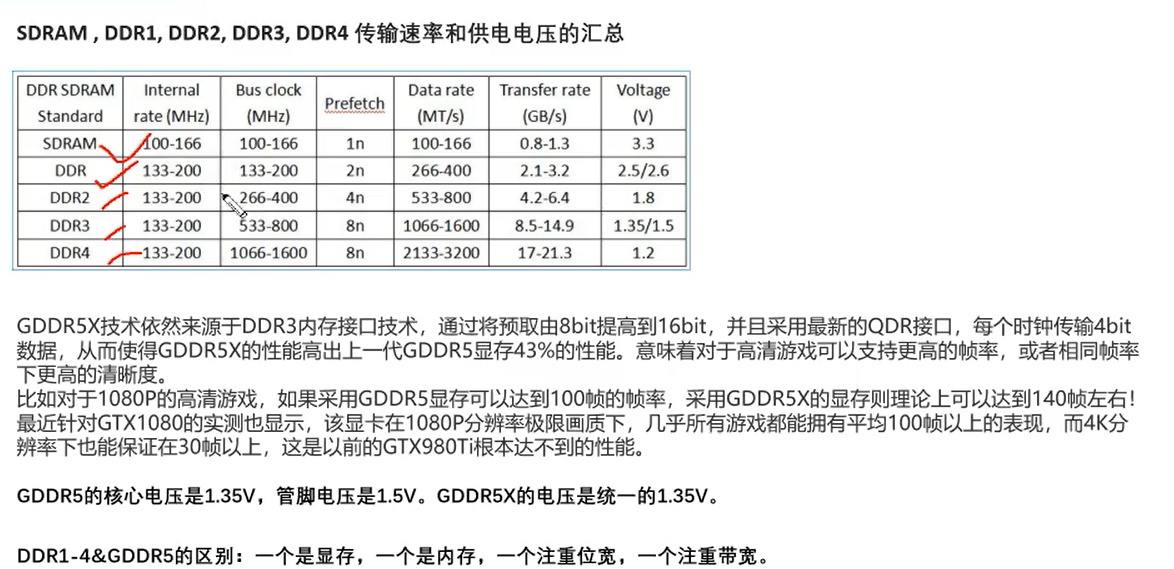

DDR发展趋势:电压越来越低,速度越来越高

1/2CU^2

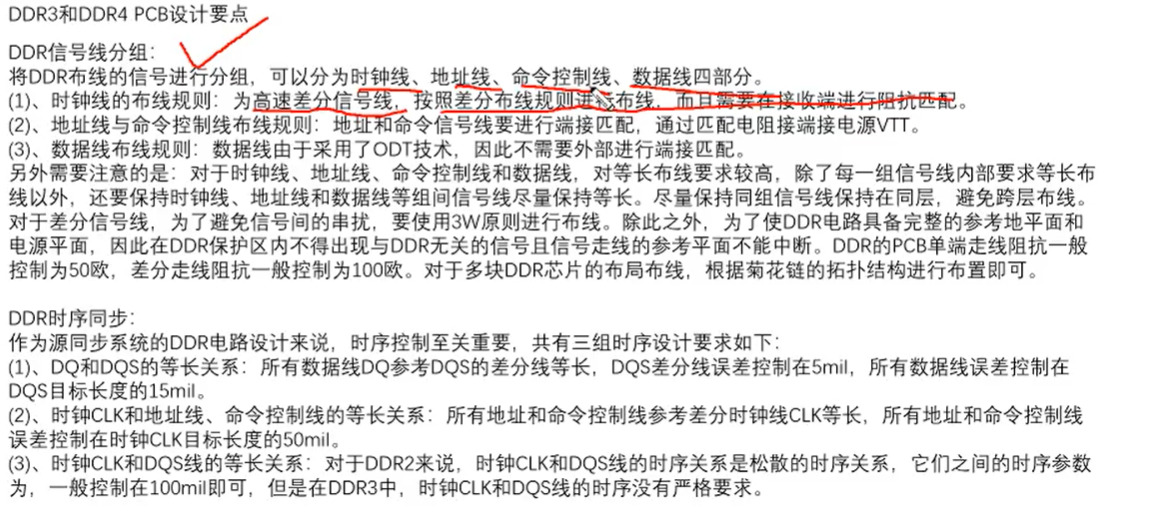

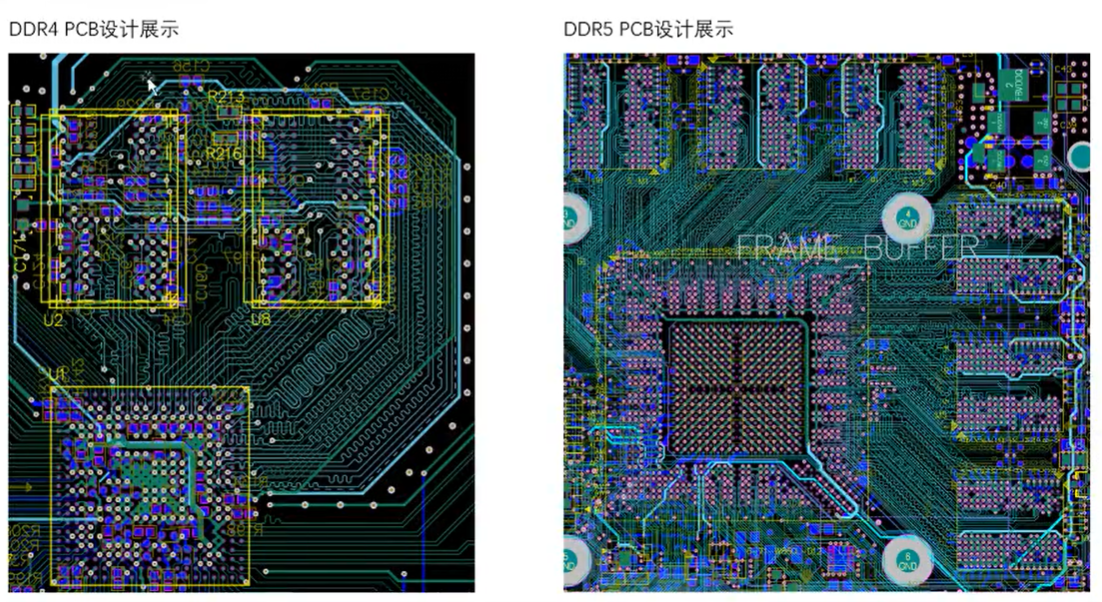

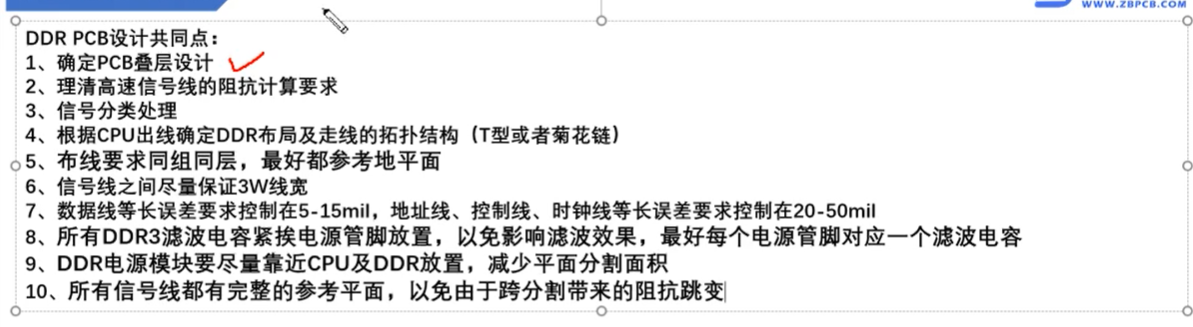

05DDR PCB设计共同点和不同点

相同点:

note:

单端50、差分100

中间出线-T型拓扑,旁边出线-菊花链

不同点:

06 答疑:

- 画PCB时不要轻易用X、Y进行镜像

- DDR4 LPDDR4 DDR4L

LP 一般是 lower power 低功耗

L 可能是Low voltage 低压意思

- 过孔最好比厂家最小工艺高点,保证良品率。

- 平面无法连续,在分割处放电容