I2C 通讯协议(Inter-Integrated Circuit)是由Phiilps 公司开发的(Now it is NXP),由于它引脚少,硬件实现简单,可扩展性强,不需要USART、CAN 等通讯协议的外部收发设备,现在被广泛地使用在系统内多个集成电路(IC)间的通讯。

一、I2C协议介绍

(一)I2C物理层

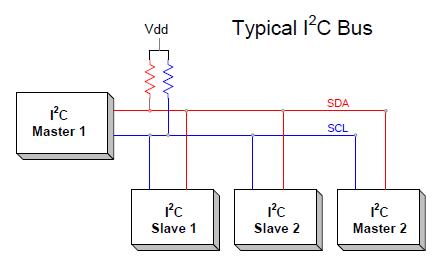

I2C 通讯设备之间的常用连接方式见下图

常见通信系统

物理层特点:

它是一个支持多设备的总线。“总线”指多个设备共用的信号线。在一个I2C 通讯总线中,可连接多个I2C 通讯设备,支持多个通讯主机及多个通讯从机,但在同一时间内,只能一个主节点使用总线。

一个I2C 总线只使用两条总线线路,一条双向串行数据线(SDA) ,一条串行时钟线(SCL)。数据线即用来表示数据,时钟线用于数据收发同步。

每个连接到总线的设备都有一个独立的地址,主机可以利用这个地址进行不同设备之间的访问。Each I2C slave device needs an address which must still be obtained from the NXP.

总线通过上拉电阻接到电源。当I2C 设备空闲时,会输出高阻态,而当所有设备都空闲,都输出高阻态时,由上拉电阻把总线拉成高电平。

多个主机同时使用总线时,为了防止数据冲突,会利用仲裁方式决定由哪个设备占用总线。

主从、收发不平衡,主机主动进行寻址,主机主动收或主机主动发,主机主动停止

具有三种传输模式:标准模式传输速率为100kbit/s(项目中所用) ,快速模式为400kbit/s ,高速模式下可达 3.4Mbit/s,但目前大多I2C 设备尚不支持高速模式。

连接到相同总线的 IC 数量受到总线的最大电容 400pF 限制 ,从节点数目取决于传输介质的电容,通常不超过20或30个从节点。

(二)I2C协议层

I2C 的协议定义了通讯的起始和停止信号、数据有效性、响应、仲裁、时钟同步和地址广播等环节。

1、I2C基本读写过程

基本通信过程

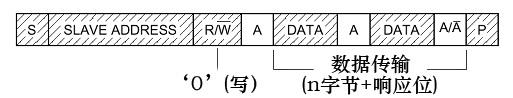

主机写数据到从机

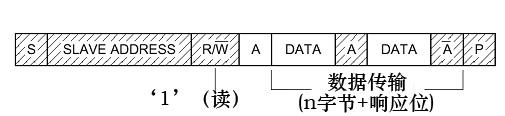

主机由从机中读取数据

I2C复合通信格式

S : 传输开始信号 SLAVE_ADDRESS: 从机地址

R/W: 传输方向选择位,1 为读,0 为写 A/A: 应答(ACK)或非应答(NACK)信号

P : 停止传输信号

其中S 表示由主机的I2C 接口产生的传输起始信号(S),这时连接到I2C 总线上的所有从机都会接收到这个信号。

起始信号产生后,所有从机就开始等待主机紧接下来广播的从机地址信号(SLAVE_ADDRESS)。在I2C 总线上,每个设备的地址都是唯一的,当主机广播的地址与某个设备地址相同时,这个设备就被选中了,没被选中的设备将会忽略之后的数据信号。根据I2C 协议,这个从机地址可以是7 位或10 位。

在地址位之后,是传输方向的选择位,该位为0 时,数据传输方向是由主机传输至从机,即主机向从机写数据。该位为1 时,主机由从机读数据。

从机接收到匹配的地址后,主机或从机会返回一个应答(ACK)或非应答(NACK)信号,只有接收到应答信号后,主机才能继续发送或接收数据。

若配置的方向传输位为“写数据”方向,即第一幅图的情况,广播完地址,接收到应答信号后,主机开始正式向从机传输数据(DATA),数据包的大小为8 位,主机每发送完一个字节数据,都要等待从机的应答信号(ACK),重复这个过程,可以向从机传输N 个数据,这个N 没有大小限制。当数据传输结束时,主机向从机发送一个停止传输信号(P),表示不再传输数据。

若配置的方向传输位为“读数据”方向,即第二幅图的情况,广播完地址,接收到应答信号后,从机开始向主机返回数据(DATA),数据包大小也为8 位,从机每发送完一个数据,都会等待主机的应答信号(ACK),重复这个过程,可以返回N 个数据,这个N 也没有大小限制。当主机希望停止接收数据时,就向从机返回一个非应答信号(NACK),则从机自动停止数据传输。

除了基本的读写,I2C 通讯更常用的是复合格式,即第三幅图的情况,该传输过程有两次起始信号(S)。一般在第一次传输中,主机通过 SLAVE_ADDRESS 寻找到从设备后,发送一段“数据”,这段数据通常用于表示从设备内部的寄存器或存储器地址(注意区分它与SLAVE_ADDRESS 的区别);在第二次的传输中,对该地址的内容进行读或写。也就是说,第一次通讯是告诉从机读写地址,第二次则是读写的实际内容。

下面详细介绍I2C通信过程(可以参考PCA9555DataSheet)

C133183_PCA9555DB(IO扩展芯片).pdf

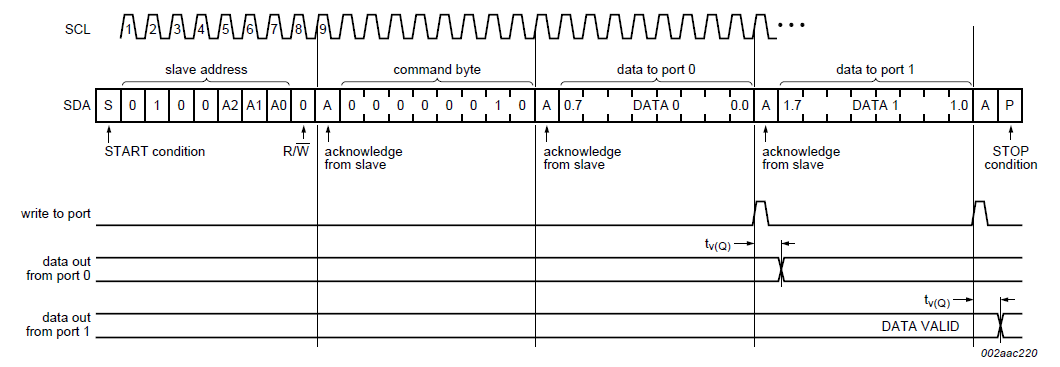

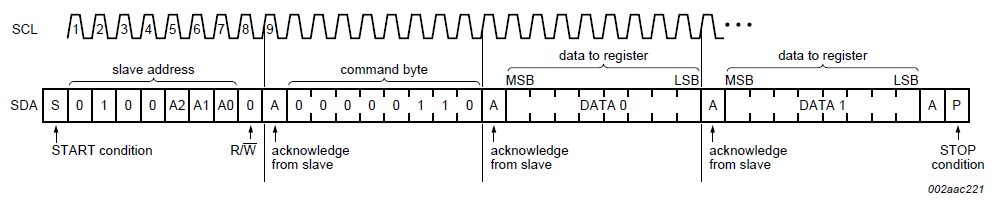

(1)Writing to the port registers

Data is transmitted to the PCA9555 by sending the device address and setting the least significant bit to a logic 0 . The command byte is sent after the address and determines which register will receive the data following the command byte.

The eight registers within the PCA9555 are configured to operate as four register pairs. The four pairs are Input Ports, Output Ports, Polarity Inversion Ports, and Configuration Ports. After sending data to one register, the next data byte will be sent to the other register in the pair. For example, if the first byte is sent to Output Port 1 (register 3), then the next byte will be stored in Output Port 0 (register 2).

There is no limitation on the number of data bytes sent in one write transmission. In this way, each 8-bit register may be updated independently of the other registers.

Write to Output port registers

Write to Configuration registers

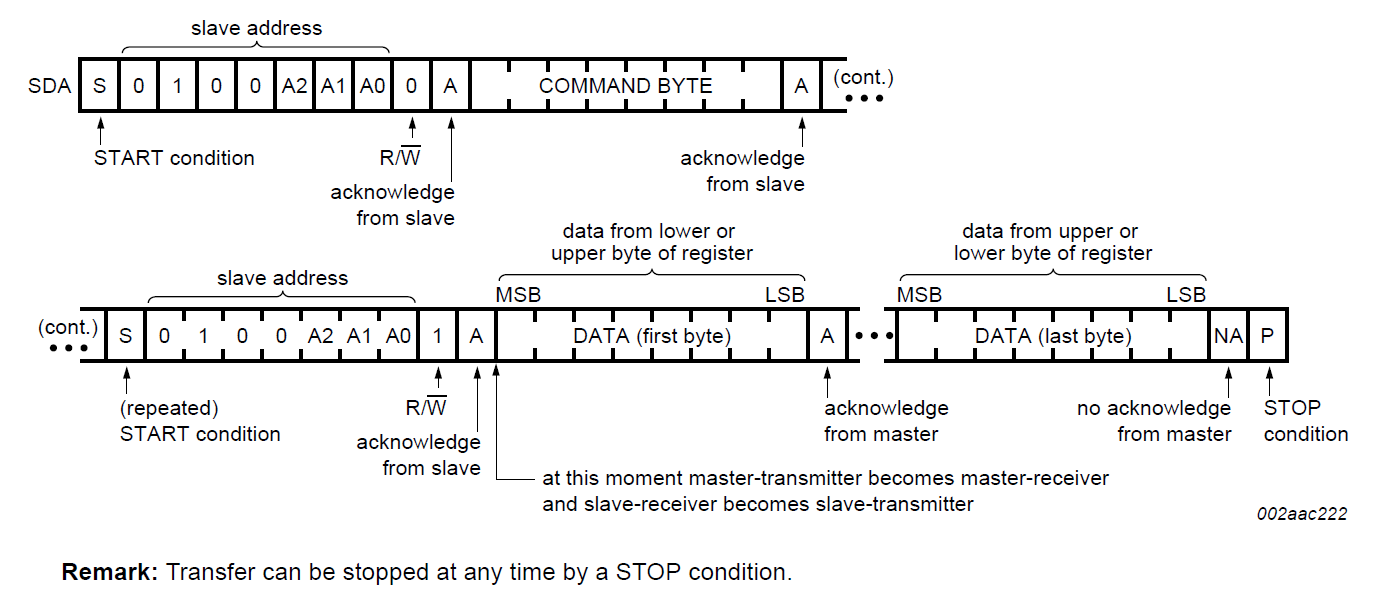

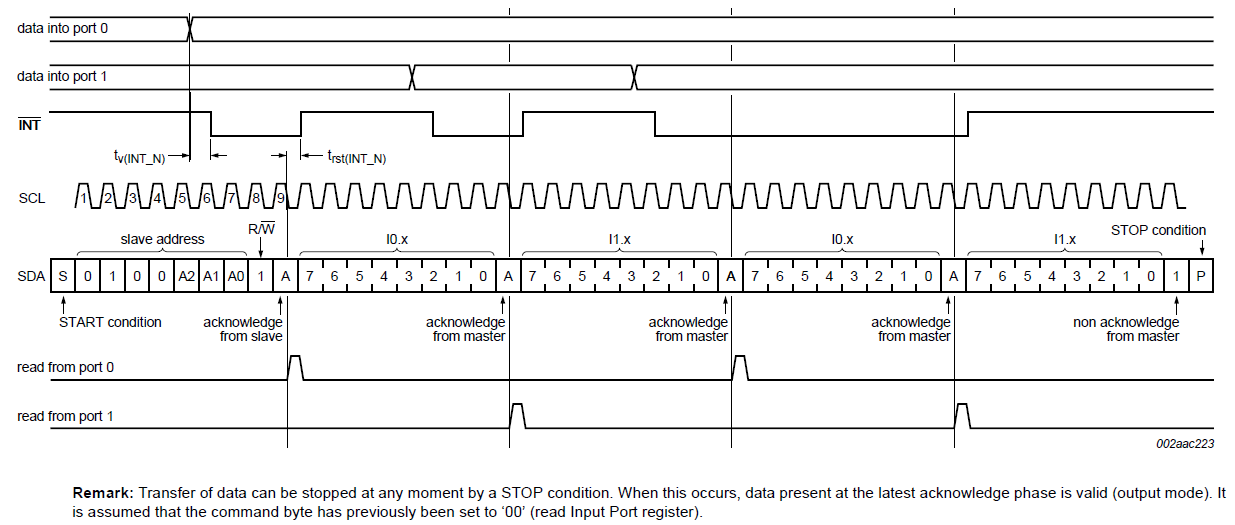

(2)Reading the port registers

In order to read data from the PCA9555, the bus master must first send the PCA9555 address with the least significant bit set to a logic 0 (see Figure 8 “PCA9555 device address”). The command byte is sent after the address and determines which register will be accessed. After a restart, the device address is sent again, but this time the least significant bit is set to a logic 1. Data from the register defined by the command byte will then be sent by the PCA9555 (see Figure 12, Figure 13 and Figure 14). Data is clocked into the register on the falling edge of the acknowledge clock pulse. After the first byte is read, additional bytes may be read but the data will now reflect the information in the other register in the pair. For example, if you read Input Port 1, then the next byte read would be Input Port 0. There is no limitation on the number of data bytes received in one read transmission but the final byte received, the bus master must not acknowledge the data.

Read from register

Read Input port register, scenario 1

2、以上通讯流程中包含的各个信号分解如下:

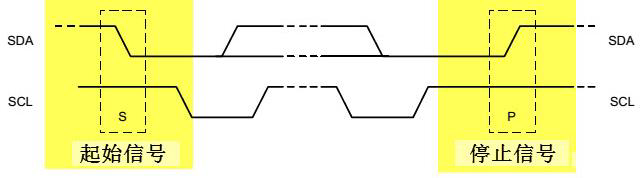

(1)通信的起始和停止信号

起始(S)和停止(P)信号是两种特殊的状态,见下图 。当 SCL 线是高电平时 SDA 线从高电平向低电平切换,这个情况表示通讯的起始。当 SCL 是高电平时 SDA线由低电平向高电平切换,表示通讯的停止。起始和停止信号一般由主机产生。

起始和停止信号

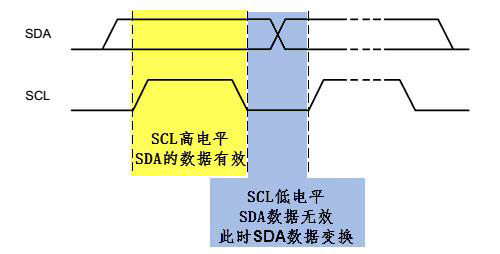

(2)数据的有效性

I2C 使用SDA 信号线来传输数据,使用SCL 信号线进行数据同步。见下图。SDA数据线在SCL 的每个时钟周期传输一位数据。传输时,SCL 为高电平的时候SDA 表示的数据有效,即此时的SDA 为高电平时表示数据“1”,为低电平时表示数据“0”。当SCL为低电平时,SDA 的数据无效,一般在这个时候SDA 进行电平切换,为下一次表示数据做好准备。

数据有效性

注意:每次数据传输都以字节为单位,但是每次传输的字节数不受限制。

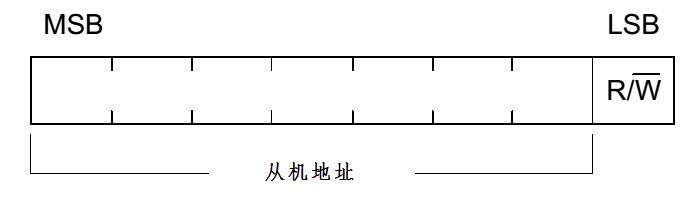

(3)地址及数据方向

I2C 总线上的每个设备都有自己的独立地址,主机发起通讯时,通过SDA 信号线发送设备地址(SLAVE_ADDRESS)来查找从机。I2C 协议规定设备地址可以是7 位或10 位,实际中7 位的地址应用比较广泛。紧跟设备地址的一个数据位用来表示数据传输方向,它是数据方向位(R/W),第8 位或第11 位。数据方向位为“1”时表示主机由从机读数据,该位为“0”时表示主机向从机写数据。

设备地址(7 位)及数据传输方向

对SDA信号线的控制:读数据方向时,主机会释放对SDA 信号线的控制,由从机控制SDA 信号线,主机接收信号,写数据方向时,SDA 由主机控制,从机接收信号。

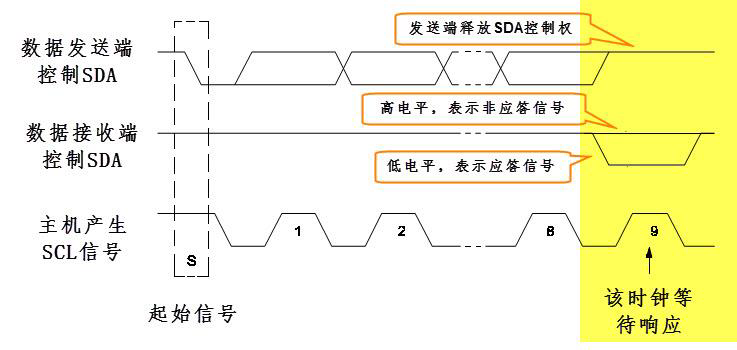

(4)响应

I2C 的数据和地址传输都带响应。响应包括“应答(ACK)”和“非应答(NACK)”两种信号。作为数据接收端时,当设备(无论主从机)接收到I2C 传输的一个字节数据或地址后,若希望对方继续发送数据,则需要向对方发送“应答(ACK)”信号,发送方会继续发送下一个数据;若接收端希望结束数据传输,则向对方发送“非应答(NACK)”信号,发送方接收到该信号后会产生一个停止信号,结束信号传输。见下图。

响应与非响应信号

传输时主机产生时钟,在第9 个时钟时,数据发送端会释放SDA 的控制权,由数据接收端控制SDA,若SDA 为高电平,表示非应答信号(NACK),低电平表示应答信号(ACK)。