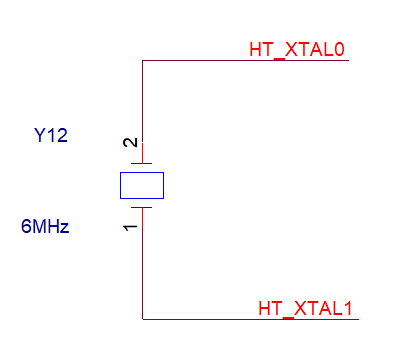

相信大家在不少的电路原理图中都见过晶振电路,其大致形式如下:

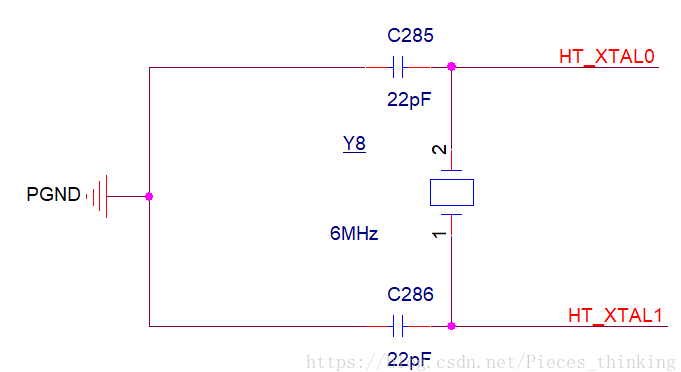

再或者这样:

我记得我第一次看到这样的晶振电路时,产生了很多的疑问,接下来咱们就一个一个的去解决这些疑问。

1、晶振两边的电容可以不要吗?

答案:可以不要。

晶体旁边加的这个电容被我们称之为晶体负载电容。

晶体的谐振频率为Fr,加了电容的谐振频率为有载谐振频率FL。晶体谐振频率Fr与晶体有载谐振频率FL的关系为:

FL=Fr + Ts*CL

式中Ts为晶体的牵引量,单位为ppm/pF。CL为晶体的负载电容,即晶体旁边加的那个电容,单位为pF。

如果电路不加负载电容,则电路会工作在晶体谐振频率上。所以电路中是可以不加负载电容的。

加了负载电容之后有什么好处呢?

首先咱们要明白:晶体发生谐振后,会呈现为纯电阻,即谐振阻抗。

在有载谐振中,谐振电阻一般会与负载电容呈反比例关系。也就是说负载电容越小,电路的谐振阻抗越高,就越不容易起振,输出波形幅度就越小。

好家伙,这不是缺点嘛?怎么是好处??

这就要考虑到工程里的实际应用了。

电路直接工作在晶体谐振频率的状态是非常理想化的。

我们一般的电路都或多或少的有一些杂散电容。当电路振荡时,这些杂散电容便被视为晶体的负载电容进行工作。由于这些杂散电容一般都很小,且不稳定,这就造成晶体振荡频率不稳定,且谐振阻抗增高,“可能工作不稳定,频率不准确”。

明白了吧,其实就是为了防止那些非常小的杂散电容干坏事,所以咱们干脆直接把它位置占了!!!

当然,如果你的振荡电路较为简单,而且PCB走线设计的又十分合理,PCB上的杂散电容小到可以忽略不计且十分稳定,那么就可以不加电容。

负载电容怎么选?

首先,你要明白FL这个有载谐振频率就是你的电路所要的频率。电路中的杂散电容为Cy的话,根据上面的公式,你所设计的电路频率应为:

FL = Fr + Ts*(Cy+CL)

设计时,你的负载电容CL可以用可调电容替代,调整CL值直到电路工作在你所要的频率上。

一般时候这个负载电容CL值不要太小,上面说过电容太小,谐振阻抗会变高,不利于起振且输出幅度小。所以这个电容值一般选取在10至30pF之间。

此时由于负载电容CL值远远大于杂散电容Cy值,因此对杂散电容的不稳定性可以忽略不计。所以加了负载电容的电路会更稳定,频率更准确。

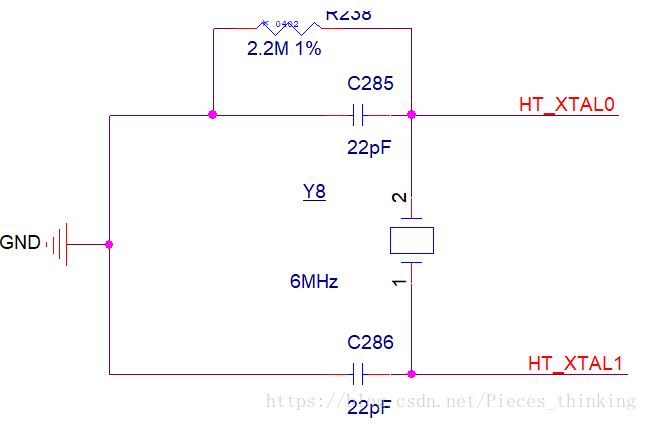

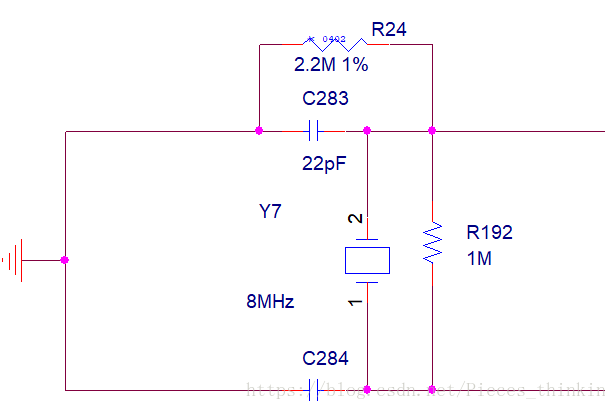

2、并联、串联电阻是干啥的?

先把答案摆出来:

并联电阻的作用:

- 1.降低晶体的Q值,Q值降低后晶体起振比较容易

- 2.抑制EMI,EMI不过时,可减小阻值

- 3.提供直流工作点

- 4.使门电路工作于线性区

串联电阻的作用:

- 1.降低晶体的激励功率,防止损坏。

- 2.限制振荡幅度。

其内部原理,比较复杂,先暂且放下,有机会再接着说~