- AXI(高级可扩展接口),是ARM AMBA的一部分;

- AMBA:高级微控制器总线架构,是1996年首次引进的一组微控制器总线;是一套开放的片内互联的总线标准,能在多主机设计中实现多个控制器和外围设备之间的连接和管理。

- 三种类型AXI4:

- AXI4(-Full):适应于高性能的存储器映射需求(memory-mapped)(主机对从机进行读写操作时,指定一个对应系统存储空间的地址,表示对该空间进行读写操作;即在读写操作时有没有指定地址);应用范围广,支持突发传输一次最大256字。

- AXI4-Lite:简化版接口,用于低吞吐率存储器映射的通,读写带宽小;一般用于对寄存器的读写操作或者配置,支持单字传输,不支持突发传输。

- AXI4-Stream(ST):用于高速的流数据通信(不需要指定地址,不是存储器映射);一般用于传输视频流等,突发长度不受限制。

- 多个AXI主机和从机会被AXI基础结构(infrastructure)IP核连接在一起,AXI Interconnect IP(vivado上点击自动连接)和AXI SmartConnect IP可以被用作多个AXI主从之间的路由。

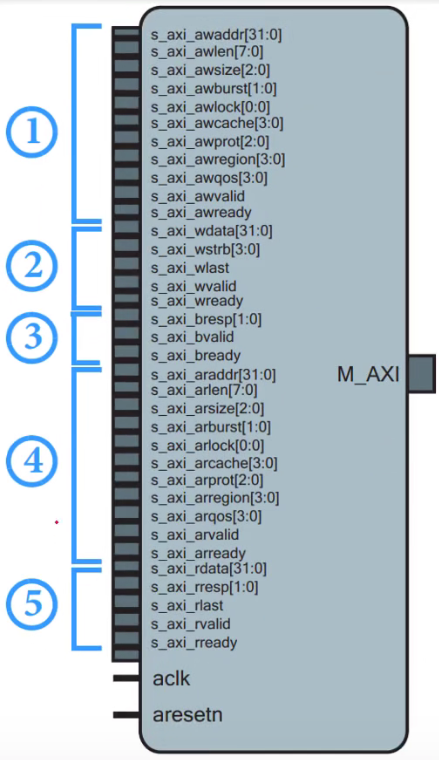

- AXI4和AXI4-Lite都有五个独立的通道(把端口信号分成了五组):

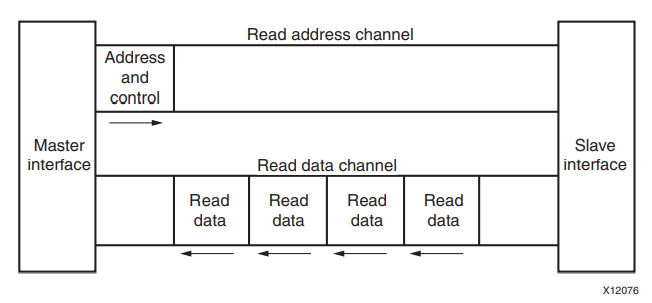

- 读地址通道

- 读数据通道

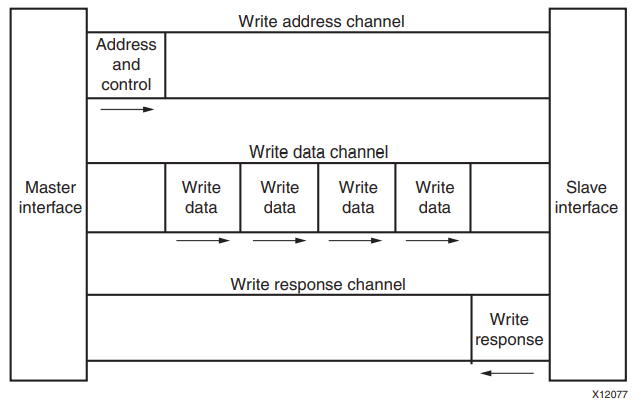

- 写地址通道

- 写数据通道

- 写响应通道

- 读写通道分离,可以同时进行双向传输。

- 也是基于握手机制。

- AXI4-Stream只有一个传输流数据的通道,突发传输单次无上限。

- AXI4-Stream协议:只关心数据流不关心地址。每个AXI4-Stream充当一个单次握手数据流单向的通道。

- Infrastructure IP:是用于搭建系统的构建块。

- AXI Register slices(for pipelining)

- AXI FIFOS(for buffering/clock conversion)

- AXI Interconnect IP and AXI Smart Connect IP(for connecting memory-mapped IP together)

- AXI Direct Memory Access(DMA) engines(存储器数据流与stream数据流的转换)

- AXI Performance Monitors and Protocol Checkers(for analysis and debug)

- AXI Verification IP(for simulation-based verification and performance analysis)

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1

- 1