注:本文档为《从0学x86操作系统》课程配套的学习文档,提供相应的辅助学习资料和答疑勘误。 有关该课程的信息,请点击这里访问:https://study.163.com/provider/1017884735/index.htm 在阅读本文档时,如有疑问和建议,欢迎在下方留言或者直接联系我。

本课时主要介绍8253定时器中断的配置,较多与芯片细节相关的东西。

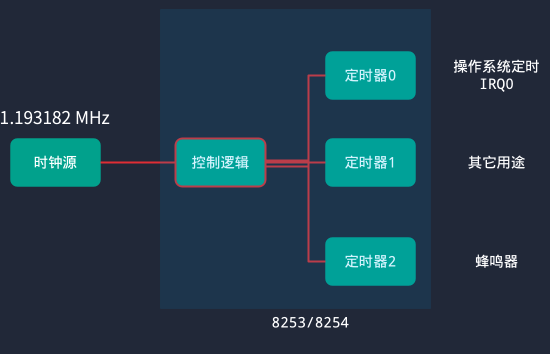

8253整体结构

8253是一颗带有3个内部计数器的定时器的芯片,用于为计算机提供相关的定时和计数功能。其中,我们主要关心定时器/计数器0,因其余两个一般用于其它用途。

定时器0可单独计数,其输入的时钟频率为1.193182 MHz。在每个时钟节拍的作用下,进行递减计数。当减至0时,通过8259的IRQ0向CPU发出中断请求,CPU将进入中断服务程序运行。

为实现对8253进行配置,可通过如下端口进行设置。

端口地址 名称

- 0x40 定时器0数据端口

- 0x41 定时器1数据端口

- 0x42 定时器2数据端口

-

定时器0的配置

在这门课程中,只需要一个可以周期性产生中断的定时器,无需考虑各种硬件方面的东西。因此,只需要将定时器设置成自动周期性触发中断即可,而模式3可以方便的实现此功能,因此选用的模式3。

其它模式较为复杂,有的需要和硬件配合,有的需要在中断中重新配置定时器,所以没有使用这些模式。

(注:无论是手册上还是各种资料上关于工作模式都讲得过细,特别是有些资料还讲了一些8253硬件输出信号的问题。这些与我们的操作系统设计没什么关系,不用看,直接跳过即可。)参考资料

8253数据手册(在课程提供的资料下载中有8259.pdf文档)

- osdev关于8253的文档:https://wiki.osdev.org/Programmable_Interval_Timer

- 另一篇关于8253配置的文档:http://www.osdever.net/bkerndev/Docs/pit.htm

- LINUX内核完全剖析:基于0.12内核 第316页(在课程提供的资料下载中有pdf文档)