注:本文档为《从0学x86操作系统》课程配套的学习文档,提供相应的辅助学习资料和答疑勘误。 有关该课程的信息,请点击这里访问:https://study.163.com/provider/1017884735/index.htm 在阅读本文档时,如有疑问和建议,欢迎在下方留言或者直接联系我。

本课时主要介绍保护模式下的内存管理机制,以分段存储部分介绍为主,分页部分在后面的章节中介绍。

参考文档为《Intel® 64 and IA-32 Architectures Software Developer’s Manual Volume 3 (3A, 3B, 3C & 3D): System Programming Guide》,仅关注其中的第3章。

IA32内存管理机制概览

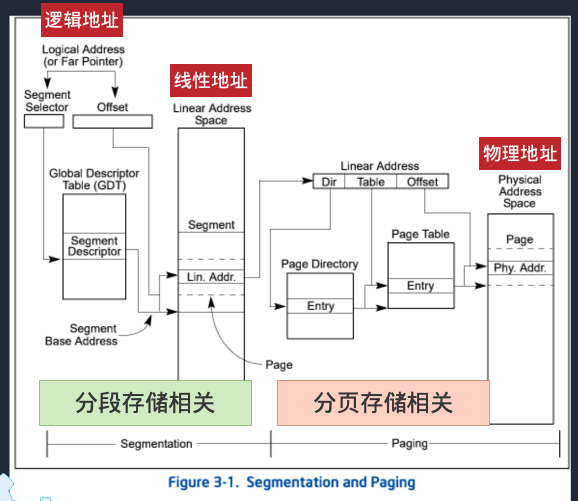

IA32将内存管理分为两部分:段式存储和页式存储,目前我们只考虑了段式存储。由于这种处理,所以得出了三种类型的地址:逻辑地址、线性地址、物理地址。

- 物理地址:实际物理内存中的地址

- 逻辑地址:使用段+偏移表示的地址

- 线性地址:将段+偏移进行转换后的地址,也是我们程序中所用的地址。如果分页机制未开启,则线性地址=物理地址。

(注:以上在操作系统教材中是有相关介绍的,可以参考下这些郝教材)

其中段式存储特点如下:

- 将线性地址空间转变成多个段(segments)

- 每个段带有相关的保护机制

- 有多种类型的段:数据、代码、栈、门、tss

- 使用的地址为逻辑地址,即段选择子+偏移

页式存储的特点如下:

- 将线性地址转换为逻辑地址

- 在较小的内存上实现更大的虚拟内容

- 按需加载等功能

平坦模型

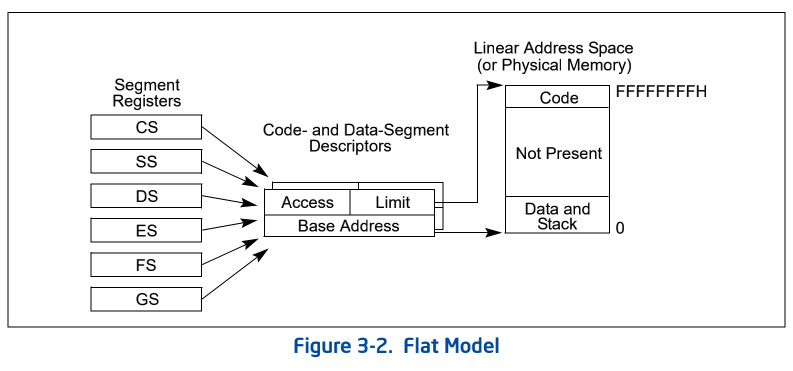

IA32中段式存储比较复杂,我们使用的是基础平坦模型,其特点如下:

- 两个段:代码段和数据段

- 段起始地址均为0,大小为4GB。即不管有没有那么大空间,都可访问,访问结果未知。

即采用上述模型中,我们不使用limit界限检查,也不使用段的基地址功能,这样程序处理会更为简单。

(注:最终我们的系统采用的模型和上述略有些不同,这在以后会再提及)

逻辑地址到线性地址的转换

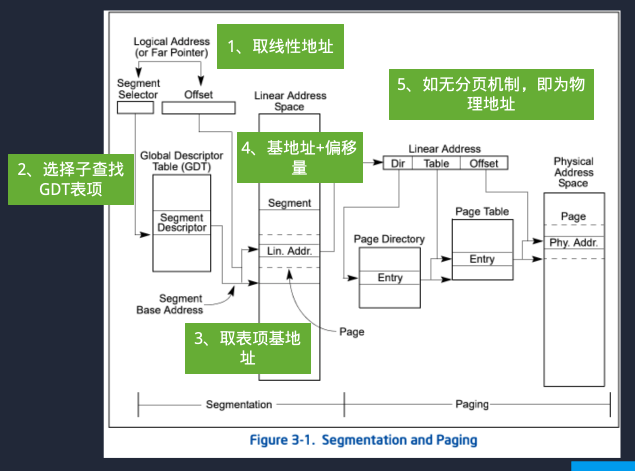

在程序进行内存访问时,会进行逻辑地址的转换,转换到线性地址(暂不考虑分页机制),转换过程如下:

参考资料

- 课程附带的intel编程文档卷3:Intel® 64 and IA-32 Architectures Software Developer’s Manual Volume 3 (3A, 3B, 3C & 3D): System Programming Guide