3月22日课上代码

module CJHYYDS();// reg 为输入的端口// wire 为输出的接口// 待解决的问题: [7:0] 是什么意思// 已解决:[7:0] 的意思是该接口具有八个比特的位宽,在一般情况下我们只用一个比特的位宽已足够。wire A;wire [7:0]B;wire [7:0]C;wire [7:0]D;wire [7:0]EX;reg ST;reg i0;reg i1;reg i10;reg i11;reg i12;reg i13;reg i14;reg i15;reg i2;reg i3;reg i4;reg i5;reg i6;reg i7;reg i8;reg i9;initialbegini15=1;i14=1;i13=0;i12=0;i11=1;i10=0;i9=0;i8=1;i7=1;i6=0;i5=1;i4=1;i3=0;i2=1;i1=1;i0=0;#50;i15=1;i14=1;i13=1;i12=1;i11=1;i10=1;i9=1;i8=1;i7=1;i6=0;i5=1;i4=1;i3=0;i2=1;i1=1;i0=0;end//下面的代码为对模拟的接口进行索引调用// .name(new_name)design_1_wrapper cjh(.A(A),.B(B),.C(C),.D(D),.EX(EX),.ST(ST),.i0(i0),.i1(i1),.i10(i10),.i11(i11),.i12(i12),.i13(i13),.i14(i14),.i15(i15),.i2(i2),.i3(i3),.i4(i4),.i5(i5),.i6(i6),.i7(i7),.i8(i8),.i9(i9));endmodule

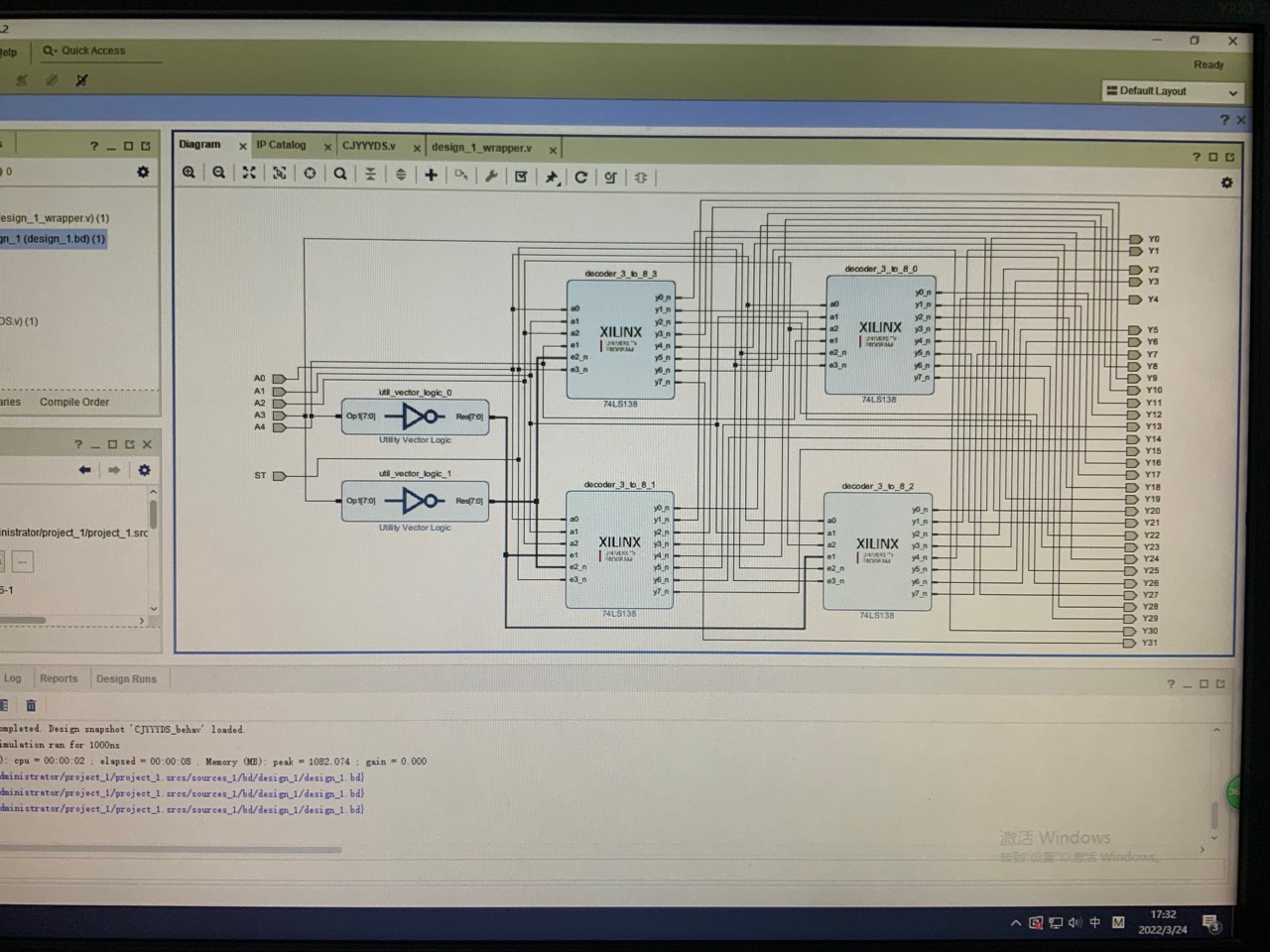

3月24日课上代码

module CJYYYDS();reg A0;reg A1;reg A2;reg A3;reg A4;reg ST;wire Y0;wire Y1;wire Y10;wire Y11;wire Y12;wire Y13;wire Y14;wire Y15;wire Y16;wire Y17;wire Y18;wire Y19;wire Y2;wire Y20;wire Y21;wire Y22;wire Y23;wire Y24;wire Y25;wire Y26;wire Y27;wire Y28;wire Y29;wire Y3;wire Y30;wire Y31;wire Y4;wire Y5;wire Y6;wire Y7;wire Y8;wire Y9;initialbeginA0=0;A1=0;A2=0;A3=0;A4=0;ST=0;#30;A0=1;A1=0;A2=0;A3=0;A4=0;ST=0;#30;A0=0;A1=1;A2=0;A3=0;A4=0;ST=0;#30;A0=1;A1=1;A2=0;A3=0;A4=0;ST=0;#30;A0=0;A1=0;A2=1;A3=0;A4=0;ST=0;#30;A0=1;A1=1;A2=1;A3=0;A4=0;ST=0;#30;A0=0;A1=0;A2=0;A3=1;A4=0;ST=0;#30;A0=1;A1=0;A2=0;A3=1;A4=0;ST=0;#30;A0=0;A1=1;A2=0;A3=1;A4=0;ST=0;#30;A0=1;A1=1;A2=0;A3=1;A4=0;ST=0;#30;A0=0;A1=0;A2=1;A3=1;A4=0;ST=0;#30;A0=1;A1=0;A2=1;A3=1;A4=0;ST=0;#30;A0=0;A1=1;A2=1;A3=1;A4=0;ST=0;#30;A0=1;A1=1;A2=1;A3=1;A4=0;ST=0;#30;A0=0;A1=0;A2=0;A3=0;A4=1;ST=0;#30;A0=1;A1=0;A2=0;A3=0;A4=1;ST=0;#30;A0=0;A1=1;A2=0;A3=0;A4=1;ST=0;#30;A0=1;A1=1;A2=0;A3=0;A4=1;ST=0;#30;A0=0;A1=0;A2=1;A3=0;A4=1;ST=0;#30;A0=1;A1=0;A2=1;A3=0;A4=1;ST=0;#30;A0=0;A1=1;A2=1;A3=0;A4=1;ST=0;#30;A0=1;A1=1;A2=1;A3=0;A4=1;ST=0;#30;A0=0;A1=0;A2=0;A3=1;A4=1;ST=0;#30;A0=1;A1=0;A2=0;A3=1;A4=1;ST=0;#30;A0=0;A1=1;A2=0;A3=1;A4=1;ST=0;#30;A0=1;A1=1;A2=0;A3=1;A4=1;ST=0;#30;A0=0;A1=0;A2=1;A3=1;A4=1;ST=0;#30;A0=1;A1=0;A2=1;A3=1;A4=1;ST=0;#30;A0=0;A1=1;A2=1;A3=1;A4=1;ST=0;#30;A0=1;A1=1;A2=1;A3=1;A4=1;ST=0;#30;enddesign_1_wrapper cjh(.A0(A0),.A1(A1),.A2(A2),.A3(A3),.A4(A4),.ST(ST),.Y0(Y0),.Y1(Y1),.Y2(Y2),.Y3(Y3),.Y4(Y4),.Y5(Y5),.Y6(Y6),.Y7(Y7),.Y8(Y8),.Y9(Y9));.Y10(Y10),.Y11(Y11),.Y12(Y12),.Y13(Y13),.Y14(Y14),.Y15(Y15),.Y16(Y16),.Y17(Y17),.Y18(Y18),.Y19(Y19),.Y20(Y20),.Y21(Y21),.Y22(Y22),.Y23(Y23),.Y24(Y24),.Y25(Y25),.Y26(Y26),.Y27(Y27),.Y28(Y28),.Y29(Y29),.Y30(Y30),.Y31(Y31),endmodule

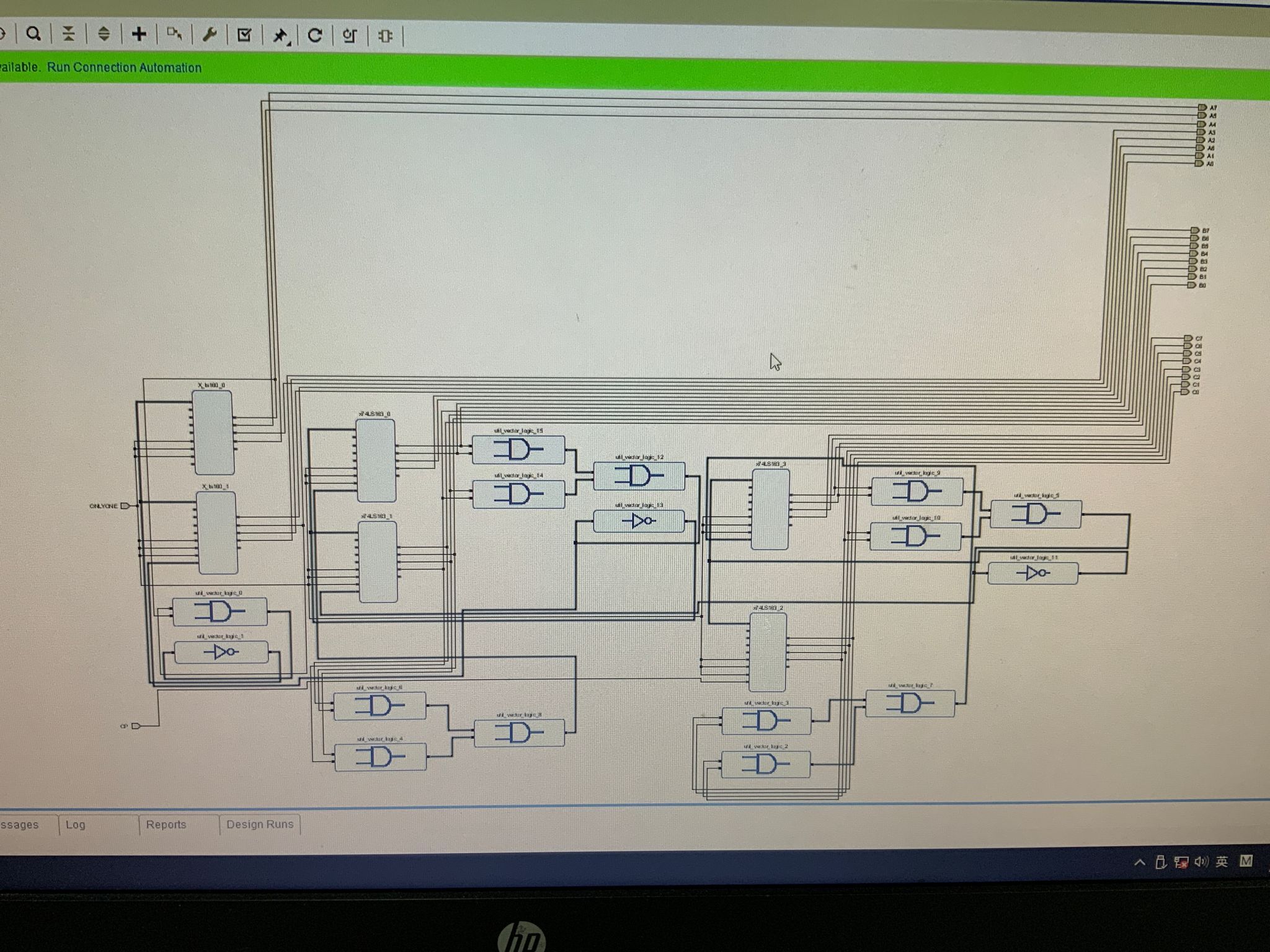

4月7日工程文件

工程说明:本工程仍存在问题,尚未解决74163的进位问题,仅供参考!!! 希望实现使用74160和74163两个模组实现时分秒的时钟,时针模12,分针秒针模60.

`timescale 1ns / 1ps

module CJHZLJ();

reg ONLYONE=1;//此处的ONLYONE变量是用于控制所有的时序器件的正常使用

reg CP = 0;//用于产生时钟信号

//此处为时针对应的八位二进制编码

wire A0;

wire A1;

wire A2;

wire A3;

wire A4;

wire A5;

wire A6;

wire A7;

//此处为分针对应的八位二进制编码

wire B0;

wire B1;

wire B2;

wire B3;

wire B4;

wire B5;

wire B6;

wire B7;

//此处为秒针对应的八位二进制编码

wire C0;

wire C1;

wire C2;

wire C3;

wire C4;

wire C5;

wire C6;

wire C7;

//此代码使得CP每两毫秒产生一次反转

always #2 CP=~CP;

//下列代码为向模拟系统的接口重设名字

design_1_wrapper cjh

(.A0(A0),

.A1(A1),

.A2(A2),

.A3(A3),

.A4(A4),

.A5(A5),

.A6(A6),

.A7(A7),

.B0(B0),

.B1(B1),

.B2(B2),

.B3(B3),

.B4(B4),

.B5(B5),

.B6(B6),

.B7(B7),

.C0(C0),

.C1(C1),

.C2(C2),

.C3(C3),

.C4(C4),

.C5(C5),

.C6(C6),

.C7(C7),

.CP(CP),

.ONLYONE(ONLYONE));

endmodule

连接示例:

以上连接方式仍存在一些小问题,亟待更正,随缘更新。